### **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35. An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### **COURSE NAME : 19CSB201 – OPERATING SYSTEMS**

**II YEAR/ IV SEMESTER**

UNIT – V I/O Systems

**Topic: I/O Systems: I/O Hardware**

Mrs. M. Lavanya Assistant Professor Department of Computer Science and Engineering

- Overview

- I/O Hardware

- Application I/O Interface

- Kernel I/O Subsystem

- Transforming I/O Requests to Hardware Operations

- STREAMS

- Performance

- Explore the structure of an operating system's I/O subsystem

- Discuss the principles of I/O hardware and its complexity

- Provide details of the performance aspects of I/O hardware and software

- I/O management is a major component of operating system design and operation

- Important aspect of computer operation

- I/O devices vary greatly

- Various methods to control them

- Performance management

- New types of devices frequent

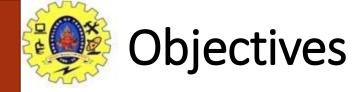

- Ports, busses, device controllers connect to various devices

- **Device drivers** encapsulate device details

- Present uniform device-access interface to I/O subsystem

## I/O Hardware

- Incredible variety of I/O devices

- Storage

- Transmission

- Human-interface

- Common concepts signals from I/O devices interface with computer

- **Port** connection point for device

- Bus daisy chain or shared direct access

- PCI bus common in PCs and servers, PCI Express (PCIe)

- expansion bus connects relatively slow devices

- Controller (host adapter) electronics that operate port, bus, device

- Sometimes integrated

- Sometimes separate circuit board (host adapter)

- Contains processor, microcode, private memory, bus controller, etc

- Some talk to per-device controller with bus controller, microcode, memory, etc

## A Typical PC Bus Structure

19CSB201 – Operating Systems/ Unit-V/I/O Systems: I/O Hardware / Mrs.M.Lavanya/AP/CSE/SNSCT

# I/O Hardware (Cont.)

- I/O instructions control devices

- Devices usually have registers where device driver places commands, addresses, and data to write, or read data from registers after command execution

- Data-in register, data-out register, status register, control register

- Typically 1-4 bytes, or FIFO buffer

- Devices have addresses, used by

- Direct I/O instructions

- Memory-mapped I/O

- Device data and command registers mapped to processor address space

- Especially for large address spaces (graphics)

### Device I/O Port Locations on PCs (partial)

| I/O address range (hexadecimal) | device                    |

|---------------------------------|---------------------------|

| 000-00F                         | DMA controller            |

| 020-021                         | interrupt controller      |

| 040–043                         | timer                     |

| 200–20F                         | game controller           |

| 2F8-2FF                         | serial port (secondary)   |

| 320–32F                         | hard-disk controller      |

| 378–37F                         | parallel port             |

| 3D0-3DF                         | graphics controller       |

| 3F0–3F7                         | diskette-drive controller |

| 3F8–3FF                         | serial port (primary)     |

#### ■ For each byte of I/O

- 1. Read busy bit from status register until 0

- 2. Host sets read or write bit and if write copies data into data-out register

- 3. Host sets command-ready bit

- 4. Controller sets busy bit, executes transfer

- 5. Controller clears busy bit, error bit, command-ready bit when transfer done

- Step 1 is **busy-wait** cycle to wait for I/O from device

- Reasonable if device is fast

- But inefficient if device slow

- CPU switches to other tasks?

- But if miss a cycle data overwritten / lost

- Polling can happen in 3 instruction cycles

- Read status, logical-and to extract status bit, branch if not zero

- How to be more efficient if non-zero infrequently?

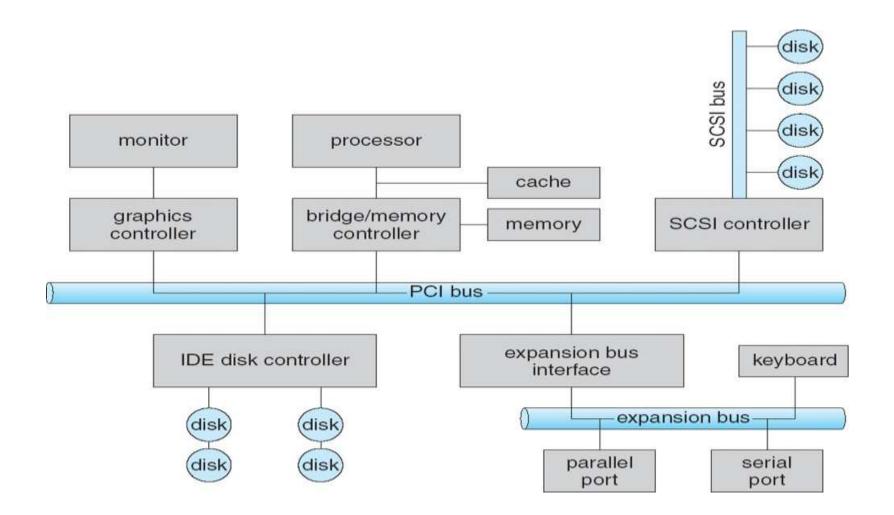

- CPU Interrupt-request line triggered by I/O device

- Checked by processor after each instruction

- Interrupt handler receives interrupts

- Maskable to ignore or delay some interrupts

- Interrupt vector to dispatch interrupt to correct handler

- Context switch at start and end

- Based on priority

- Some nonmaskable

- Interrupt chaining if more than one device at same interrupt number

# Interrupt-Driven I/O Cycle

19CSB201 – Operating Systems/ Unit-V/I/O Systems: I/O Hardware / Mrs.M.Lavanya/AP/CSE/SNSCT

#### Intel Pentium Processor Event-Vector Table

| vector number | description                            |

|---------------|----------------------------------------|

| 0             | divide error                           |

| 1             | debug exception                        |

| 2             | null interrupt                         |

| 3             | breakpoint                             |

| 4             | INTO-detected overflow                 |

| 5             | bound range exception                  |

| 6             | invalid opcode                         |

| 7             | device not available                   |

| 8             | double fault                           |

| 9             | coprocessor segment overrun (reserved) |

| 10            | invalid task state segment             |

| 11            | segment not present                    |

| 12            | stack fault                            |

| 13            | general protection                     |

| 14            | page fault                             |

| 15            | (Intel reserved, do not use)           |

| 16            | floating-point error                   |

| 17            | alignment check                        |

| 18            | machine check                          |

| 19–31         | (Intel reserved, do not use)           |

| 32–255        | maskable interrupts                    |

# Interrupts (Cont.)

- Interrupt mechanism also used for exceptions

- Terminate process, crash system due to hardware error

- Page fault executes when memory access error

- System call executes via trap to trigger kernel to execute request

- Multi-CPU systems can process interrupts concurrently

- If operating system designed to handle it

- Used for time-sensitive processing, frequent, must be fast

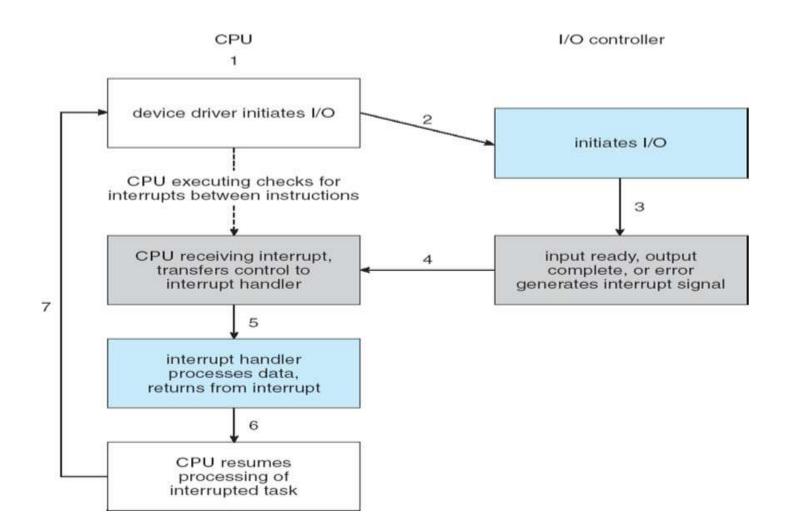

## **Direct Memory Access**

- Used to avoid programmed I/O (one byte at a time) for large data movement

- Requires **DMA** controller

- Bypasses CPU to transfer data directly between I/O device and memory

- OS writes DMA command block into memory

- Source and destination addresses

- Read or write mode

- Count of bytes

- Writes location of command block to DMA controller

- Bus mastering of DMA controller grabs bus from CPU

- Cycle stealing from CPU but still much more efficient

- When done, interrupts to signal completion

- Version that is aware of virtual addresses can be even more efficient -DVMA

#### Six Step Process to Perform DMA Transfer

19CSB201 – Operating Systems/ Unit-V/I/O Systems: I/O Hardware / Mrs.M.Lavanya/AP/CSE/SNSCT

#### **TEXT BOOKS:**

- T1 Silberschatz, Galvin, and Gagne, "Operating System Concepts", Ninth Edition, Wiley India Pvt Ltd, 2009.)

- T2. Andrew S. Tanenbaum, "Modern Operating Systems", Fourth Edition, Pearson Education, 2010

#### **REFERENCES:**

- R1 Gary Nutt, "Operating Systems", Third Edition, Pearson Education, 2004.

- R2 Harvey M. Deitel, "Operating Systems", Third Edition, Pearson Education, 2004.

- R3 Abraham Silberschatz, Peter Baer Galvin and Greg Gagne, "Operating System Concepts", 9th Edition, John Wiley and Sons Inc., 2012.

- R4. William Stallings, "Operating Systems Internals and Design Principles", 7th Edition, Prentice Hall, 2011