### **SNS COLLEGE OF TECHNOLOGY** An Autonomous Institution Coimbatore-35

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

### **DEPARTMENT OF ELECTRONICS & COMMUNICATION**

### MICROPROCESSORS AND MICROCONTROLLERS ENGINEERING

II YEAR/ IV SEMESTER

### UNIT 1 – 8085 AND 8086 ARCHITECTURE

TOPIC – Memory and I/O Interfacing of 8086

#### 8086 Microprocessor

- Registers inside a microcomputer

- Store data and results temporarily

- No speed disparity

- Cost ↑

#### <sup>7</sup> Primary or Main Memory

- Storage area which can be directly accessed by microprocessor

- Store programs and data prior to execution

- Should not have speed disparity with processor ⇒ Semi Conductor memories using CMOS technology

- ROM, EPROM, Static RAM, DRAM

#### **Secondary Memory**

- Storage media comprising of slow devices such as magnetic tapes and disks

- Hold large data files and programs: Operating system, compilers, databases, permanent programs etc.

#### Memory

Store Programs and Data

### Memory organization in 8086

- Memory IC's : Byte oriented

- **8086 : 16-bit**

- Word : Stored by two consecutive memory locations; for LSB and MSB

- Address of word : Address of LSB

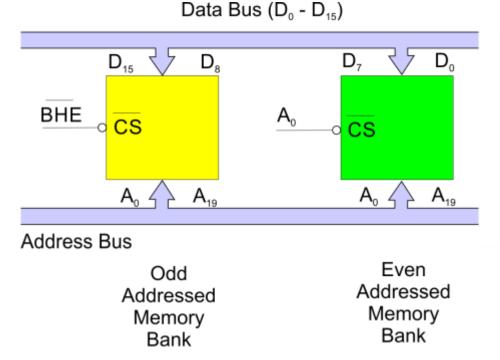

- Bank 0 : A<sub>0</sub> = 0 ⇒ Even addressed memory bank

**Bank 1** :  $\overline{BHE}$  = 0  $\Rightarrow$  Odd addressed memory bank

|   | Memory or data Bus<br>D <sub>15</sub> O BHE<br>BHE<br>CS<br>A <sub>0</sub> A <sub>19</sub> |                                                   | $\frac{P_{i}P_{j}}{P_{i}} \xrightarrow{P_{i}} D_{i}$ $\frac{P_{i}P_{j}}{P_{i}} \xrightarrow{P_{i}} D_{i}$ $\frac{P_{i}P_{j}}{P_{i}} \xrightarrow{P_{i}} D_{i}$ $\frac{P_{i}P_{j}}{P_{i}} \xrightarrow{P_{i}} D_{i}$ |                                    | r in 8086                                                           |

|---|--------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------|

|   |                                                                                            | Address Bus<br>Odd<br>Addressed<br>Memory<br>Bank |                                                                                                                                                                                                                     | Even<br>ddressed<br>Memory<br>Bank |                                                                     |

|   | Operation                                                                                  |                                                   | BHE                                                                                                                                                                                                                 | A <sub>0</sub>                     | Data Lines Used                                                     |

| 1 | Read/ Write byte at an even address                                                        |                                                   | 1                                                                                                                                                                                                                   | 0                                  | $D_{7} - D_{0}$                                                     |

| 2 | Read/ Write byte at an odd address                                                         |                                                   | 0                                                                                                                                                                                                                   | 1                                  | $D_{15} - D_8$                                                      |

| 3 | Read/ Write word at an even address                                                        |                                                   | 0                                                                                                                                                                                                                   | 0                                  | $D_{15} - D_0$                                                      |

| 4 | Read/ Write word at an o                                                                   | odd address                                       | 0                                                                                                                                                                                                                   | 1                                  | $D_{15} - D_0$ in first operation byte from odd bank is transferred |

|   |                                                                                            |                                                   | 1                                                                                                                                                                                                                   | 0                                  | $D_7 - D_0$ in first operation byte from odd bank is transferred    |

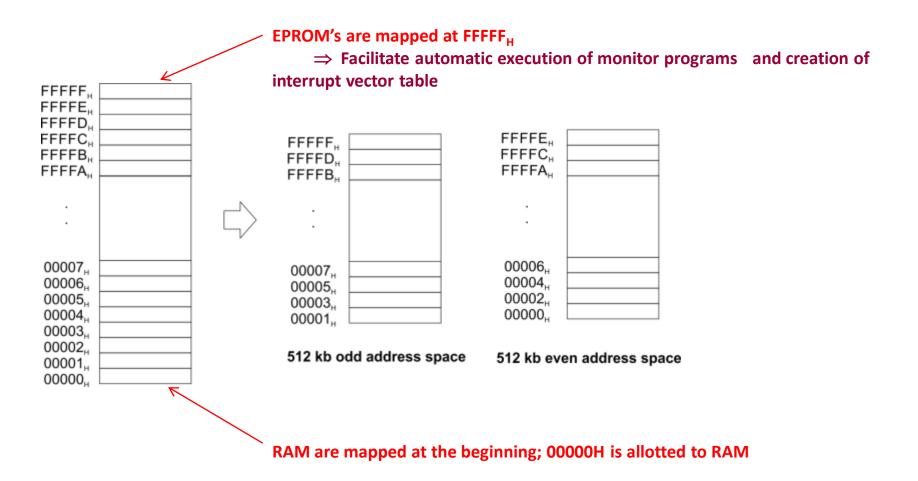

### Memory organization in 8086

- Available memory space = EPROM + RAM

- Allot equal address space in odd and even bank for both EPROM and RAM

- Can be implemented in two IC's (one for even and other for odd) or in multiple IC's

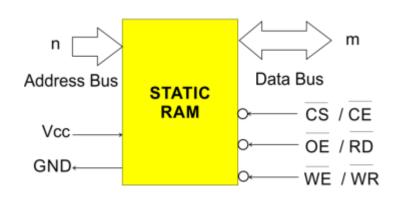

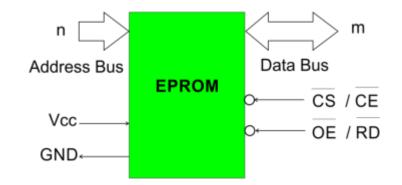

### Interfacing SRAM and EPROM

- Memory interface ⇒ Read from and write in to a set of semiconductor memory IC chip

- EPROM ⇒ Read operations

- RAM ⇒ Read and Write

In order to perform read/ write operations,

- Memory access time < read / write time of the processor</p>

- Chip Select (CS) signal has to be generated

- Control signals for read / write operations

- Allot address for each memory location

## Interfacing SRAM and EPROM

| No of<br>Address pins |                             | Range of address<br>in hexa |         |                      |

|-----------------------|-----------------------------|-----------------------------|---------|----------------------|

|                       | In Decimal                  | In kilo                     | In hexa |                      |

| 20                    | 2 <sup>20</sup> = 10,48,576 | 1024 k = 1M                 | 100000  | 00000<br>to<br>FFFFF |

# Interfacing SRAM and EPROM

### Interfacing SRAM and EPROM

#### **Monitor Programs**

- $\Rightarrow$  Programing 8279 for keyboard scanning and display refreshing

- ⇒ Programming peripheral IC's 8259, 8257, 8255, 8251, 8254 etc

- $\Rightarrow$  Initialization of stack

- $\Rightarrow$  Display a message on display (output)

- $\Rightarrow$  Initializing interrupt vector table

| Note : | 8279 | Programmable keyboard/ display controller |

|--------|------|-------------------------------------------|

|        | 8257 | DMA controller                            |

|        | 8259 | Programmable interrupt controller         |

|        | 8255 | Programmable peripheral interface         |

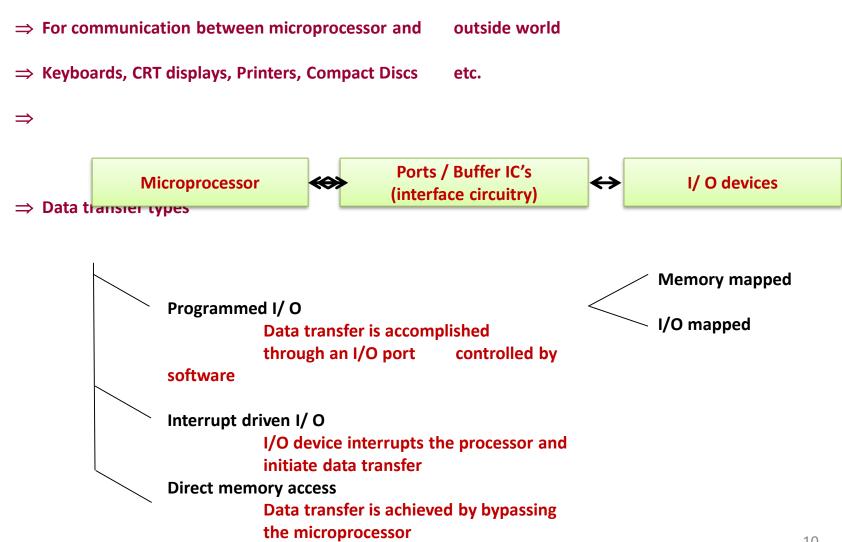

### Interfacing I/O and peripheral devices I/O devices

### 8086 and 8085 comparison

| Memory mapping                                                                                                                                                                          | I/O mapping                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 20 bit address are provided for I/O devices                                                                                                                                             | 8-bit or 16-bit addresses are provided for I/O devices                                         |

| The I/O ports or peripherals can be treated like<br>memory locations and so all instructions related<br>to memory can be used for data transmission<br>between I/O device and processor | Only IN and OUT instructions can be used for data<br>transfer between I/O device and processor |

| Data can be moved from any register to ports and vice versa                                                                                                                             | Data transfer takes place only between accumulator and ports                                   |

| When memory mapping is used for I/O devices,<br>full memory address space cannot be used for<br>addressing memory.                                                                      | Full memory space can be used for addressing memory.                                           |

| ⇒ Useful only for small systems where memory requirement is less                                                                                                                        | $\Rightarrow$ Suitable for systems which require large memory capacity                         |

| For accessing the memory mapped devices, the processor executes memory read or write cycle.                                                                                             | For accessing the I/O mapped devices, the processor executes I/O read or write cycle.          |

| $\Rightarrow$ M / $\overline{10}$ is asserted high                                                                                                                                      | $\Rightarrow$ M / $\overline{IO}$ is asserted low                                              |

# THANK YOU