## **SNS COLLEGE OF TECHNOLOGY**

## An Autonomous Institution Coimbatore-35

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING MICROPROCESSORS AND MICROCONTROLLERS

II YEAR/ IV SEMESTER

**UNIT 1 - 8085 AND 8086 ARCHITECTURE**

TOPIC – Instruction set of 8085

## Branching Instructions:

The branching instruction alter the normal sequential flow.

These instructions alter either unconditionally or conditionally.

| Opcode | Operand        | Description          |

|--------|----------------|----------------------|

| JMP    | 16-bit address | Jump unconditionally |

|        |                |                      |

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand.

Example: JMP 2034 H.

| Opcode | Operand        | Description        |

|--------|----------------|--------------------|

| Jx     | 16-bit address | Jump conditionally |

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW.

Example: JZ 2034 H.

| Opcode | Description         | Status Flags |

|--------|---------------------|--------------|

| JC     | Jump if Carry       | CY = 1       |

| JNC    | Jump if No Carry    | CY = 0       |

| JP     | Jump if Positive    | S = 0        |

| JM     | Jump if Minus       | S = 1        |

| JZ     | Jump if Zero        | Z = 1        |

| JNZ    | Jump if No Zero     | Z = 0        |

| JPE    | Jump if Parity Even | P = 1        |

| JPO    | Jump if Parity Odd  | P = 0        |

| Opcode | Operand        | Description          |

|--------|----------------|----------------------|

| CALL   | 16-bit address | Call unconditionally |

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand.

Before the transfer, the address of the next instruction after CALL (the contents of the program counter) is pushed onto the stack.

Example: CALL 2034 H.

| Opcode | Description         | Status Flags |

|--------|---------------------|--------------|

| CC     | Call if Carry       | CY = 1       |

| CNC    | Call if No Carry    | CY = 0       |

| СР     | Call if Positive    | S = 0        |

| CM     | Call if Minus       | S = 1        |

| CZ     | Call if Zero        | Z = 1        |

| CNZ    | Call if No Zero     | Z = 0        |

| CPE    | Call if Parity Even | P = 1        |

| СРО    | Call if Parity Odd  | P = 0        |

| Opcode | Description           | Status Flags |

|--------|-----------------------|--------------|

| RC     | Return if Carry       | CY = 1       |

| RNC    | Return if No Carry    | CY = 0       |

| RP     | Return if Positive    | S = 0        |

| RM     | Return if Minus       | S = 1        |

| RZ     | Return if Zero        | Z = 1        |

| RNZ    | Return if No Zero     | Z = 0        |

| RPE    | Return if Parity Even | P = 1        |

| RPO    | Return if Parity Odd  | P = 0        |

The control instructions control the operation of microprocessor.

No operation is performed.

The instruction is fetched and decoded but no operation is executed.

Example: NOP

| Opcode | Operand | Description  |

|--------|---------|--------------|

| NOP    | None    | No operation |

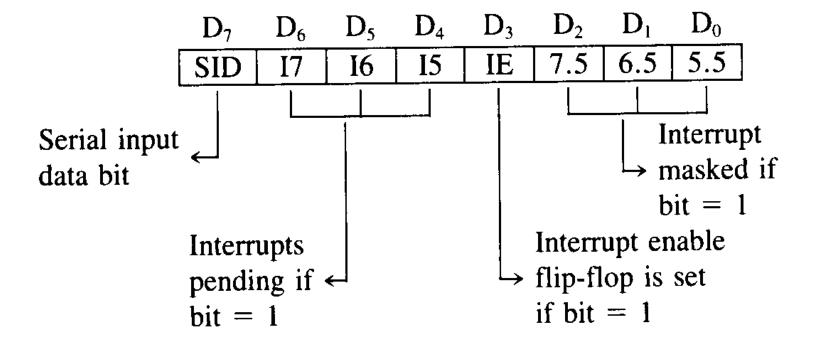

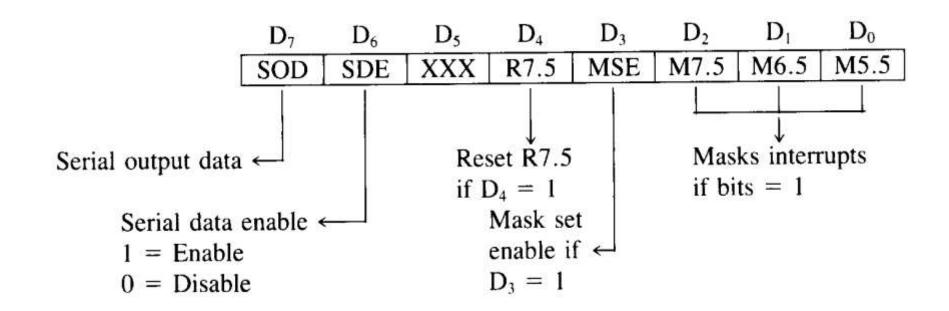

## RIM AND SIM

## THANK YOU