### **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

19ECT312 – EMBEDDED SYSTEM DESIGN

SPI /19ECT312/Embedded systems Design / Mrs.E.Ramya/AP/ECE/SNSCT III YEAR/ VI SEMESTER

**UNIT 2: DEVICES AND EMERGING BUS STANDARDS**

**TOPIC: Communication from serial devices-SPI**

1/22/2024

### Outline

- Introduction to Serial Buses

- UART

- SPI

- 12C

### SPI

### Introduction

- What is it?

- Basic Serial Peripheral Interface (SPI)

- Capabilities

- Protocol

- Pro / Cons and Competitor

- Uses

- Conclusion

### **SPI**

#### What is SPI?

- Serial Bus protocol

- Fast, Easy to use, Simple

- Everyone supports it

### SPI

### **SPI Basics**

- A communication protocol using 4 wires

- Also known as a 4 wire bus

- Used to communicate across small distances

- Multiple Slaves, Single Master

- Synchronized

### **SPI**

### Capabilities of SPI

- Always Full Duplex

- Communicating in two directions at the same time

- Transmission need not be meaningful

- Multiple Mbps transmission speed

- Transfers data in 4 to 16 bit characters

- Multiple slaves

- Daisy-chaining possible

### SPI

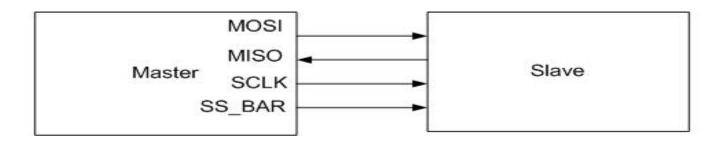

### **Protocol**

- Wires:

- Master Out Slave In (MOSI)

- Master In Slave Out (MISO)

- System Clock (SCLK)

- Slave Select 1...N

- Master Set Slave Select low

- Master Generates Clock

- Shift registers shift in and out data

### **SPI**

#### Wires in Detail

- MOSI Carries data out of Master to Slave

- MISO Carries data from Slave to Master

- Both signals happen for every transmission

- SS\_BAR Unique line to select a slave

- SCLK Master produced clock to synchronize data transfer

### SPI

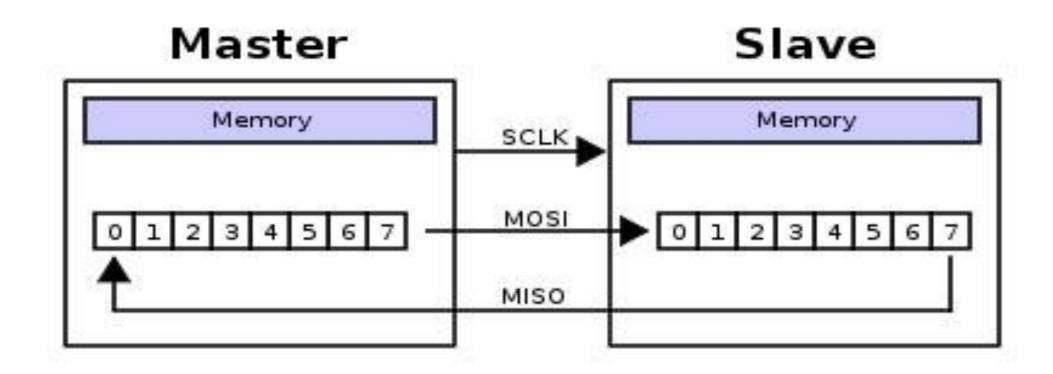

### Shifting Protocol

Master shifts out data to Slave, and shift in data from Slave http://upload.wikimedia.org/wikipedia/commons/thumb/b/bb/SPI\_8-bit\_circular\_transfer.svg/400px-SPI\_8-bit\_circular\_transfer.svg.png

### SPI

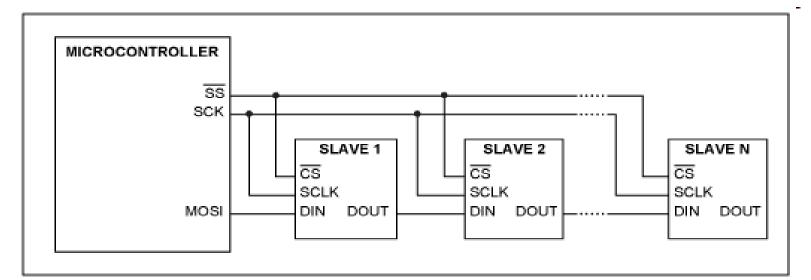

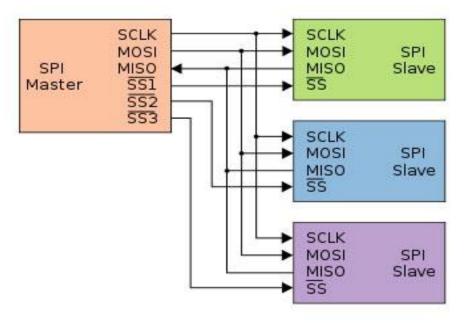

# Diagram

Some wires have been renamed

Master and multiple daisy-chained slaves http://www.maxim-ic.com/appnotes.cfm/an\_pk/3947

Master and multiple independent slaves http://upload.wikimedia.org/wikipedia/commons/thumb/f/fc/SPI\_three\_slaves.svg/350px-SPI\_three\_slaves.svg.png

### SPI

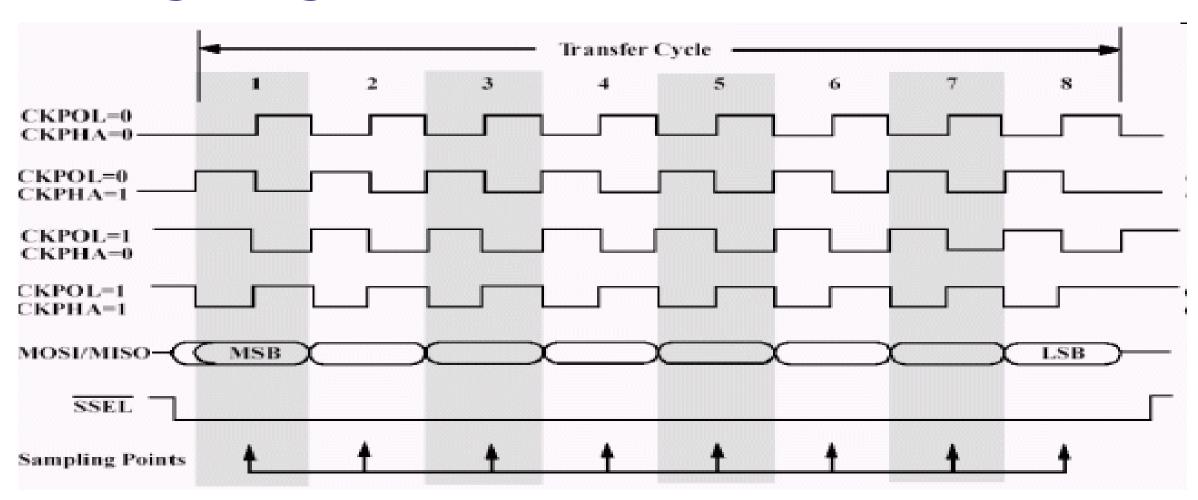

## Clock Phase (Advanced)

- Two phases and two polarities of clock

- Four modes

- Master and selected slave must be in same mode

- Master must change polarity and phase to communicate with slaves of different numbers

### SPI

# Timing Diagram

Timing Diagram – Showing Clock polarities and phases http://www.maxim-ic.com.cn/images/appnotes/3078/3078Fig02.gif

### SPI

#### **Pros and Cons**

#### Pros:

- Fast and easy

- Fast for point-to-point connections

- Easily allows streaming/Constant data inflow

- No addressing/Simple to implement

- Everyone supports it

#### Cons:

- SS makes multiple slaves very complicated

- No acknowledgement ability

- No inherent arbitration

- No flow control

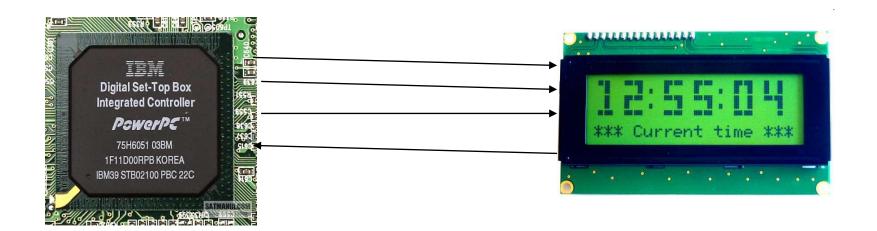

#### Uses

- Some Serial Encoders/Decoders, Converters, Serial LCDs, Sensors, etc.

- Pre-SPI serial devices

### SPI

### Summary

- SPI 4 wire serial bus protocol

- MOSI MISO SS SCLK wires

- Full duplex

- Multiple slaves, One master

- Best for point-to-point streaming data

- Easily Supported

### **SUMMARY & THANK YOU**