# **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

#### 19ECT312 – EMBEDDED SYSTEM DESIGN

Introduction to embedded system Design /19ECT312/Embedded systems Design / III YEAR/ VI SEMESTER

UNIT 1 – INTRODUCTION TO EMBEDDED SYSTEMS

TOPIC 1.1 & 1.2 -INTRODUCTION TO EMBEDDED SYSTEMS, STRUCTURAL UNITS IN A EMBEDDED PROCESSOR

1/22/2024

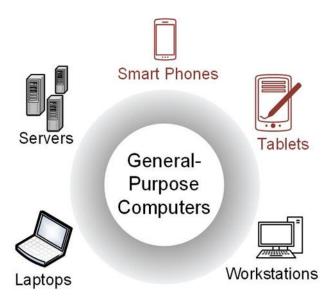

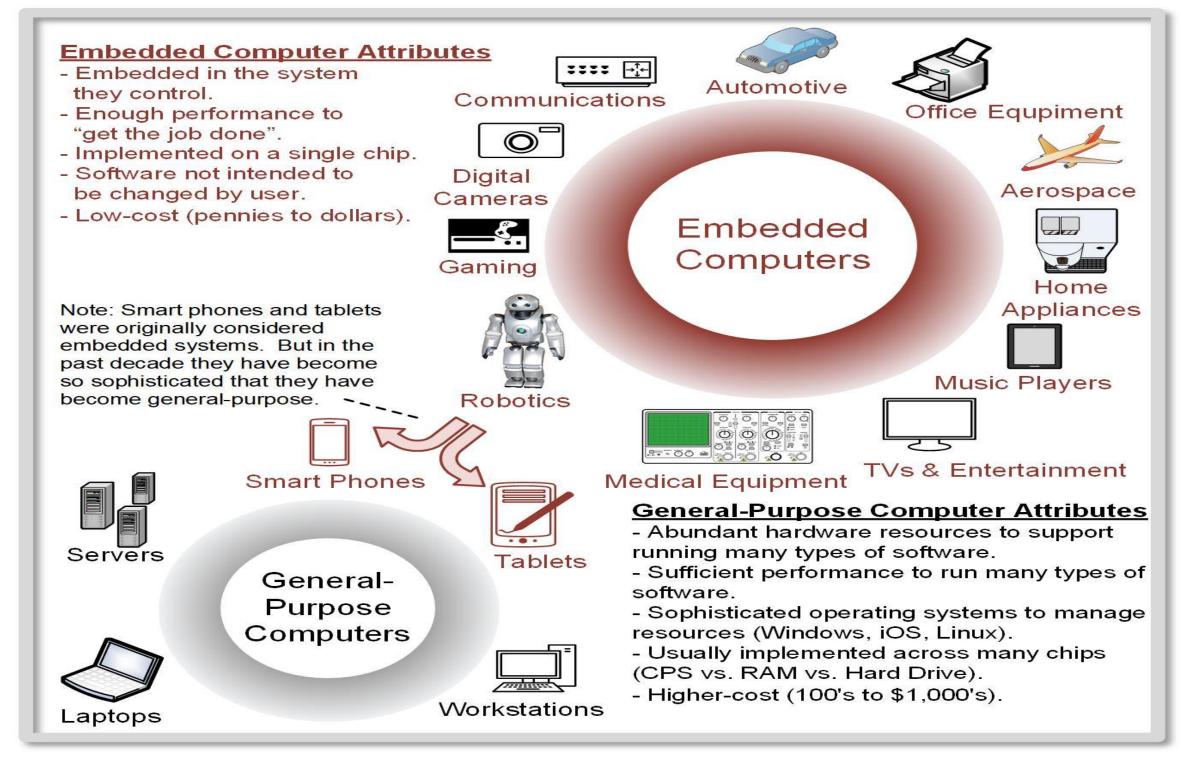

#### **GENERAL-PURPOSE COMPUTERS**

- Able to run a variety of software.

- Contain relatively high-performance hardware components (fast processors, data & program storage).

• Require an operating system (OS).

# INSTITUTIONS

#### **GENERAL-PURPOSE COMPUTERS**

- Designed for heavy user interaction.

- Uses a variety of peripherals

(displays, keyboards, mice, internet connections, wireless communication capability).

- Expensive (\$100s \$1000s).

- Use a group of integrated circuits or chips (ICs).

- One implements the central processing unit (CPU).

- Several implement data memory and program storage.

- Possesses a *distributed* architecture (full functionality of the computer is spread across multiple IC chips).

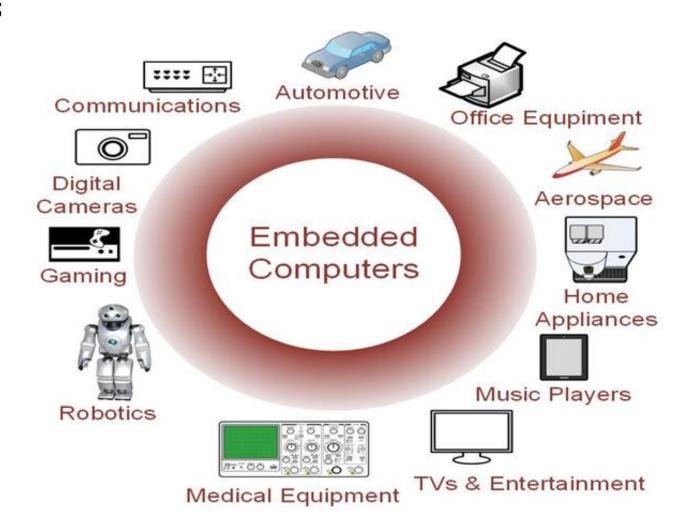

#### **EMBEDDED COMPUTERS**

- Resources can be implemented on a single IC.

- Include a variety of peripherals (timers, analog-to-digital converters, digital-to-analog converters, serial interfaces).

- Small size makes them very versatile.

#### **EMBEDDED COMPUTERS**

- Contains firmware (only the *needed* software which is not intended to be changed frequently).

- May contain Real Time Operating Systems (RTOS) which are used as a task scheduler.

- Low cost (10s of cents to a few dollars).

#### **EMBEDDED COMPUTERS**

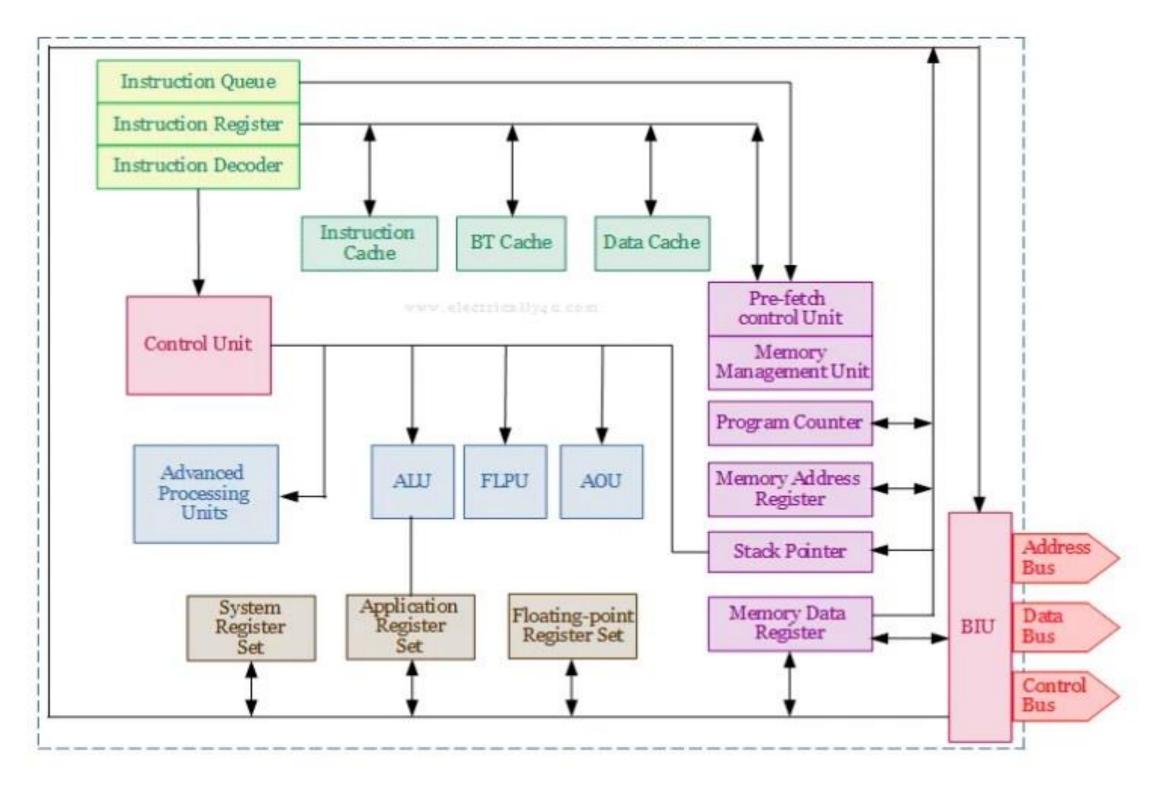

☐ The processor in any embedded system contains various units for its successful and fast operation. Buses, memories, processing units, instructions, registers, control units are some of the structural units that an embedded processor should possess.

Reference Image: https://microcontrollerslab.com/wp-content/uploads/2017/06/Embedded-processors-686x415.jpg

#### **CONTENTS**

- •Internal Buses

- Instruction Units

- <u>Caches</u>

- Control Units

- Processing Units

- Register Sets

- Memory Registers

- Program Counter and Stack Pointer

#### **Internal Buses**

- •It internally connects all the structural units inside the processor. Its width can be of 8, 16, 32 or 64 bits. The internal buses include address bus, data bus and control bus.

- All the internal units of the processor are communicated with the external buses through an interface unit called *Bus Interface Unit(BIU)*.

Image Reference:

https://1.bp.blogspot.com/eXdxVwWXxew/XL\_4qxXDe\_I/AAAAAAAAE/umQII6l37blZJGyoJrlVSTs0k2K8GsfpgCLcBGAs/s1600/Overview+of+system+bus+and+external+bus.png

- •Address bus is an external bus that carries the address from the Memory Address Register(MAR) to the memory as well as to the IO devices and other units of the system.

- •Data bus is an external bus that carries the data from or to the address determined by Memory Address Register(MAR).

- •Control Bus is an external bus that carries, control signals to or between the processor and memory.

Reference: https://image.. slidesharecdn.com/03computerarchitecture-170805155428/95/computer-system-architecture-lecture-note-3-computer-architecture-31-638jpg?cb=1501948498

#### **Instruction Units**

- •The processor executes several operations with the help of a piece of code or program called instructions. All these instruction are arranged in a queue called *Instruction Queue(IQ)*.

- •This helps the Instruction Register to execute the instructions without the need to wait.

- •Instruction Register(IR) takes the instruction codes(opcodes) sequentially to the execution unit of the processor.

- •Instruction decoder(ID) decodes the instruction opcode received at the Instruction Register and passes it to the processor Control unit for its execution..

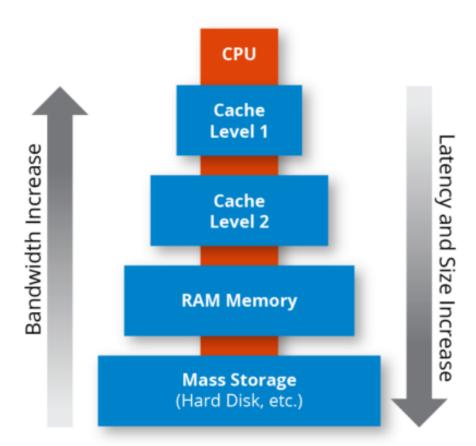

#### **CACHES**

- •In general, cache is the temporary storage place in the processor, where the data can easily be retrieved by the CPU for quick operation.

- •Cache is available in your computers, laptop, mobile phone, browser, app, etc. The embedded processor has three cache memory for fast operation.

Reference: https://hazelcast.com/wp-content/uploads/2021/12/diagram-MemoryCache-400x400-1.png

□ Branch Target Cache(BT Cache) facilitates the ready availability of the next instruction set, when a branch instruction like jump, call or loop is encountered. Its fetch unit foresees a branching instruction in the I − cache.

□ Data Cache(D – Cache) stores the pre – fetched data from the external memory.

#### **Control Units**

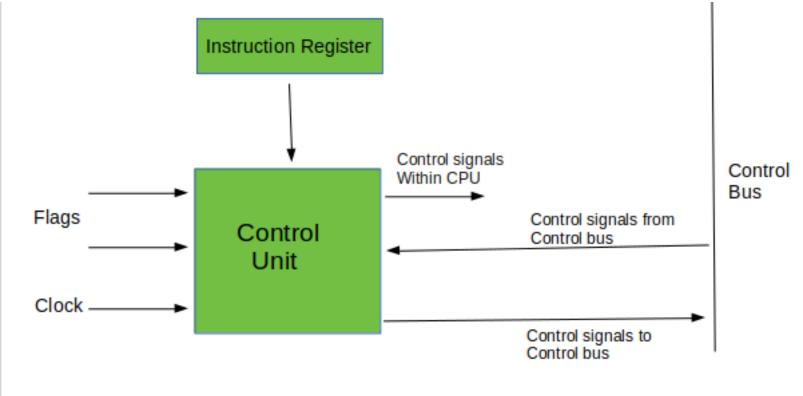

- ☐ The *control unit(CU)* is one of the important structural units in an any embedded processor. It is responsible for all the control of the bus activities and unit functions needed for processing.

- ☐ It directs all the units of a processor to respond to the instruction that is executed.

Block Diagram of the Control Unit

## Pre fetch control Unit(PFCU)

□ controls the fetching of data into the I-Cache and D-Cache in advance from the memory unit.

#### Memory Management Unit(MMU):

- ☐ manages the memories such that the instructions and data are readily available for processing.

- ☐ There are several memory management methods for managing the memory in an embedded processor such as fixed block allocation, dynamic block allocation, dynamic page allocation, etc.

#### **Processing Units**

Processing units receives the input data, process it and produces the output.

Depending on the function of the embedded system, the processing is done through different units like ALU, FLPU, AOU and advanced units.

#### Arithmetic Logic Unit(ALU)

It is used for the execution the arithmetic and logic instructions according to the instruction present at the Instruction Register.

- Floating point processing unit(FLPU) is different from ALU, used primarily for floating point processing. It is essential for fast processing mathematical functions in a microprocessor or Digital Signal Processor.

- \* Atomic operation unit(AOU) lets a user (compiler) instruction when broken into number of processor instructions called atomic operations, finish before an interrupt of the processor occurs..

#### **Register Sets**

Application Register Set(ARS) is a set of on-chip registers used during processing of instructions of the application program of the user.

A register window consists of a subset of registers with each subset storing static variables of software – routine.

*System Register Set(SRS)* is a set of registers used while processing the instructions of the supervisory system program.

**Floating point register set(FRS)** is dedicated for storing floating point numbers in the standard format and used by Floating point Processing Units for its data.

#### **Memory Registers**

Registers are smallest part of the CPU, where the data and address can be stored and accessed quickly. There are various registers like accumulator, general purpose registers, flag registers, memory address register, memory data register, program counter, stack pointer, etc.

*Memory Address Register(MAR)* holds the address of the data byte or word that is to be fetched from external memories. *Memory Data Register(MDR)* holds the data byte or word that is fetched from external memory or stored to the external memory.

# Program Counter M→ADDRESS(Next) and Stack Pointer (Last)

**Program counter** is a register that stores the address of the next instruction to be executed from the memory. It generates the instruction cycle to fetch the address from memory through MAR.

**Stack pointer** is a register that stores the address of the last program request in a stack. It is a pointer for an address which corresponds to a stack top in the memory.

# **SUMMARY & THANK YOU**