### SNS COLLEGE OF TECHNOLOGY

# (AN AUTONOMOUS INSTITUTION) COIMBATORE-35

# 19ECB211 - MICROCONTROLLER PROGRAMMING AND INTERFACING

UNIT V ADVANCED MICROCONTROLLERS

# ARM MICROCONTROLLER -Registers

#### **ARM7 REGISTERS**

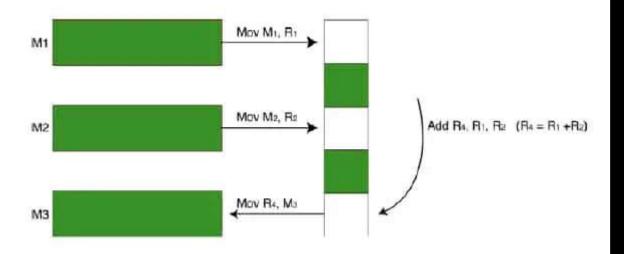

The ARM-7 is a load and store architecture, where if you want to perform any data processing instructions, then first the data has to move from a memory store into a set of central registers, the data processing instruction has to be executed and then the data again stored back into the memory.

The central set of registers are a bank of 16 registers from R0 – R15. Each of these registers is having 32-bit wide whereas R0 – R12 are user registers and R13 – R15 having some special functions. Where the R13 is called a Stack Pointer (SP), R14 is called Linked Register (LR), and the R15 is the Program Counter (PC).

## **ARM Microcontroller Register Modes**

An ARM microcontroller is a load store reducing instruction set computer architecture means the core cannot directly operate with the memory. The data operations must be done by the registers and the information is stored in the memory by an address. The ARM cortex-M3 consists of 37 register sets wherein 31 are general purpose registers and 6 are status registers.

The ARM uses seven processing modes to run the user task.

- •USER Mode

- •FIQ Mode

- •IRQ Mode

- •SVC Mode

- •UNDEFINED Mode

- •ABORT Mode

- Monitor Mode

| USER                                                                          | FIQ                                    | IRQ                           | SVC                           | Undefine                      | ABORT                         | Mon                           |

|-------------------------------------------------------------------------------|----------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| r0<br>r1<br>r2<br>r3<br>r4<br>r5<br>r6<br>r7<br>r8<br>r9<br>r10<br>r11<br>r12 | User Mode r0-r7  r8  r9  r10  r11  r12 | User<br>Mode<br>Rr0-r12       | User<br>Mode<br>Rr0-r12       | User<br>Mode<br>Rr0-r12       | User<br>Mode<br>Rr0-r12       | User<br>Mode<br>Rr0-r12       |

| r13(sp)<br>r14(lr)<br>r15(PC)                                                 | r13(sp)<br>r14(lr)<br>r15(PC)          | r13(sp)<br>r14(lr)<br>r15(PC) | r13(sp)<br>r14(lr)<br>r15(PC) | r13(sp)<br>r14(lr)<br>r15(PC) | r13(sp)<br>r14(lr)<br>r15(PC) | r13(sp)<br>r14(lr)<br>r15(PC) |

| CPSR                                                                          | SPSR                                   | SPSR                          | SPSR                          | SPSR                          | SPSR                          | SPSR                          |

**USER Mode:** The user mode is a normal mode, which has the least number of registers. It doesn't have SPSR and has limited access to the CPSR.

**FIQ and IRQ:** The FIQ and IRQ are the two interrupt caused modes of the CPU. The FIQ is processing interrupt and IRQ is standard interrupt. The FIQ mode has additional five banked registers to provide more flexibility and high performance when critical interrupts are handled.

**SVC Mode:** The Supervisor mode is the software interrupt mode of the processor to start up or reset.

**Undefined Mode:** The Undefined mode traps when illegal instructions are executed. The ARM core consists of 32-bit data bus and faster data flow.

**THUMB Mode:** In THUMB mode 32-bit data is divided into 16-bits and increases the processing speed.

**THUMB-2 Mode:** In THUMB-2 mode the instructions can be either 16-bit or 32-bit and it increases the performance of the ARM cortex –M3 microcontroller. The ARM cortex-m3 microcontroller uses only THUMB-2 instructions.

Some of the registers are reserved in each mode for the specific use of the core. The reserved registers are

- •Stack Pointer (SP).

- •Link Register (LR).

- •Program Counter (PC).

- •Current Program Status Register (CPSR).

- •Saved Program Status Register (SPSR).

The reserved registers are used for specific functions. The SPSR and CPSR contain the status control bits which are used to store the temporary data. The SPSR and CPSR register have some properties that are defined operating modes, Interrupt enable or disable flags and ALU status flag. The ARM core operates in two states 32-bit state or THUMBS state.

#### LPC-2148 MICROCONTROLLER

The LPC-2148 is the widely used microcontroller from the ARM-7 family. It is manufactured by Philips and added with many inbuilt peripherals which making it more efficient and also it is more reliable for both beginners and high-end developers to learn and research.

15 User registers + PC

R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 is used as the stack pointer R13 R14

R15 (PC)

RO

R1

R2

R3

Current Program Status Register CPSR

R15 is the Program Counter

R14 is the link register

**STACK POINTER (SP-R13):** The stack pointer is a register called **Stack** inside the processor which stores the address of the next instruction in the which is going to be executed.

**STACK**: A stack is a special temporary buffer which stores the data from top-down.

**LINKED REGISTER** (**LR-R14**): The R14 is the linked register which stores the return information for subroutines, function calls, and exceptions. On reset, the processor sets the LR value to **0xFFFFFFFF**.

**PROGRAM COUNTER (PC-R15):** The program counter is the **R15** register in ARM-7 which contains the current address of the instruction which is executing. On reset, the processor loads the PC with the value of the reset vector, which is at address **0x0000004**. Bit[0] of the value is loaded into the **EPSR** T-bit at reset and must be 1.

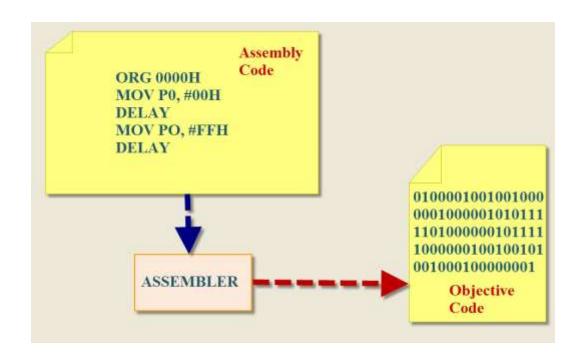

## **ARM-Cortex Microcontroller Programming**

The ARM microcontrollers runs at 100Mhz frequency and higher performance, therefore it supports the higher level languages. The ARM microcontroller is programmed with different IDES such as keiluvision3, keiluvision4, coocox and so on. A 8-bit microcontroller use 8-bit instructions and the ARM cortex-M uses a 32-instructions.

### **PREPARED BY:**

- 1. AJAYDEV 713521EC008

- 2. AVINASH 713521EC015

- 3. BOORNEUSH.M 713521EC017

- 4. DEEPIKA.M 713521EC019

- 5. GOWTHAM.S 713521EC029

- 6. JEYASUBRAMANIAN.S 713521EC041

- 7. SANJAY 713521EC512

- 8. KOUSIK RAJ -713521EC503

### **GUIDED BY:**

DR.B.SIVASANKARI

PROFESSOR

DEPARTMENT OF ECE

SNS COLLEGE OF TECHNOLOGY