# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## **19ECT312 – EMBEDDED SYSTEM DESIGN**

III YEAR/ VI SEMESTER

#### UNIT 2 : DEVICES AND EMERGING BUS STANDARDS

TOPIC 2.2 : Communication from serial devices-I2C

#### **COMMUNICATION FROM SERIAL DEVICES**

## Outline

- Introduction to Serial Buses

- UART

- SPI

- I2C

2/20/2023 2/20/2023 19ECT312/Emb.Sys / Dr.Sivanaynkathia/R.Solfesson//ECE//SWSCT

#### 2/17

#### What is I<sup>2</sup>C (or I2C)?

- Inter-Integrated Circuit

- Pronounced "eye-squared-see"

- Two-wire serial bus protocol

- Invented by Philips in the early 1980's

- That division now spun-off into NXP

#### Where is it Used?

- Originally used by Philips inside television sets

- Now very common in peripheral devices intended for embedded systems use

- Philips, National Semiconductor, Xicor, and Siemens , ...

- Also used in the PC world

- Real time clock

- Temperature sensors

## **Basic Description**

- Two-wire serial protocol with addressing capability

- Speeds up to 3.4 Mbit/s

- Multi-master/Multi-slave

## **Electrical Wiring**

- Two lines

- SDA (data)

- SCL (clock)

- Open-collector

- Very simple interfacing between different voltage levels

# Clock

- Not a traditional clock

- Normally high (kept high by the pull-up)

- Pulsed by the master during data transmission (whether the master is transmitter or receiver)

- Slave device can hold clock low if it needs more time

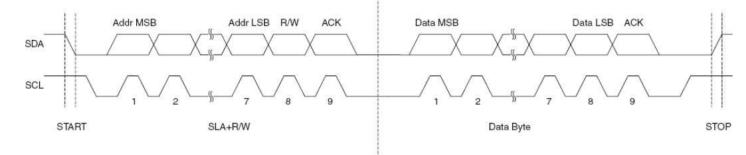

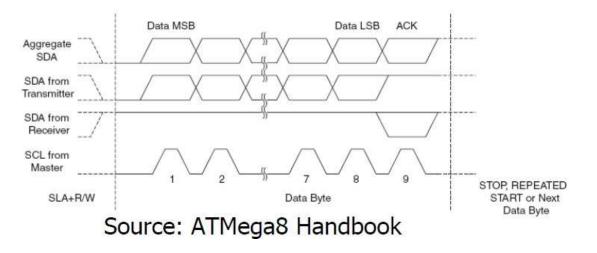

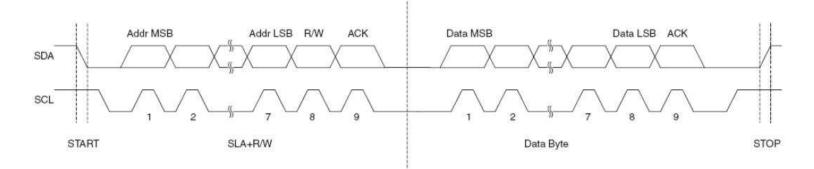

## A Basic I2C Transaction

- Master always initiates transactions

- Start Condition

- Address

- Data

- Acknowledgements

- Stop Condition

Source: ATMega8 Handbook

19ECT312/Emb.Sys / Dr.Sivasankari/Professor/ECE/SNSCT

2/20/2023

## A Basic I2C Transaction

- Transmitter/Receiver differs from Master/Slave

- Master initiates transactions, slave responds

- Transmitter sets data on the SDA line, Receiver acknowledges

- For a read, slave is transmitter

- For a write, master is transmitter

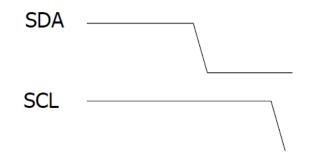

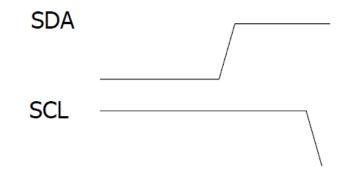

## Start Condition

Master pulls SDA low while SCL is high

Normal SDA changes only happen while SCL is low

## Address Transmission

- Data is always sampled on rising edge of clock

- Address is 7 bits

- An 8th bit indicates read or write

- High for read, low for write

- Addresses assigned by Philips/NXP (for a fee)

## Data transmission

- Transmitted just like address (8 bits)

- For a write, master transmits, slave acknowledges

- For a read, slave transmits, master acknowledges

- Transmission continues with subsequent bytes until master creates stop condition

## **Stop Condition**

Master pulls SDA high while SCL is high

Also used to abort transactions

## Another look at I2C

Source: ATMega8 Handbook

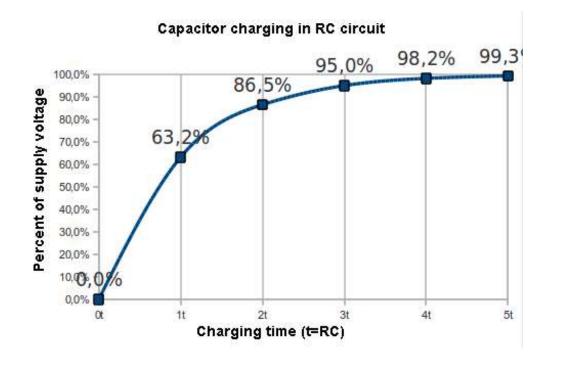

## Exercise: How fast can I2C run?

- How fast can you run it?

- Assumptions

- 0's are driven

- 1's are "pulled up"

- Some working figures ullet

- $-R_{p} = 10 \text{ k}\Omega$

- $-C_{cap} = 100 \text{ pF}$

- $-V_{DD} = 5 V$

- $V_{in_high} = 3.5 V$

- Recall for RC circuit

- $-V_{cap}(t) = V_{DD}(1-e^{-t/\tau})$

- Where  $\tau = RC$

# Exercise: Bus bit rate vs Useful data rate

- An I2C "transactions" involves the following bits

- <S><A6:A0><R/W><A><D7:D0><A><F>

- Which of these actually carries useful data?

- <S><A6:A0><R/W><A><D7:D0><A><F>

- So, if a bus runs at 400 kHz

- What is the clock period?

- What is the data throughput (i.e. data-bits/second)?

- What is the bus "efficiency"?

#### **SUMMARY & THANK YOU**

2/20/2023 2/20/2023 19ECT312/Emb.Sys / Dr.Sivanaynkathia P.Solfe & M.//ECE//SNASCIT

#### 17/17