### Intel 8088

- ➤ Introduced in 1979.

- $\triangleright$  It was also 16-bit  $\mu$ P.

- It was created as a cheaper version of Intel's 8086.

- It was a 16-bit processor with an 8-bit external bus.

### Intel 80186 & 80188

- ➤ Introduced in 1982.

- > They were 16-bit μPs.

- Clock speed was 6 MHz.

- ➤ 80188 was a cheaper version of 80186 with an 8-bit external data bus.

### Intel 80286

- ➤ Introduced in 1982.

- $\triangleright$  It was 16-bit  $\mu$ P.

- > Its clock speed was 8 MHz.

- ➤ Its data bus is 16-bit and address bus is 24-bit.

- ➤ It could address 16 MB of memory.

# Intel 80386 in 1986.

- $\triangleright$  It was first 32-bit  $\mu$ P.

- ➤ Its data bus is 32-bit and address bus is 32-bit.

- ➤ It could address 4 GB of memory.

- ➤ It had 2,75,000 transistors.

- ➤ Its clock speed varied from 16 MHz

# Intel 80486ed in 1989.

- $\triangleright$  It was also 32-bit  $\mu$ P.

- ➤ It had 1.2 million transistors.

- ➤ Its clock speed

varied from 16 MHz

to 100 MHz

depending upon the

various versions.

- ➤ 8 KB of cache memory was

# Intel Pantium in 1993.

- $\triangleright$  It was also 32-bit  $\mu$ P.

- ➤ It was originally named 80586.

- ➤ Its clock speed was 66 MHz.

- ➤ Its data bus is 32-bit and address bus is 32-bit.

### Intel Pentium Pro

- ➤ Introduced in 1995.

- $\triangleright$  It was also 32-bit  $\mu$ P.

- ➤ It had 21 million transistors.

- ➤ Cache memory:

- >8 KB for instructions.

- ▶8 KB for data.

### Intel Pentium II

- ➤ Introduced in 1997.

- $\triangleright$  It was also 32-bit  $\mu$ P.

- ➤ Its clock speed was 233 MHz to 500 MHz.

- Could execute 333 million instructions per second.

### Intel Pentium II Xeon

- ➤ Introduced in 1998.

- $\triangleright$  It was also 32-bit  $\mu$ P.

- ➤ It was designed for servers.

- ➤ Its clock speed was 400 MHz to 450 MHz.

### Intel Pentium III

- ➤ Introduced in 1999.

- $\triangleright$  It was also 32-bit  $\mu$ P.

- ➤ Its clock speed varied from 500 MHz to 1.4 GHz.

- ➤ It had 9.5 million transistors.

### Intel Pentium IV

- ➤ Introduced in 2000.

- $\triangleright$  It was also 32-bit  $\mu$ P.

- ➤ Its clock speed was from 1.3 GHz to 3.8 GHz.

- ➤ It had 42 million transistors.

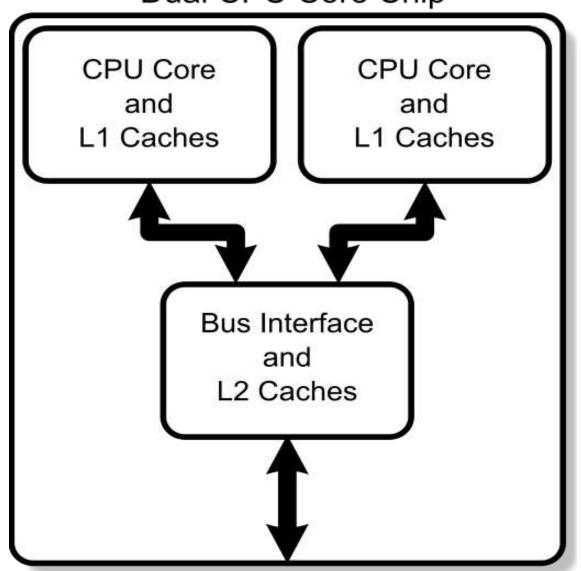

## Intel Duab Gage in 2006.

> It is 32-bit or 64-bit  $\mu$ P.

#### **Dual CPU Core Chip**

# 64-bit Microprocessors

#### **Intel Core 2**

#### **Intel Core i3**

### **Intel Core i5**

#### **INTEL CORE 17**

# **Basic Terms**

- Bit: A digit of the binary number { 0 or 1 }

- Nibble: 4 bit Byte: 8 bit word: 16 bit

- Double word: 32 bit

- Data: binary number/code operated by an instruction

- Address: Identification number for memory locations

- Clock: square wave used to synchronize various devices in μP

- Memory Capacity = 2<sup>n</sup>,

n->no. of address lines

Falling edge

### **BUS CONCEPT**

BUS: Group of conducting lines that carries data, address & control signals.

#### **CLASSIFICATION OF BUSES:**

- **1.DATA BUS:** group of conducting lines that carries data.

- 2. ADDRESS BUS: group of conducting lines that carries address.

- **3.CONTROL BUS:** group of conducting lines that carries control signals {RD, WR etc}

- CPU BUS: group of conducting lines that directly connected to  $\mu P$

- SYSTEM BUS: group of conducting lines that carries data, address & control signals in a  $\mu P$  system

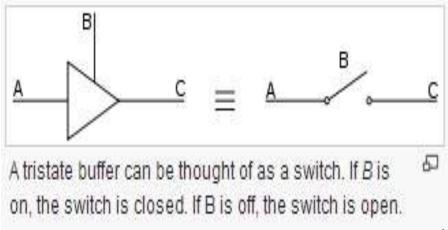

### TRISTATE LOGIC

#### 3 logic levels are:

- High State (logic 1)

- Low state (logic 0)

- High Impedance state

**High Impedance**: output is not being driven to any **defined** logic level by the output circuit.

| INPUT |   | OUTPUT            |

|-------|---|-------------------|

| Α     | В | С                 |

| 0     | 1 | 0                 |

| 1     |   | 1                 |

| х     | 0 | Z(high impedance) |

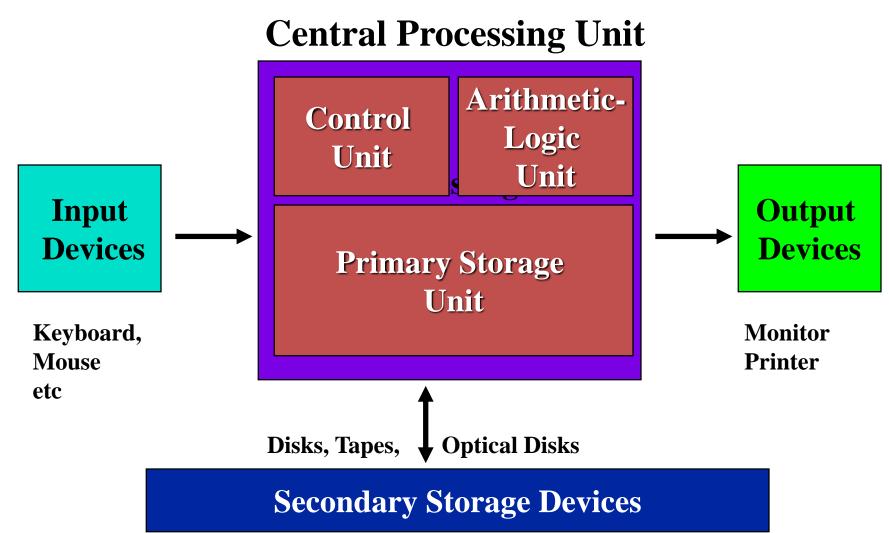

# **Basic Microprocessors System**