## SNSCOLLEGEOFTECHNOLOGY

Coimbatore -35

An Autonomous Institution

Accredited by NBA AICTE and Accredited by NAAC UGOwith î <sup>a</sup>Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENTOFELECTRONIC&NDCOMMUNICATION ENGINEERING

19ECB21 DIGITALELECTRONSC

II YEAR/III SEMESTER

UNIT5 SEQUENTIAMERCUITS

TOPIC5 – Analysis and design of clocked sequentiatuits –

Moore/Mealymodels example

## **Analysis Procedure**

- •Identify type of circuit either Mealy or Moore circuit

- •Derive excitation equation (Boolean expression)

- Derive next state and output equations

- •Generatestatetable

- •Generatestatediagram

#### **Analysis Procedure**

#### DESIGN PROCEDURE FOR CLOCKED SEQUENTIAL CIRCUIT

The following stepsare followed to design the clocked sequential ogic circuit.

- •Obtainthe state table from the given circuit information such as a state diagram, atiming diagram or description.

- •The number of states may be reduce by state reduction technique.

- •Assignbinary values to each staten the state table.

- •Determine the number offlip flops required and assigna letter symbol to each flip flop.

- •Choosetheflip flop type to be used according to the application.

- •Derive the excitation table from the reduced state table.

- •Derive the expression for flip flop inputs and outputs using k-maps implification (The present tate and inputs are considered for k-maps implification) and drawlogic circuit

## **Analysis of Sequential Logic**

- 1. Analysis is the process that starts with an implementation and generates the function or behavior of the sequential circuit.

- i.e. given a logic schematicto generatæne ormore functionablescriptions using state diagrams state and outputables, and inputandoutput Boolean equations.

- 2. Synthesis, the reverse of analysis, starts with a behavioral description and generates an implementation

#### State-based or Moore-type sequential circuit.

The output values depend solely on its present state.

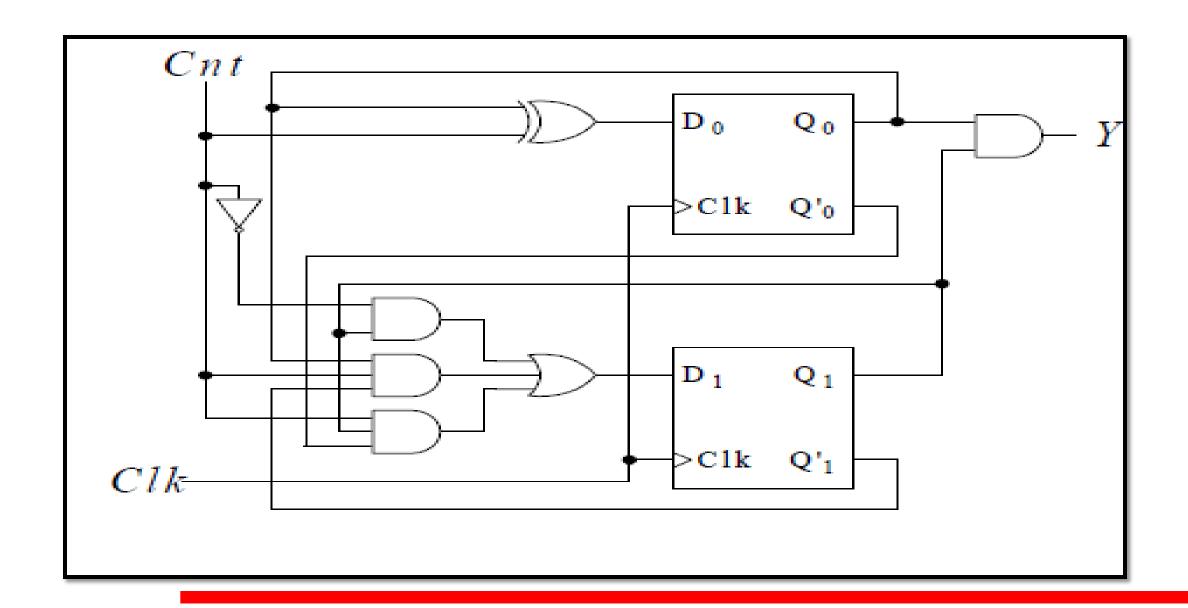

Derive the next tate, the output tables, and the statediagram for the (modulo 4 counter) sequential circuit represented by the following schematic.

#### **Solution:**

**Step 1 (Moore):** Derive excitation equations.

i.e., boolean expressions for the inputs of **dap**hflop in the schematic, in terms of the external input Cnt and the ff outputs Q1 and Q0.

Sincetherearetwo ffs in our example, we derive two expression for D1 and D0:

$$D_0 = Cnt \oplus Q_0 = Cnt'Q_0 + CntQ'_0$$

$$D_1 = Cnt'Q_1 + CntQ'_1Q_0 + CntQ_1Q'_0$$

#### **Solution:**

#### Step 2:

Derive the next-state equations by substituting the excitation equations into the flipflop characteristic equations.

The characteristic equations formally describe the functional behavior of a latch or flip-flop.

They specify the flip-flop's next state as a function of its current state and inputs. For the Dflip-flop, the characteristie quationis

$$Qnext = D$$

Thus, the nextate equations re:

$$\begin{aligned} Q_{0next} &= D_0 = Cnt \oplus Q_0 = Cnt'Q_0 + CntQ_0' \\ Q_{1next} &= D_1 = Cnt'Q_1 + CntQ_1'Q_0 + CntQ_1Q_0' \end{aligned}$$

Step 2b (Moore):

Derive the output equation.

$$Y = Q_1Q_0$$

#### <u>Solution:</u>

#### Step 3a:

Derive thenext-state tablerom the next-state equations.

Each row corresponds to a statetheef sequential circuit which is defined by the binary valuesstoredin its ffs.

Each columne presents ne set input values.

Each entry defines the value of the sequential circuit in the next clock cycle after the

rising edgeof the Clk.

| Present State | Next State                              |         | Outputs |

|---------------|-----------------------------------------|---------|---------|

| $Q_1Q_0$      | $Q_{1 \text{ next}} Q_{0 \text{ next}}$ |         | Y       |

|               | Cnt = 0                                 | Cnt = 1 |         |

| 00            | 00                                      | 01      | 0       |

| 01            | 01                                      | 10      | 0       |

| 10            | 10                                      | 11      | 0       |

| 11            | 11                                      | 00      | 1       |

#### **Solution:**

#### Step3b:

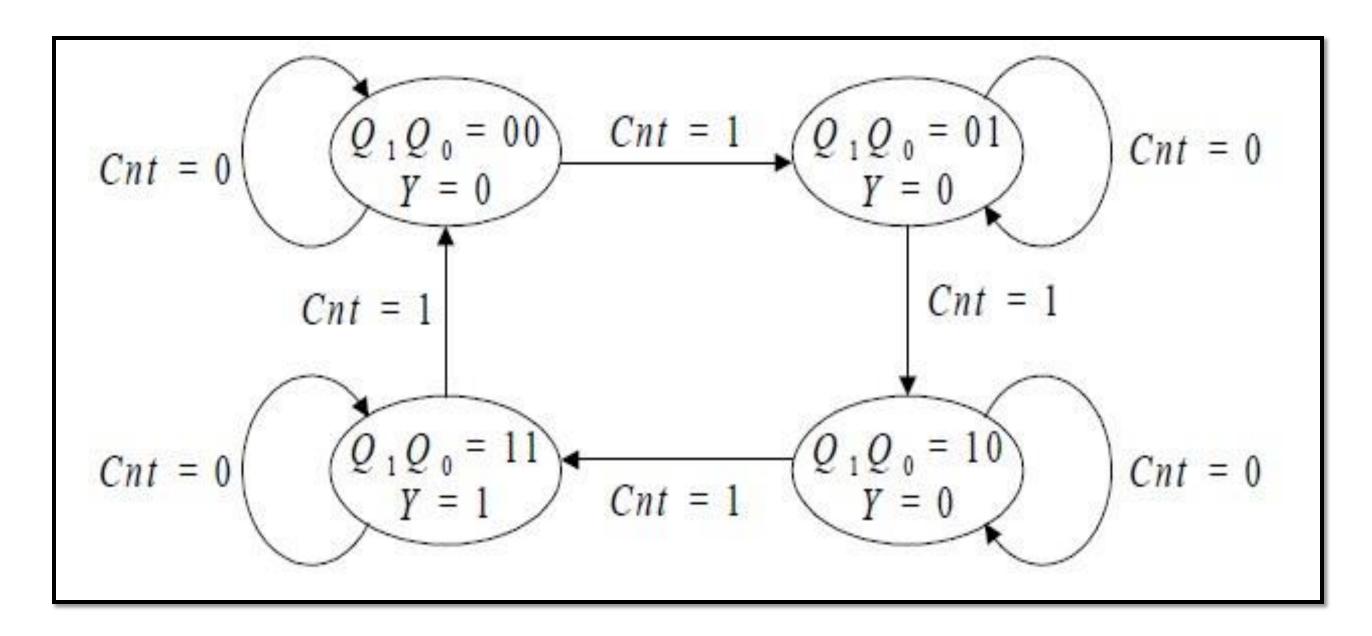

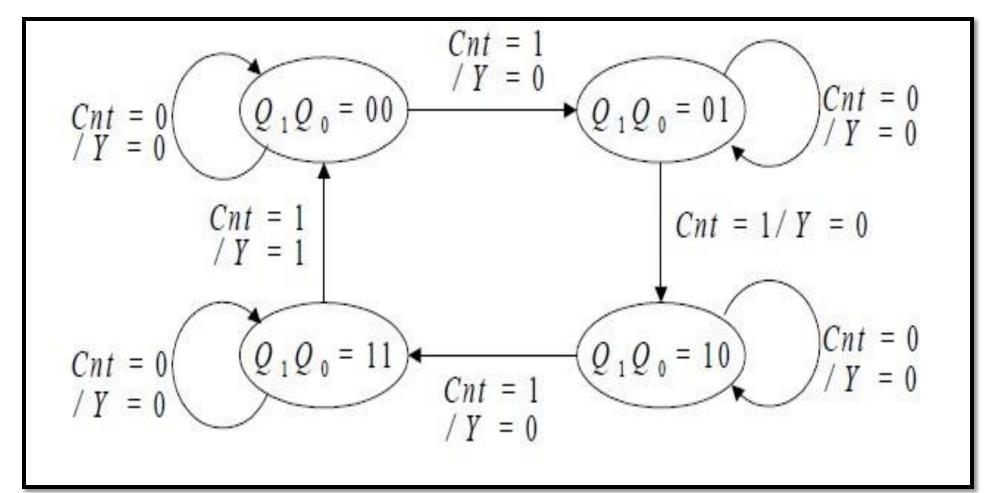

- Instead of a nexitate table, we could use a state diagram to represent the behavior of the sequentiatircuit.

- A statediagramis basically a pictorial representation of the next-state table. It has exactly one node for each presentate in the next-state table.

- > As long as Cnt=1, the sequentia circuit visits the states in the sequence 0,1,2,3,0,1,2,....

- ➤ When Cnt=0, the circuit stays in its present state until Cnt changes to 1, at which point the countingcontinues.

- > We conclude that the circuit is a modulo 4 counterwith one control signal, Cnt.

## Step3b:

## > Statediagram

## **Solution:**

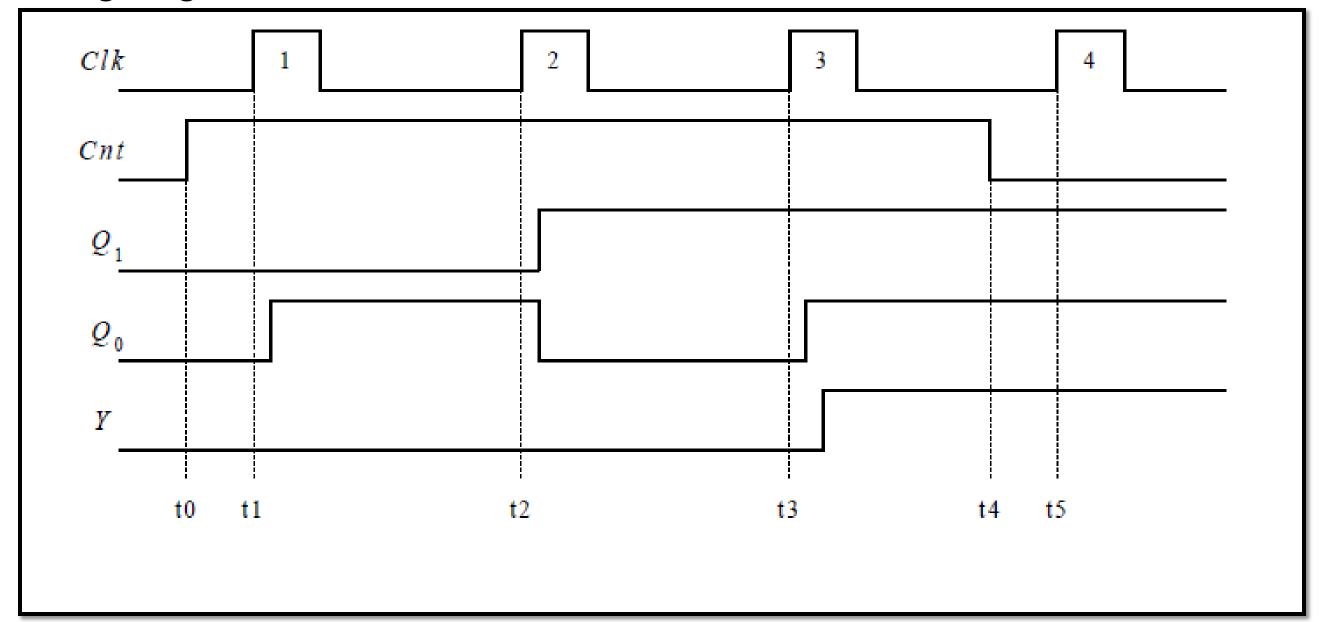

## Step 4:

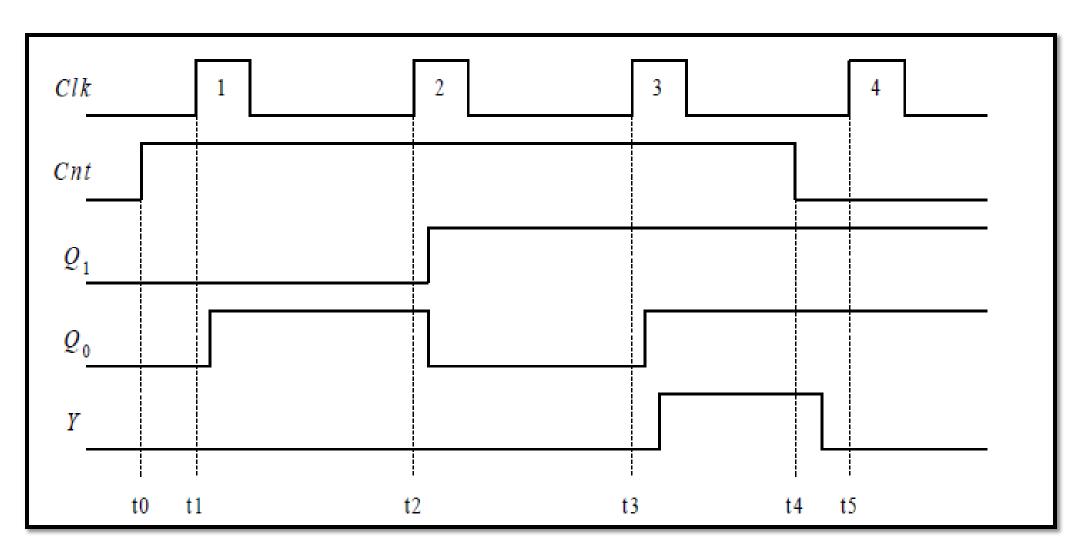

The timingdiagramis shown below:

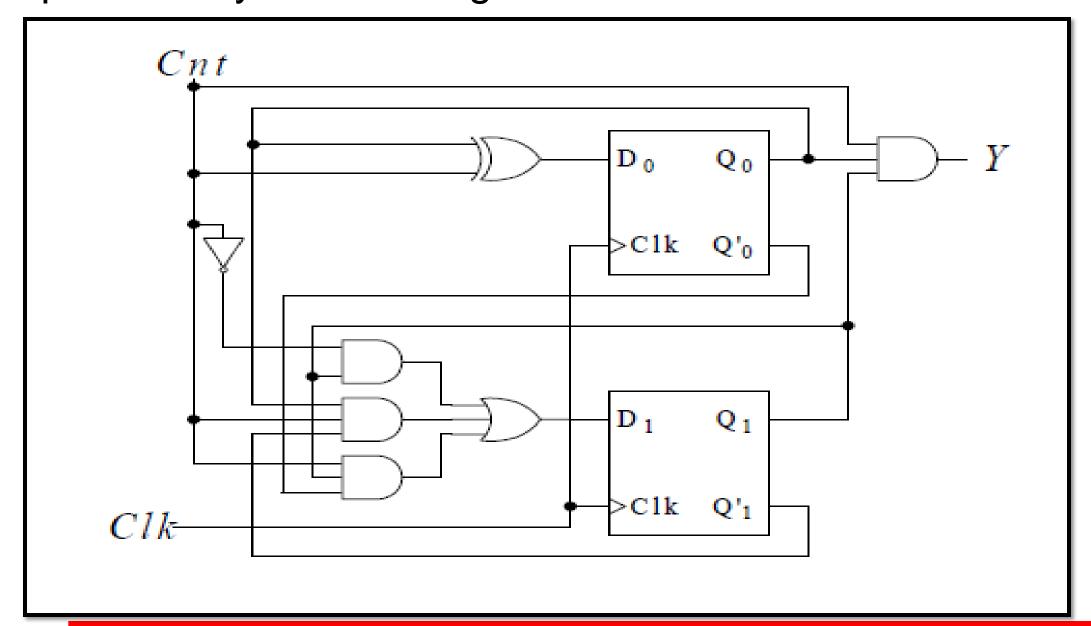

Input-based or Mealy-type sequential circuit. The output values are dependent in the input values as well as its presentate.

Derive the nexstate, the output tables, and the tatediagram for the (modulo 4 counter) sequentia bircuit represente by the following schematic.

Step1 (Mealy): Derive excitation equations.

$$\begin{split} D_0 &= Cnt \oplus Q_0 = Cnt'Q_0 + CntQ_0' \\ D_1 &= Cnt'Q_1 + CntQ_1'Q_0 + CntQ_1Q_0' \end{split}$$

Step2a (Mealy):Derive thenext-stateequations.

$$\begin{aligned} Q_{0next} &= D_0 = Cnt \oplus Q_0 = Cnt'Q_0 + CntQ_0' \\ Q_{1next} &= D_1 = Cnt'Q_1 + CntQ_1'Q_0 + CntQ_1Q_0' \end{aligned}$$

Step2b (Mealy): Derive the outputequation.

$$Y = CntQ_1Q_0$$

#### Step3a (Mealy):

Derive thenext-state/outputable. Every entry in the next-state table will represent he next-state and the output value, separate by a slash (/).

| Present State | Next State / Outputs                        |         |  |

|---------------|---------------------------------------------|---------|--|

| $Q_1Q_0$      | $Q_{1 \text{ next}} Q_{0 \text{ next}} / Y$ |         |  |

|               | Cnt = 0                                     | Cnt = 1 |  |

| 00            | 00 / 0                                      | 01 / 0  |  |

| 01            | 01/0                                        | 10 / 0  |  |

| 10            | 10 / 0                                      | 11 / 0  |  |

| 11            | 11 / 0                                      | 00 / 1  |  |

Step3b (Mealy):Derive the Stateliagram.

The output is not associated with the state but with the transition arc.

Eacharc is labeledwith both the input values that move the circuits from the present tate the next state, and the output values, which correspond to the signat values in the present state.

#### Step4 (Mealy): The timing diagrams shown below:

In clock cycle 3, the counterwill be in state Q1Q0= 11 and the output signal Y = 1. At t4, Y = 0 becaus the input signal Cnt = 0 eventhough the counters still in state Q1Q0= 11.

## THANK YOU