# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA - AICTE and Accredited by NAAC - UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

# **16EC303-VLSI DESIGN**

III YEAR/ V SEMESTER

# **UNIT 4 –VLSI TESTING**

**TOPIC 5: Design Strategies -BIST & BOUNDARY SCAN**

# OUTLINE

- Design for Test

- Scan-FLIPFLOP

- BIST

- PRSG

- BILBO

- Activity

- Boundary Scan

- Examples

- Interface

- summary

1/7/2023

# **DESIGN FOR TEST**

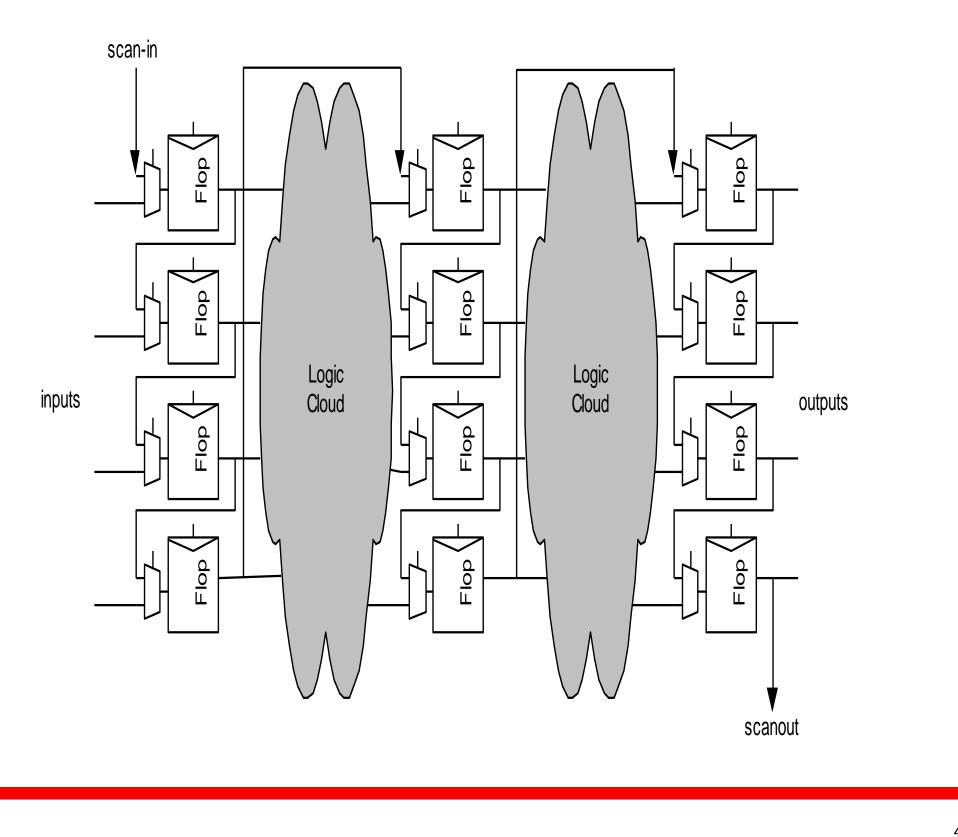

- •Design the chip to increase observability and controllability

- •If each register could be observed and controlled, test problem reduces to testing combinational logic between registers.

- •Better yet, logic blocks could enter test mode where they generate test patterns and report the results automatically.

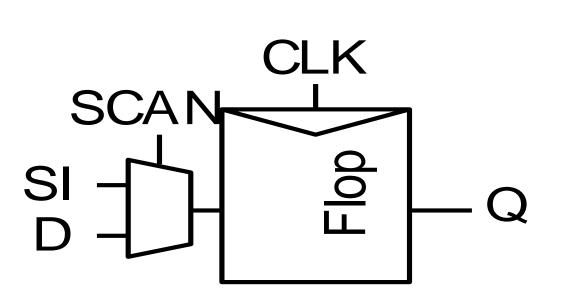

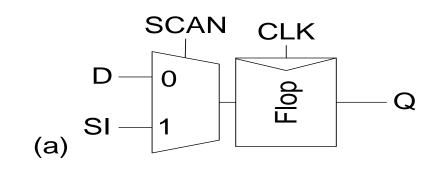

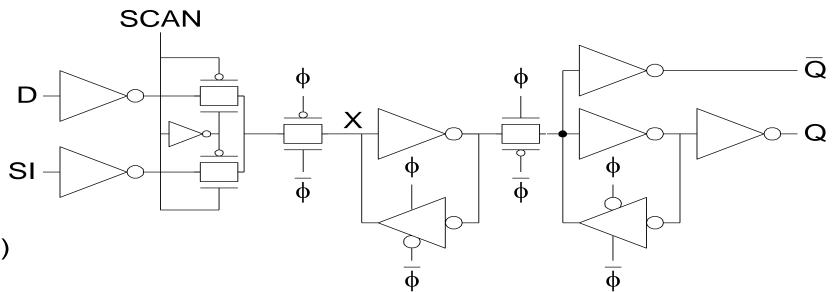

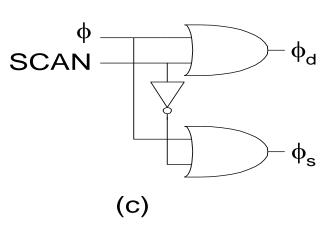

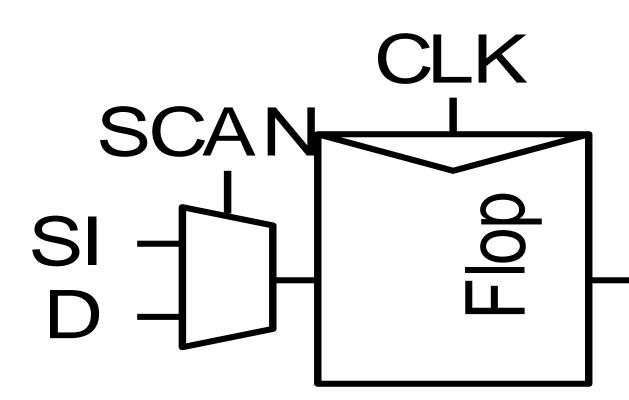

SCAN

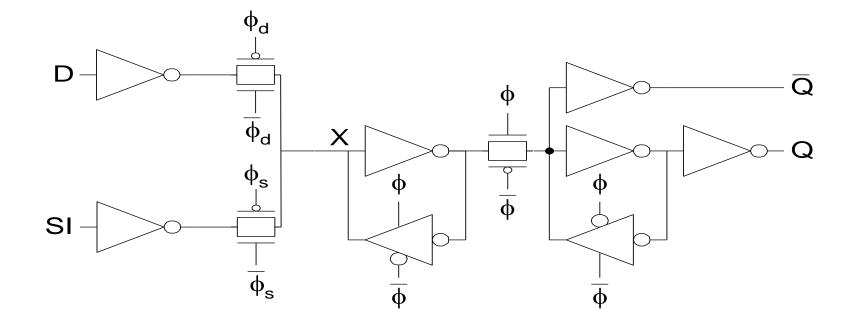

- Convert each flip-flop to a scan register

- Only costs one extra multiplexer

- Normal mode: flip-flops behave as usual

- Scan mode: shift register

- Contents of flops

can be scanned out and

new values scanned in

# **SCANNABLE FLIP-FLOPS**

(b)

1/7/2023

# **BUILT-IN SELF-TEST**

Built-in self-test lets blocks test themselves

high probability, block is fault-free if it produces the expected syndrome.

1/7/2023

# Generate pseudo-random inputs to comb. Logic. Combine outputs into a syndrome With

# PRSG

- Linear Feedback Shift Register

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

| Step | Q          |

|------|------------|

| 0    | 111        |

| 1    | 110        |

| 2    | 101        |

| 3    | 010        |

| 4    | 100        |

| 5    | 001        |

| 6    | 011        |

| 7    | 111 (repea |

1/7/2023

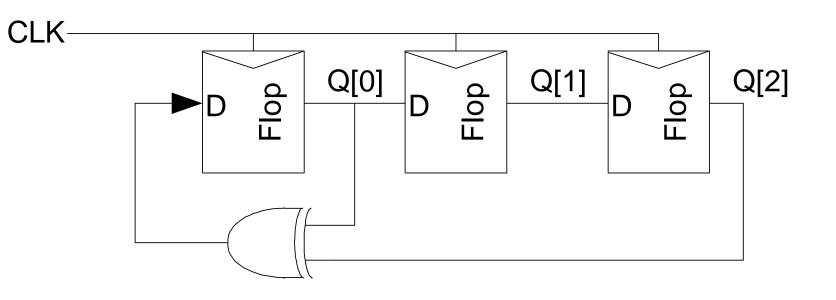

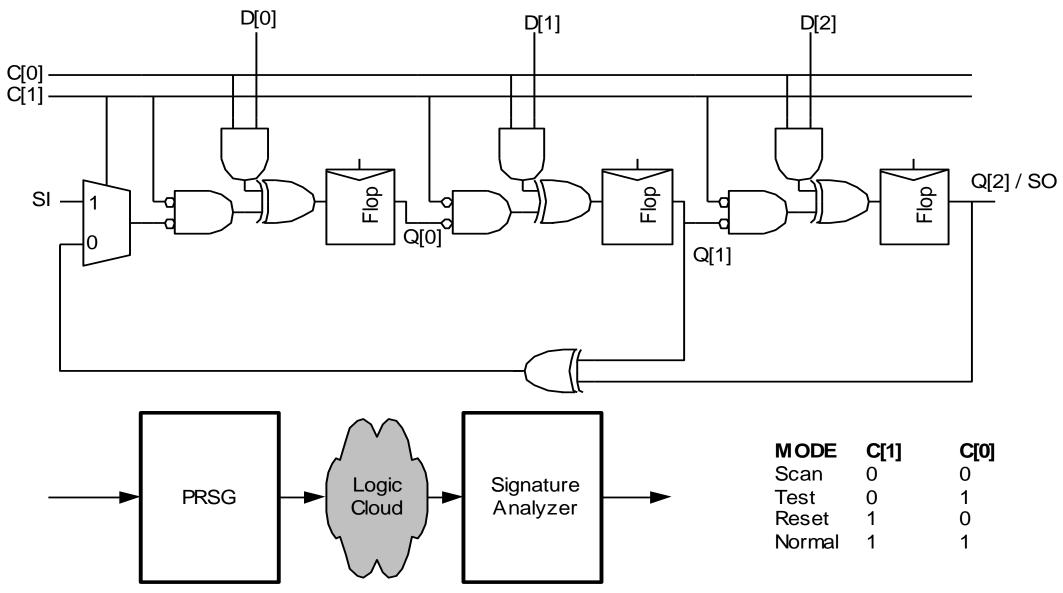

# **BILBO**

- Built-in Logic Block Observer

- Combine scan with PRSG & signature analysis

1/7/2023

| MODE   | <b>C</b> [1] | <b>C[</b> ( |

|--------|--------------|-------------|

| Scan   | 0            | 0           |

| Test   | 0            | 1           |

| Reset  | 1            | 0           |

| Normal | 1            | 1           |

# ACTIVITY

## DEBATE : BOYS VS GIRLS

1/7/2023

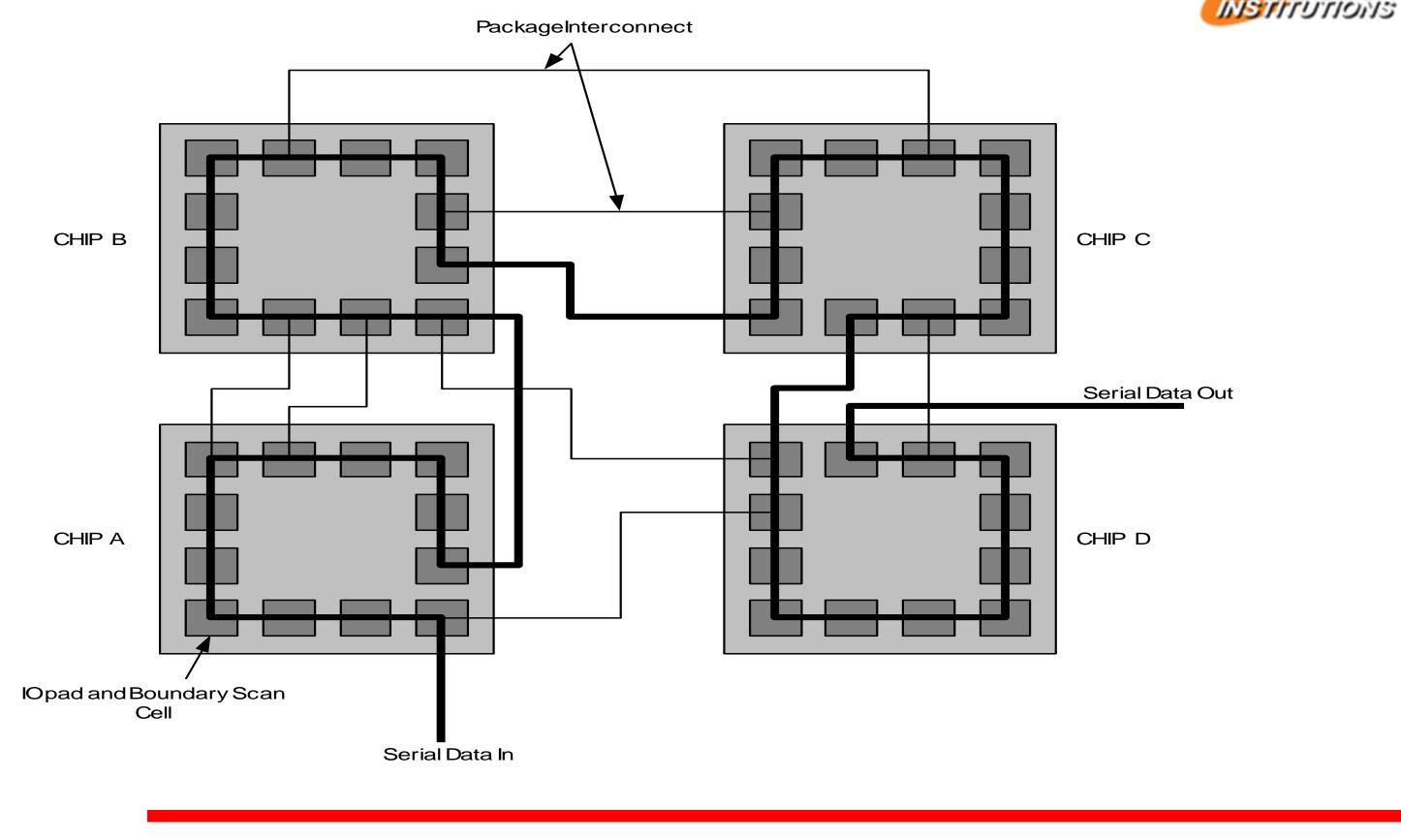

# **BOUNDARY SCAN**

- Testing boards is also difficult

- Need to verify solder joints are good

- Drive a pin to 0, then to 1

- Check that all connected pins get the values

- Through-hold boards used "bed of nails"

- SMT and BGA boards cannot easily contact pins

- Build capability of observing and controlling pins into each chip to make board test easier

# **BOUNDARY SCAN EXAMPLE**

1/7/2023

# **BOUNDARY SCAN INTERFACE**

Boundary scan is accessed through five pins

| TCK:          | test clock           |

|---------------|----------------------|

| TMS:          | test mode select     |

| <b>TDI:</b>   | test data in         |

| TDO:          | test data out        |

| <b>TRST*:</b> | test reset (optional |

Chips with internal scan chains can access the chains through boundary scan for unified test strategy.

1/7/2023

l) ains through

# SIMULATE

## Think about testing from the beginning Simulate as you go Plan for test after fabrication

"If you don't test it, it won't work! (Guaranteed)"

1/7/2023

# Q

## ASSESSMENT

0

1

2

3

4

5

6

7

# WRITE THE BOUNDARY SCAN PIN NAMES & FILL UP THE BLANK IN PRSG TABLE TCK: TMS: TDI: TDO: TRST\*:

1/7/2023

**4**

| Step | Q   |

|------|-----|

|      | 111 |

|      |     |

|      | 101 |

|      |     |

|      | 100 |

|      |     |

|      | 011 |

|      |     |

# **SUMMARY & THANK YOU**

1/7/2023