# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS AND COMMUNICATION** ENGINEERING

# **19ECB202 – LINEAR AND DIGITAL CIRCUITS**

II YEAR/, III SEMESTER

UNIT 5 – SEQUENTIAL CIRCUITS

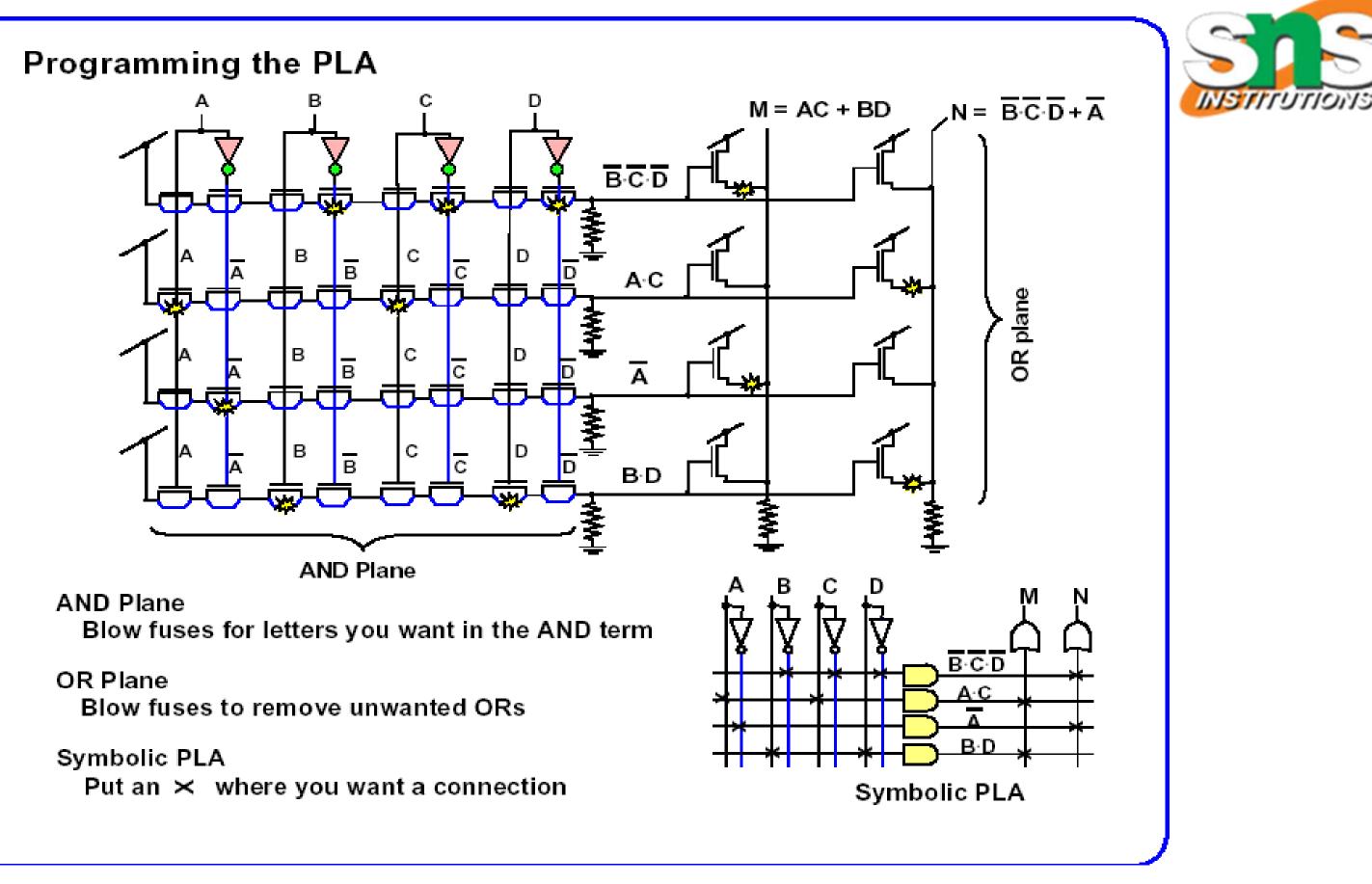

TOPIC 7 – Introduction to PLD implementation

## Problem definition

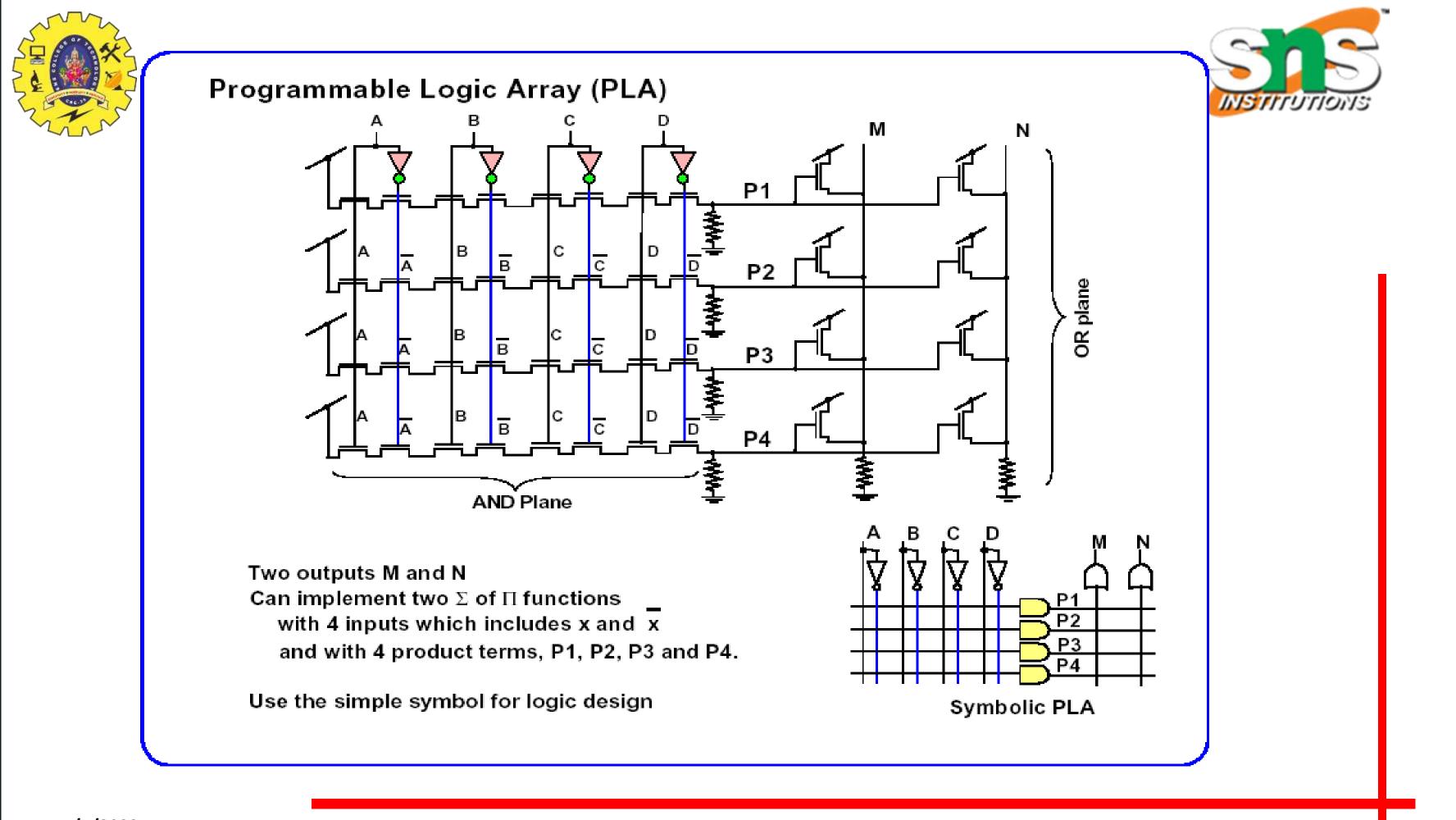

| Device | AND-array    | OR-array     |

|--------|--------------|--------------|

| PROM   | Fixed        | Programmable |

| PLA    | Programmable | Programmable |

| PAL    | Programmable | Fixed        |

| GAL    | Programmable | Fixed        |

- The differences between the first three categories are these:

- -1. In a ROM, the input connection matrix is hardwired. The user can modify the output connection matrix.

- -In a PAL/GAL the output connection matrix is hardwired. The user can modify the input connection matrix.

- -In a PLA the user can modify both the input connection matrix and the output connection matrix.

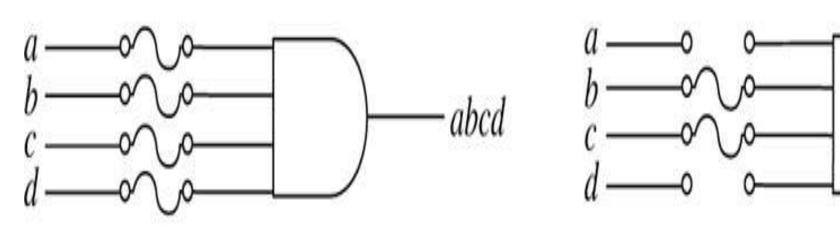

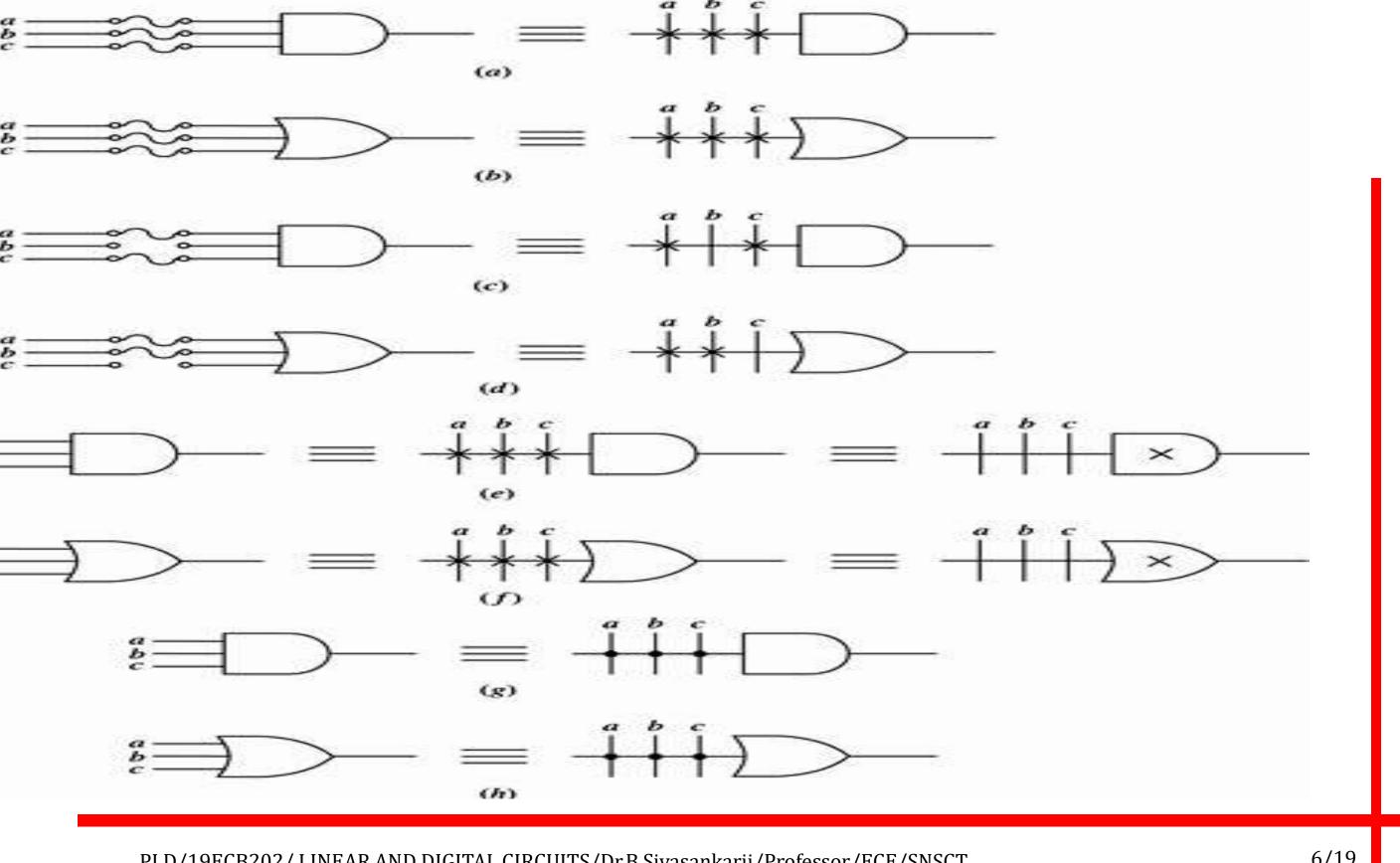

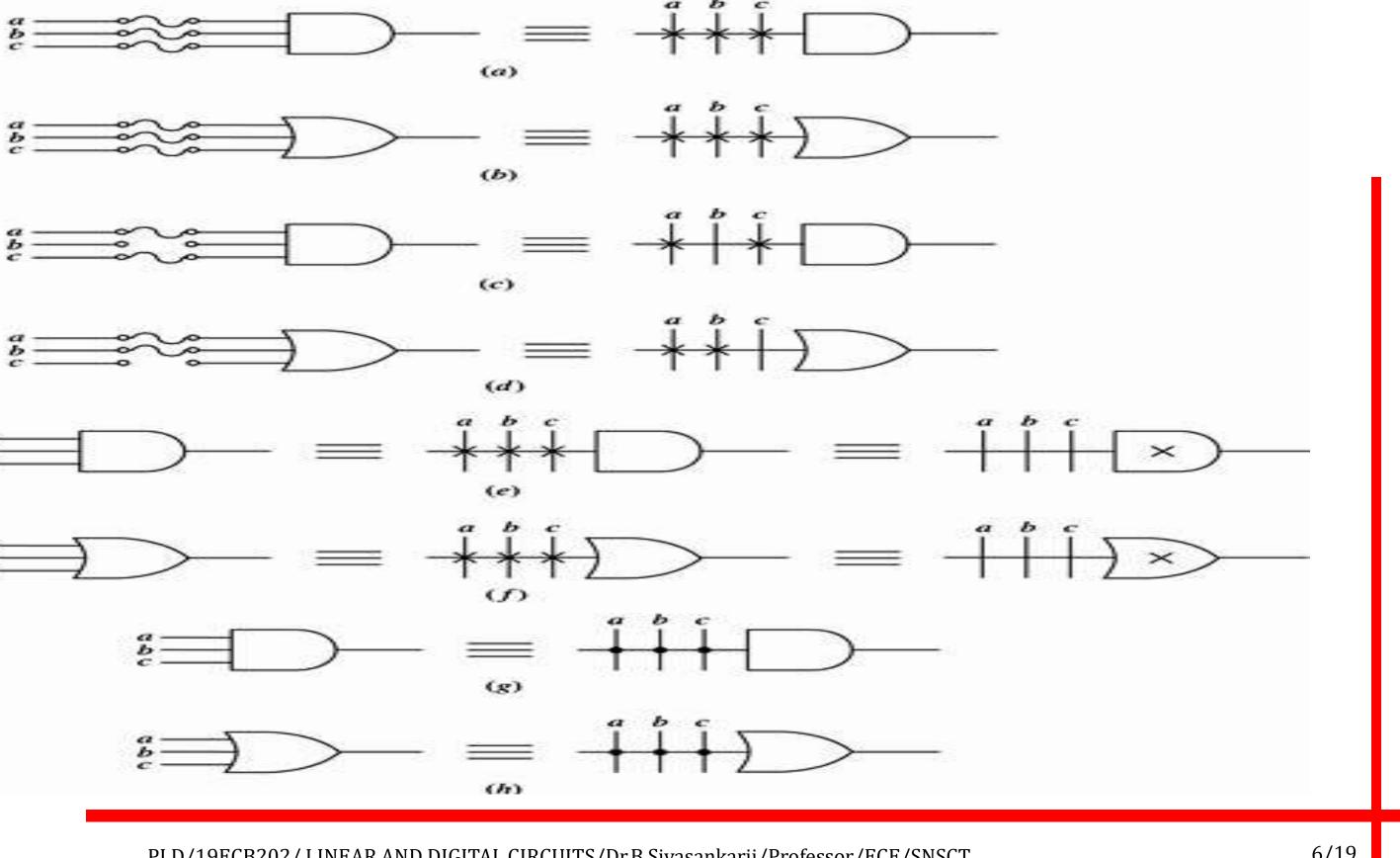

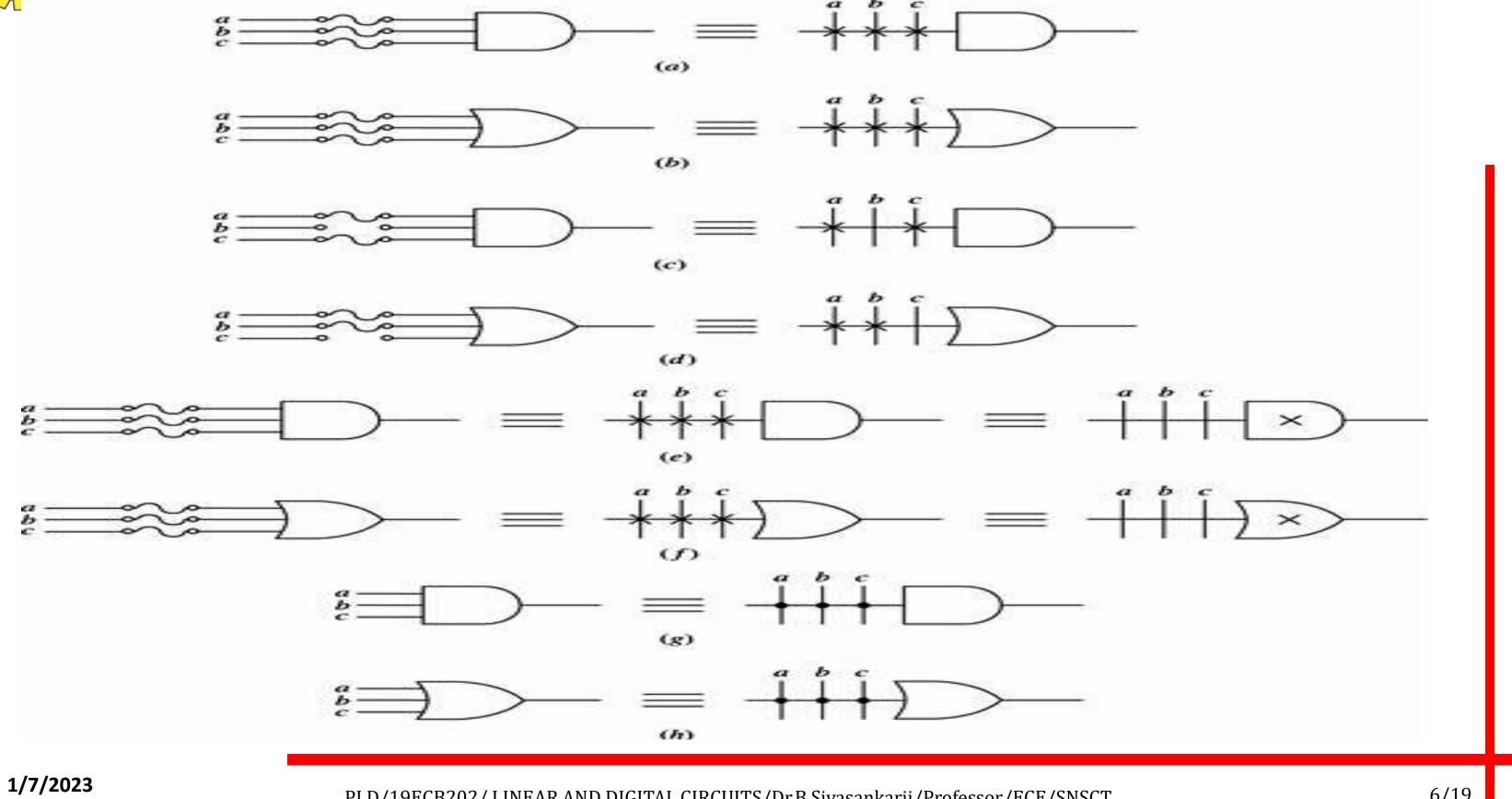

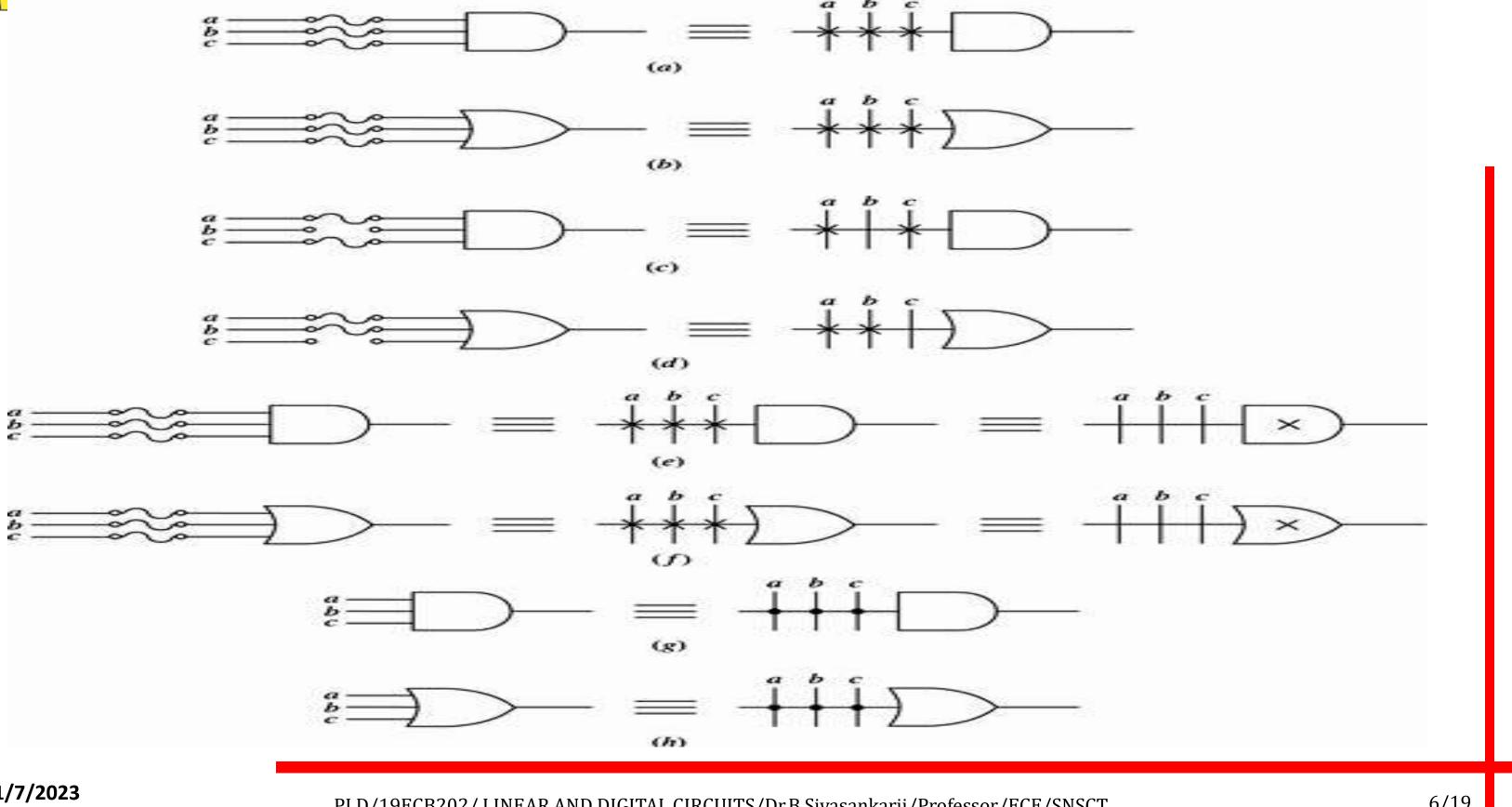

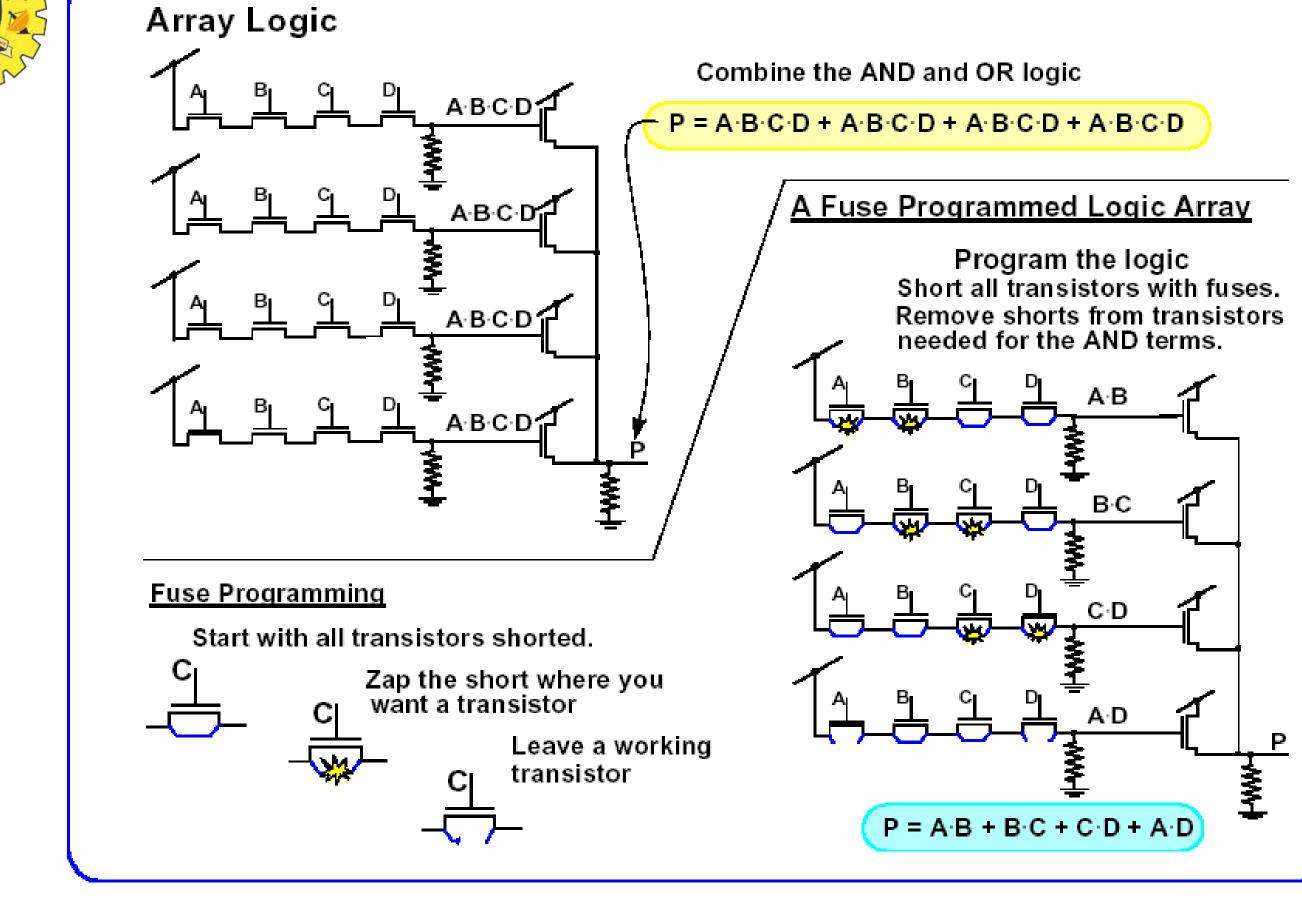

## Programming by blowing fuses.

(a)

(b)

(a) Before programming. (b) After programming.

1/7/2023

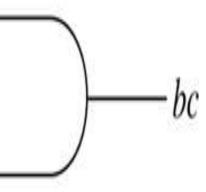

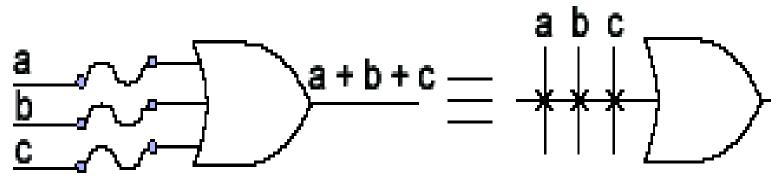

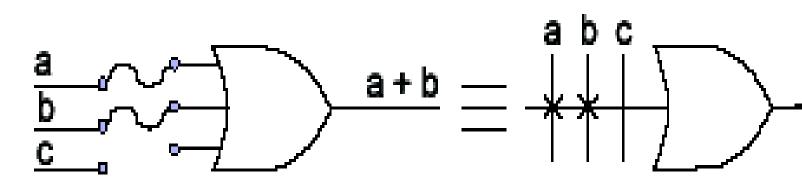

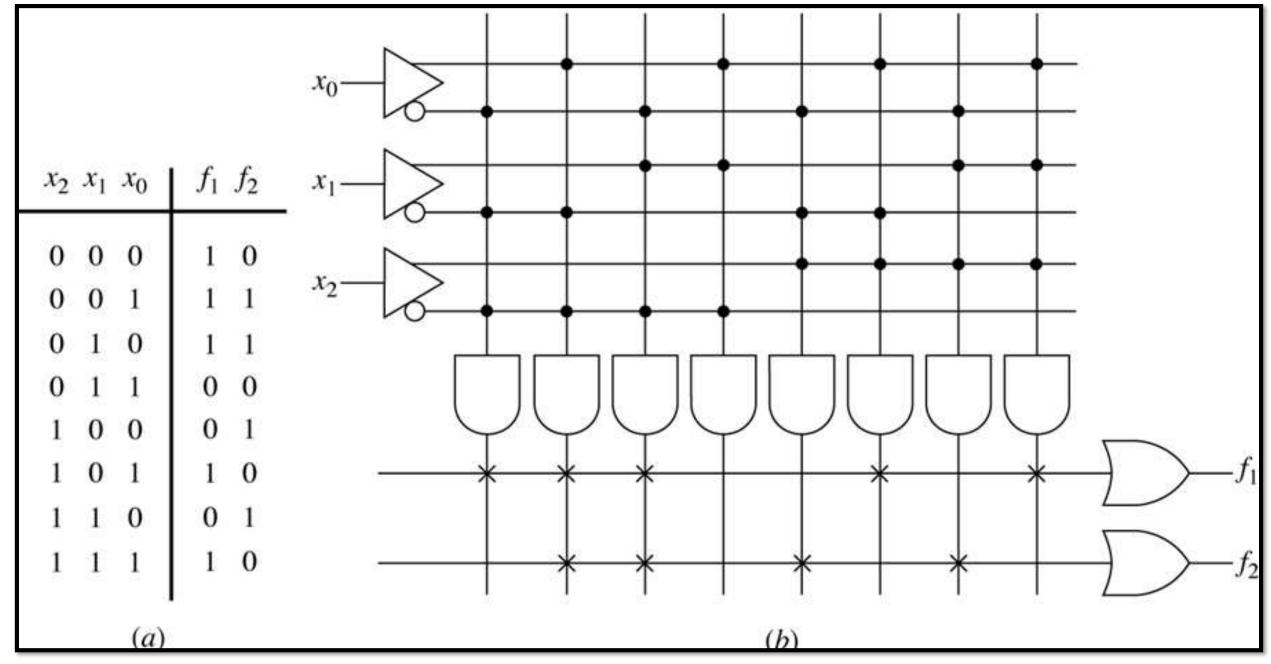

## **OR-** PLD Implementation

OR gate before programming

OR gate after programming

PLD/19ECB202/ LINEAR AND DIGITAL CIRCUITS/Dr.B.Sivasankarii/Professor/ECE/SNSCT

### a+b+c

a+b

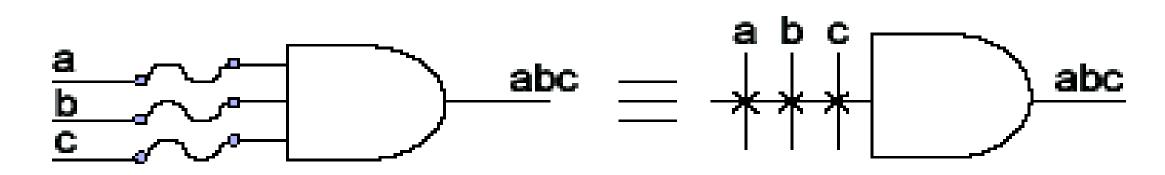

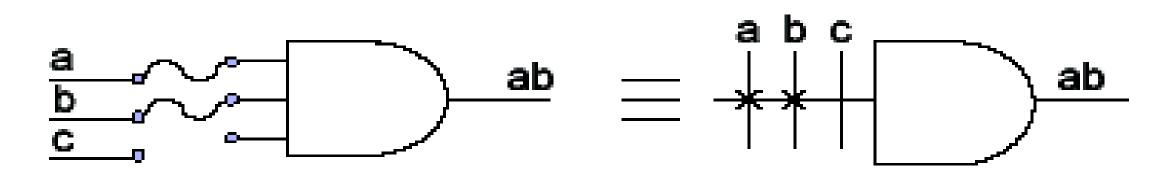

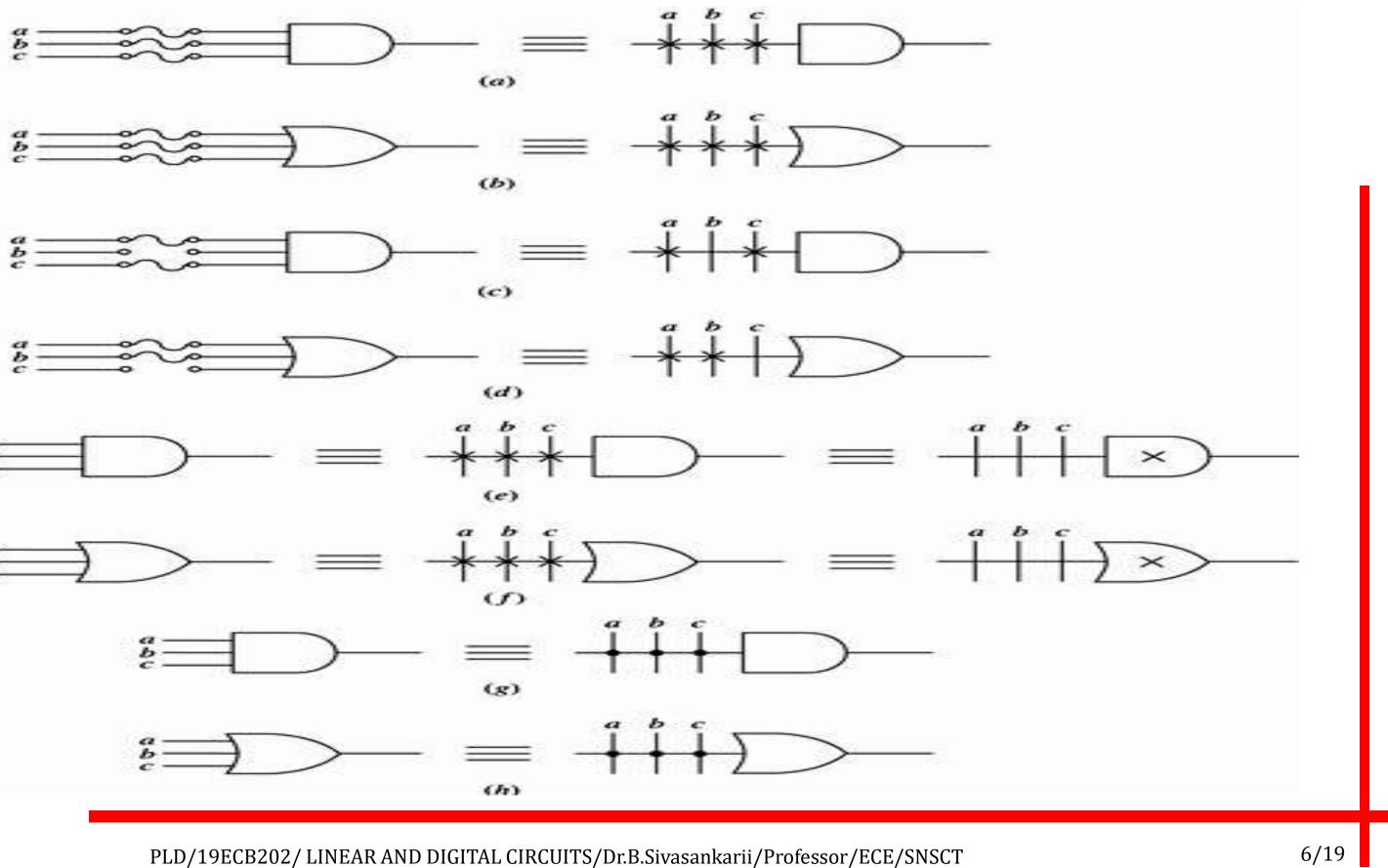

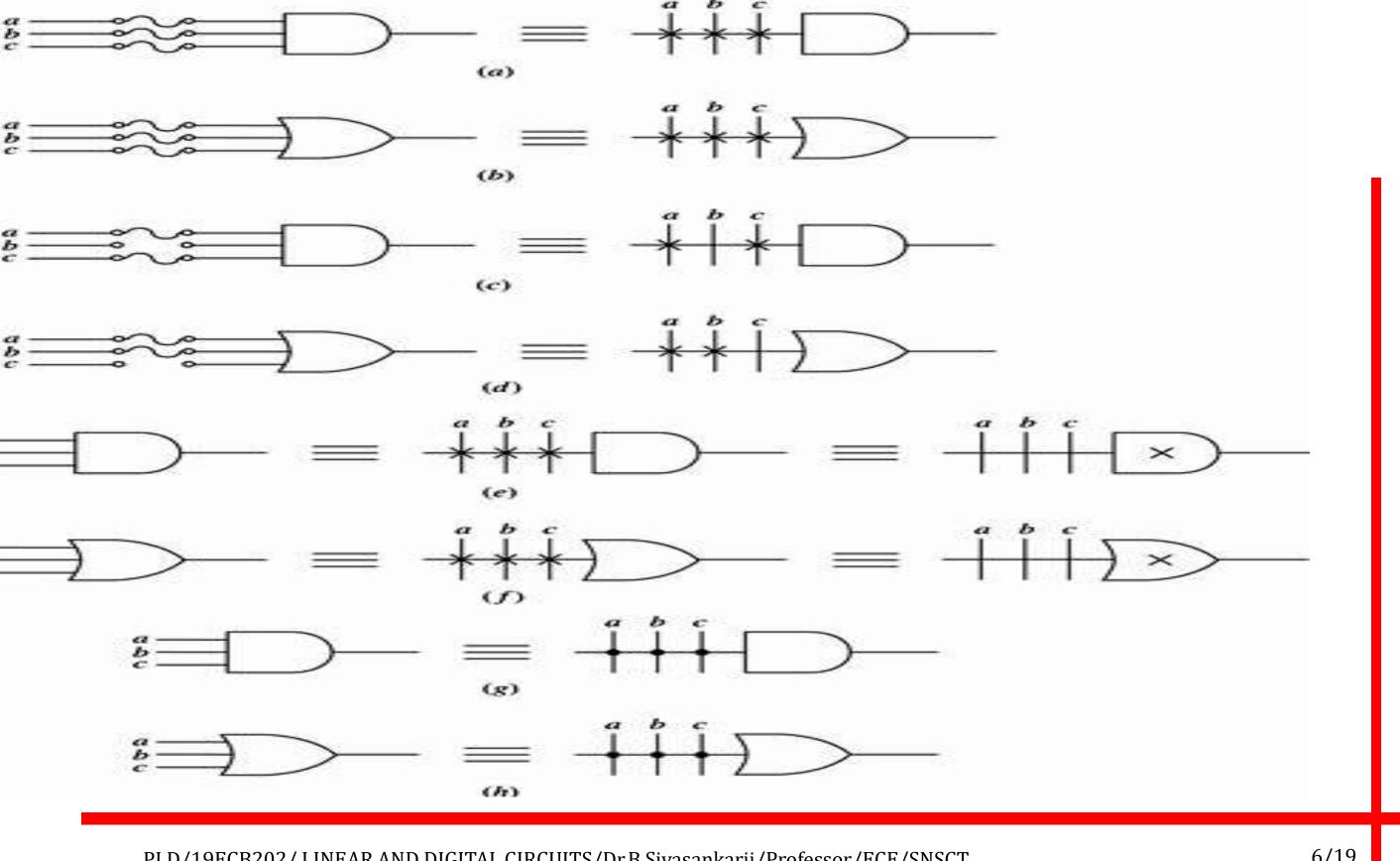

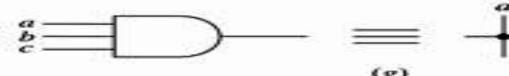

## **AND- PLD Implementation**

AND gate before programming

AND gate after programming

PLD/19ECB202/ LINEAR AND DIGITAL CIRCUITS/Dr.B.Sivasankarii/Professor/ECE/SNSCT

1/7/2023

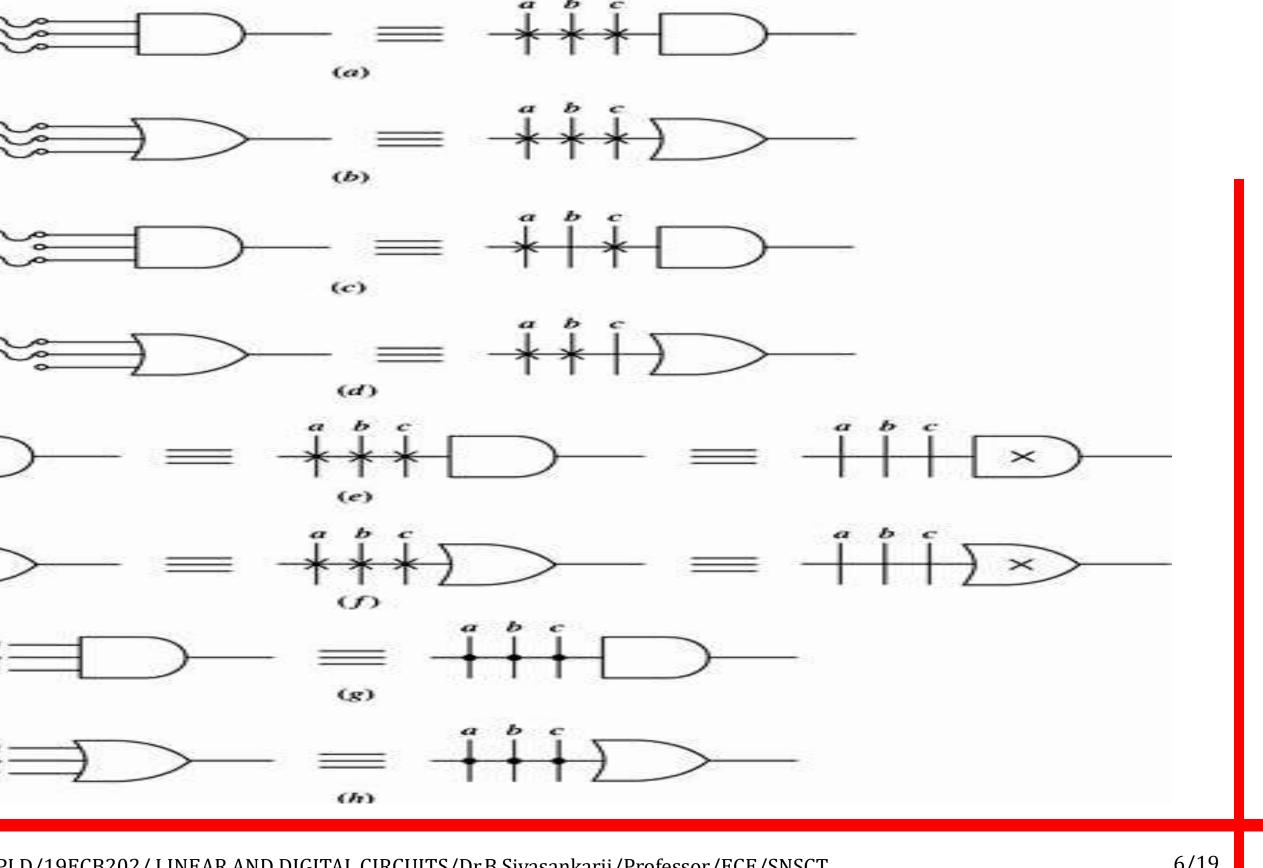

## PLDs

## **PROM** Notation

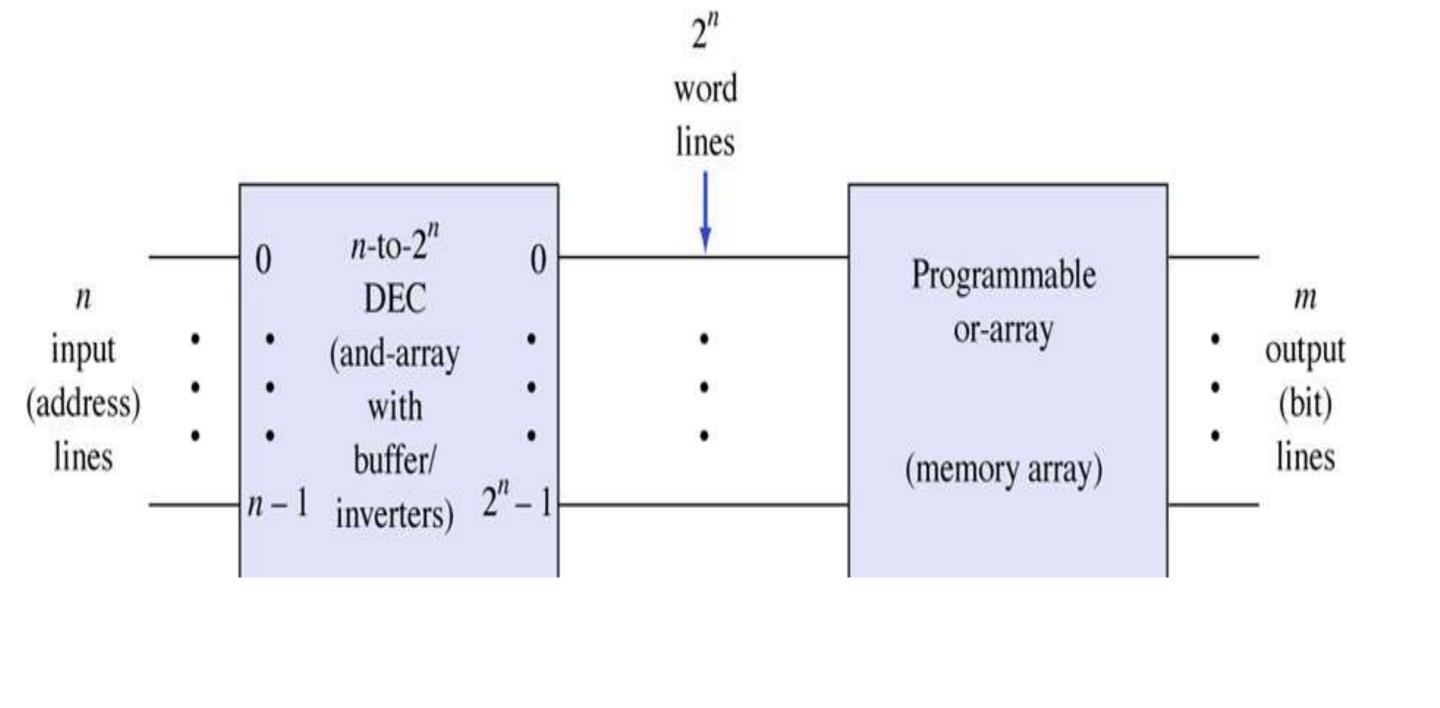

Using a PROM for logic design

(a) Truth table.

(b) PROM realization.

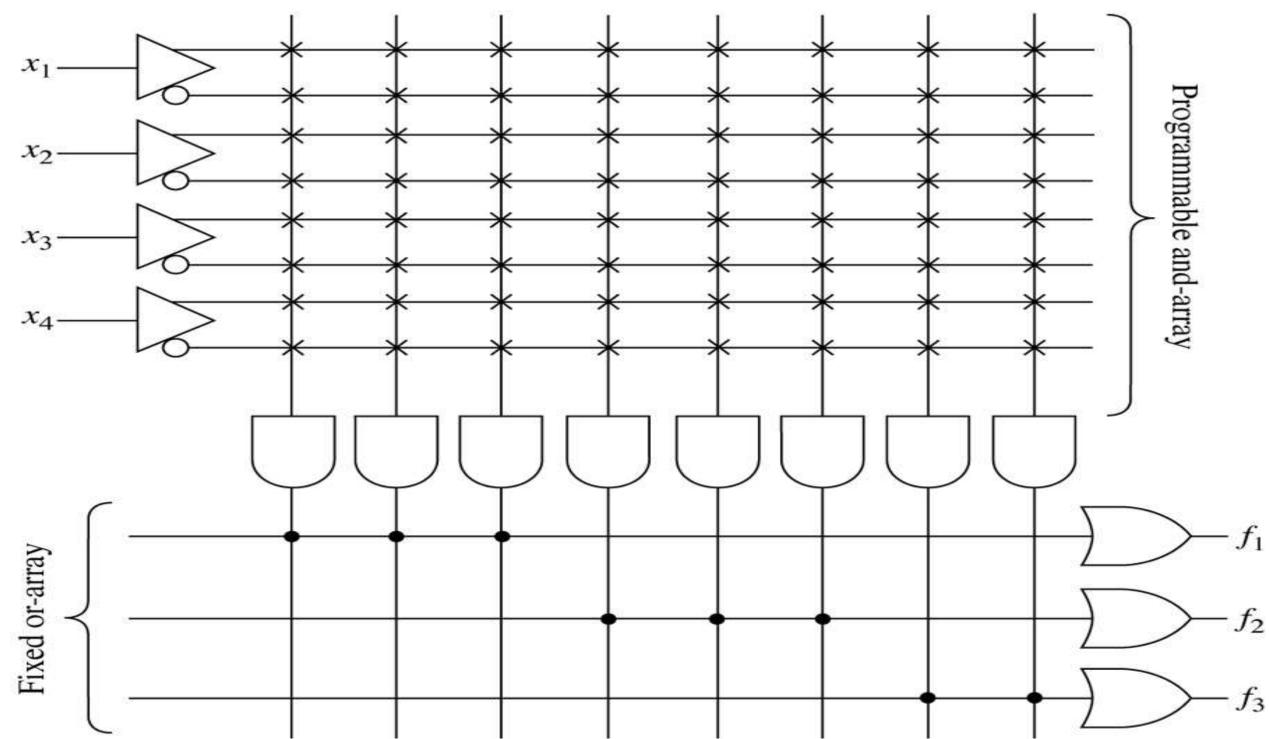

## A simple four-input, three-output PAL device.

1/7/2023

## A simple four-input, three-output PAL device.

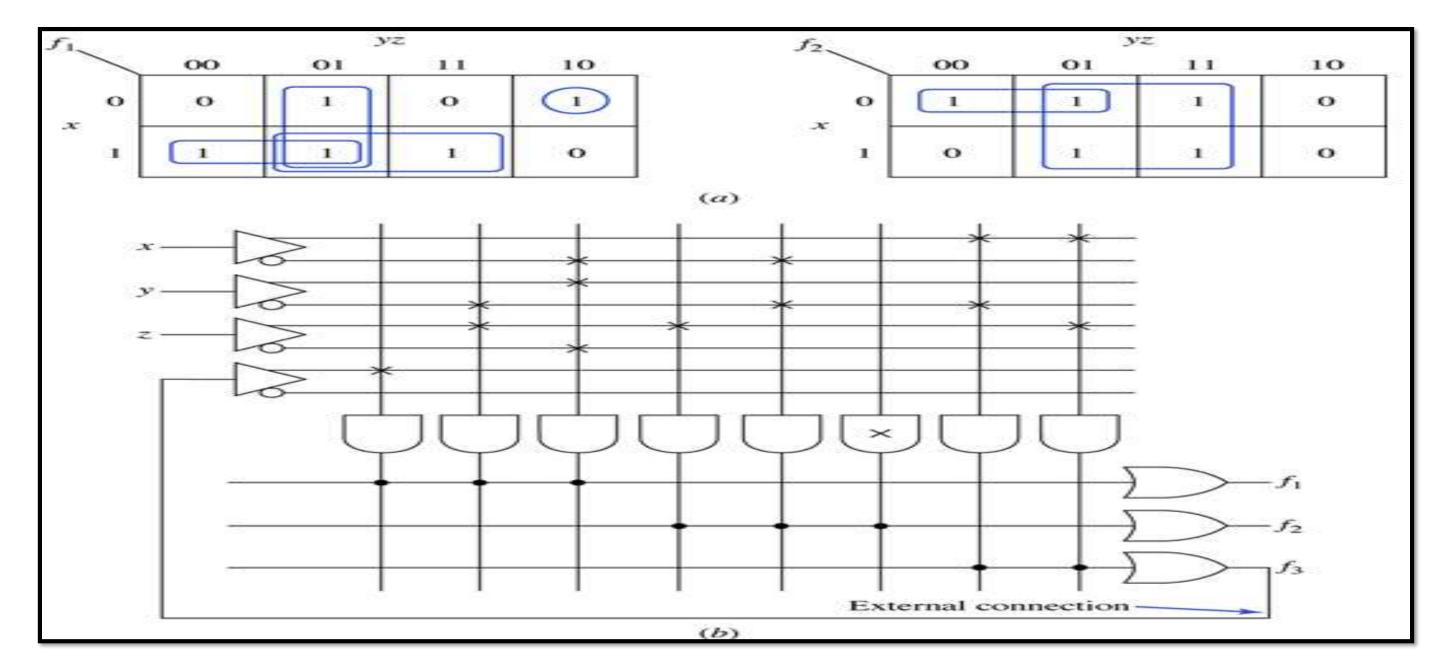

### An example of using a PAL device to realize two Boolean functions.

(a) Karnaugh maps.

1/7/2023

PLD/19ECB202/ LINEAR AND DIGITAL CIRCUITS/Dr.B.Sivasankarii/Professor/ECE/SNSCT

### (b) Realization.

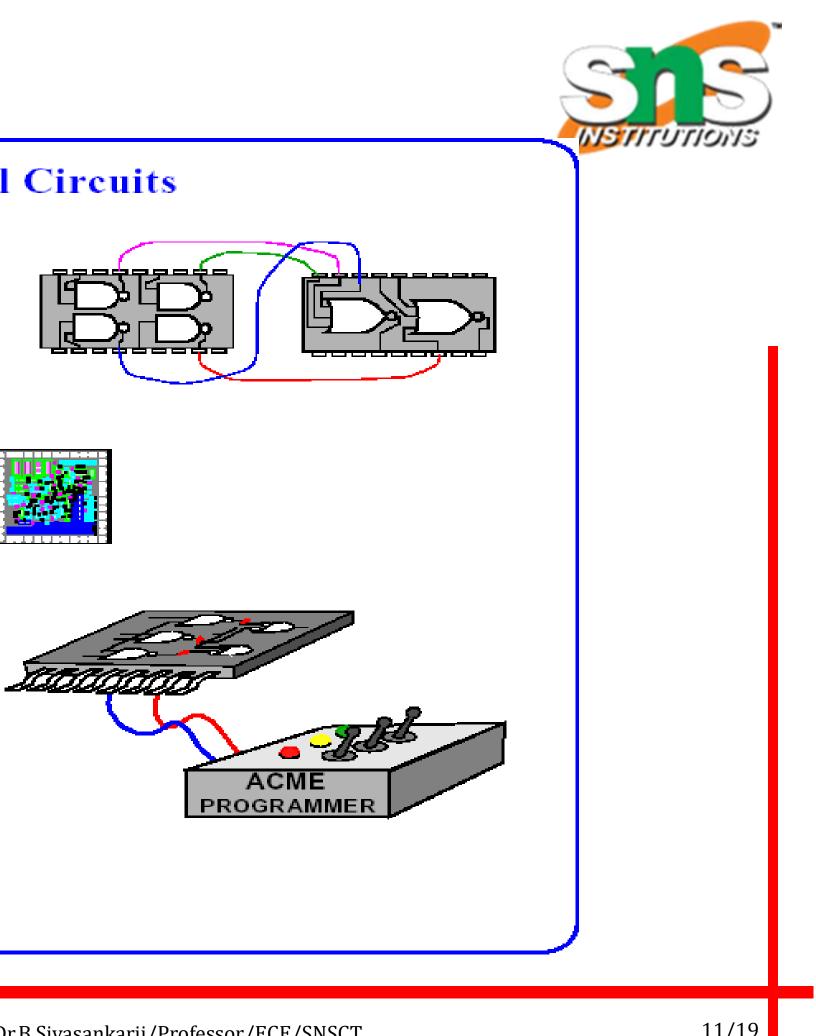

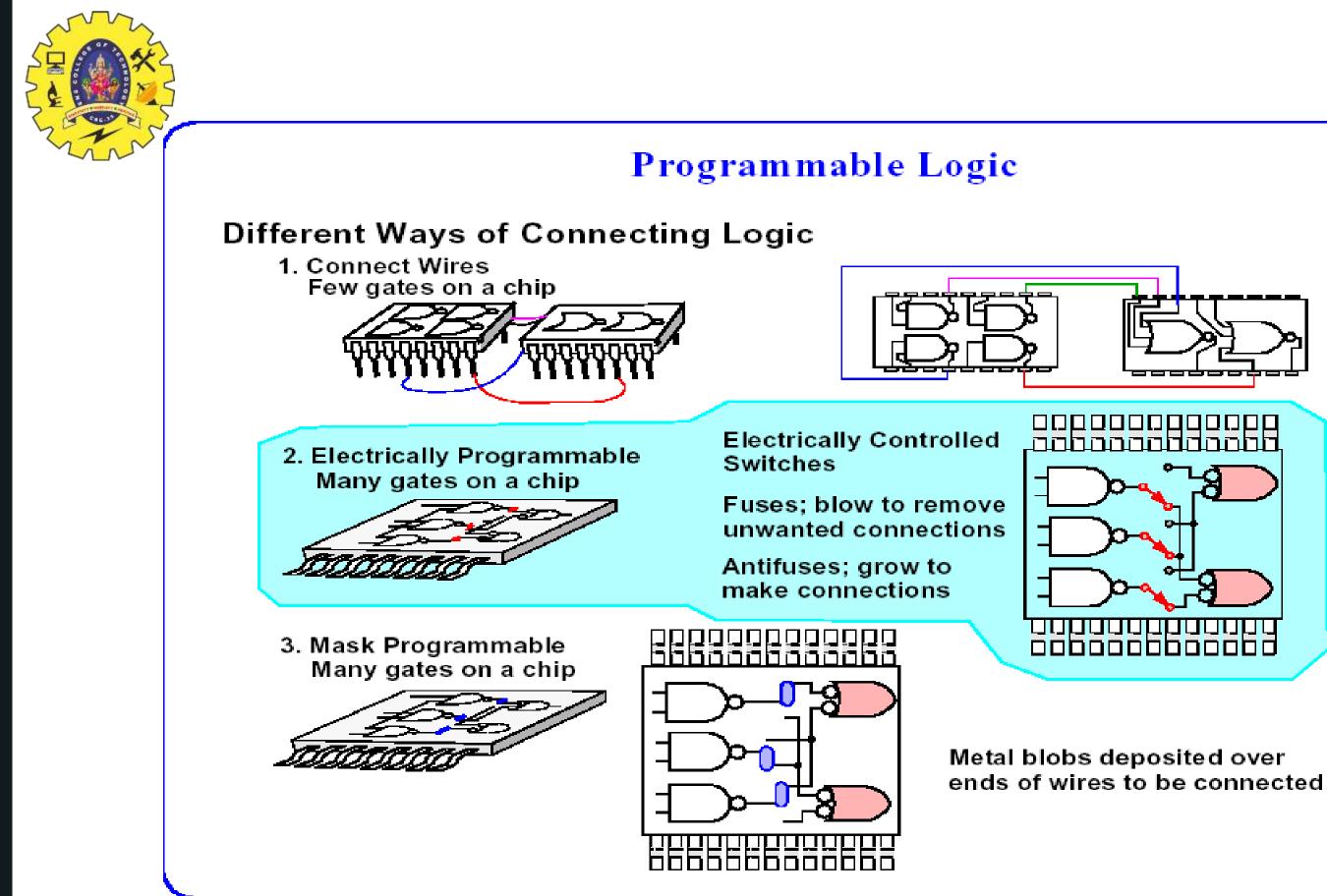

### **Constructing Digital Circuits**

### Hand Wired Circuits

Cirri 1970-85

- Make 2 to 4 silicon gates in a package.

- Connect with wires.

### VLSI circuits

Start with a silicon wafer and make:

- the gates

- the interconnections on top

both made together.

### **Field Programmable circuits**

Start with a silicon wafer and make:

- gates with no connections.

- Make connections later using:

- 1) electrical means

- blow fuses, grow anti fuses

- use memory to hold connections

- deposit metal lines on top of silicon. 2)

### Micro Controllers

PLD/19ECB202/ LINEAR AND DIGITAL CIRCUITS/Dr.B.Sivasankarii/Professor/ECE/SNSCT

## FPGA AND CPLD

- FPGA Field-Programmable Gate Array. 1.

- CPLD Complex Programmable Logic Device 2.

- 3. FPGA and CPLD is an advance PLD.

- Support thousands of gate where as PLD only support hundreds of gates. 4.

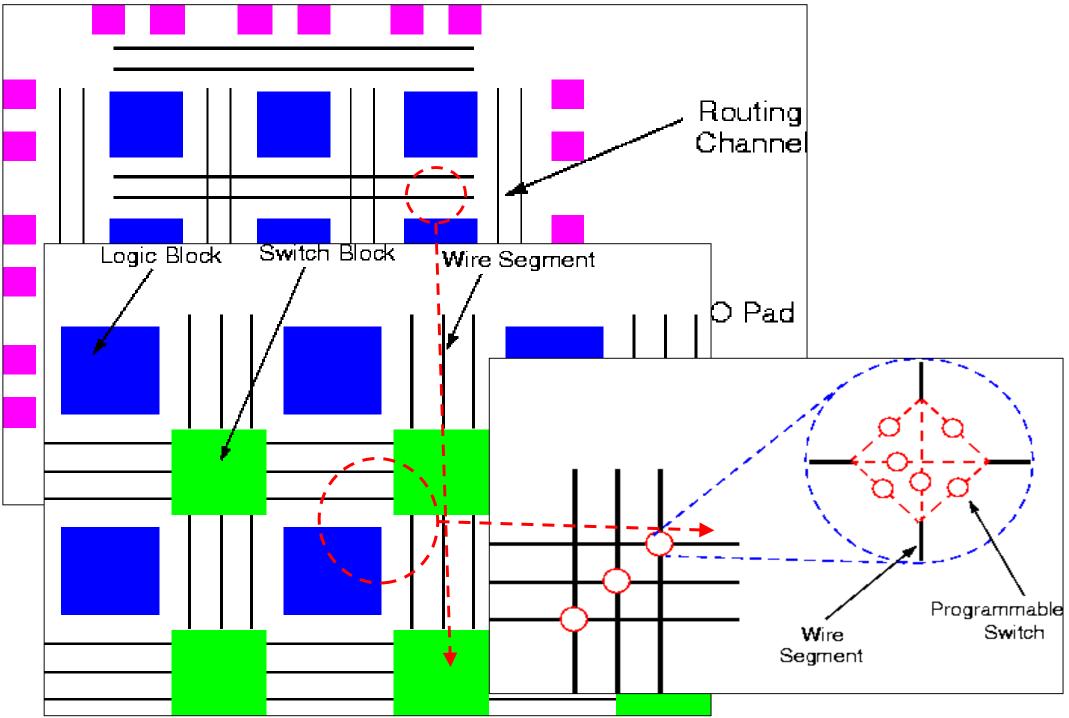

## What is an FPGA?

- Before the advent of programmable logic, custom logic circuits were built at the board level using standard components, or at the gate level in expensive application-specific (custom) integrated circuits.

- FPGA is an integrated circuit that contains many (64 to over 10,000) identical logic cells • that can be viewed as standard components. Each logic cell can independently take on any one of a limited set of personalities.

- Individual cells are interconnected by a matrix of wires and programmable switches.

- A user's design is implemented by specifying the simple logic function for each cell and selectively closing the switches in the interconnect matrix.

- Array of logic cells and interconnect form a fabric of basic building blocks for logic circuits. Complex designs are created by combining these basic blocks to create the desired circuit

1/7/2023

## What is an FPGA?

1/7/2023

# THANK YOU

1/7/2023