# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA - AICTE and Accredited by NAAC - UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

# **16EC303-VLSI DESIGN**

III YEAR/ V SEMESTER

VLSI TESTING & NEEDS//16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SN SCT

### **UNIT 4 –VLSI TESTING**

**TOPIC 1 & 2-VLSI TESTING -NEEDS FOR TESTING**

11/4/202

## **OUTLINE**

- **INTRODUCTION**

- BASIC CONCEPT OF TESTING

- PRINCIPLE OF TESTING  $\bullet$

- DIFFICULTIES IN TESTING  $\bullet$

- HOW TO DO TESTING

- **CIRCUIT MODELING**  $\bullet$

- AUTOMATIC TEST PATTERN GENERATION (ATPG) •

- **DIFFICULTIES IN TEST GENERATION-2 TYPES** ullet

- **TESTABLE DESIGN** ۲

- ACTIVITY  $\bullet$

- **TESTING METHODS**

- NEEDS OF TESTING

- **DESIGN VERIFICATION**  $\bullet$

- YIELD AND REJECT RATE •

- **ELECTRONIC SYSTEM MANUFACTURING**  $\bullet$

- **ELECTRONIC SYSTEM MANUFACTURING**

- **TESTING AND QUALITY** •

- ASSESSMENT  $\bullet$

- SUMMARY & THANK YOU  $\bullet$

# **BASIC CONCEPT OF TESTING**

Testing: To tell whether a circuit is good or bad

**Related fields**

Verification: To verify the correctness of a design

Diagnosis: To tell the faulty site

Reliability: To tell whether a good system will work

correctly or not after some time.

Debug: To find the faulty site and try to eliminate the fault

## **PRINCIPLE OF TESTING**

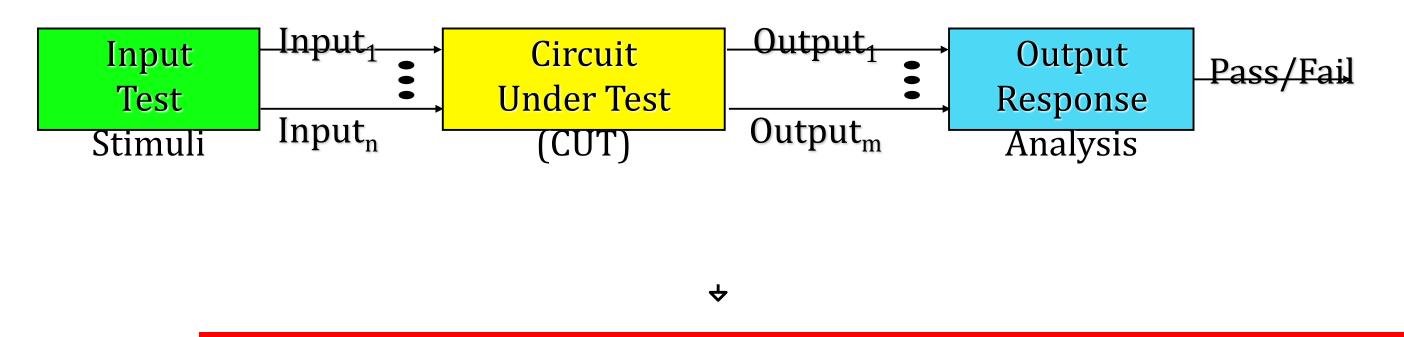

- Testing typically consists of

- Applying set of test stimuli (input patterns, test vectors) to inputs of circuit under test (CUT), and

- Analyzing output responses

- The quality of the tested circuits will depend upon the thoroughness of the test vectors

# **DIFFICULTIES IN TESTING**

- Fault may occur anytime

- Design

Process

Package

Field

- Fault may occur at any place

- VLSI circuit are large

- Most problems encountered in testing are NP-complete

- I/O access is limited

Vss

## **HOW TO DO TESTING**

From designer's point of view:

• Synthesis for testability

VLSI TESTING & NEEDS//16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT

# **CIRCUIT MODELING**

• Functional model--- logic function

- f(x1,x2,...)=...

- Truth table

• Behavioral model--- functional + timing

- f(x1,x2,...)=... , Delay = 10

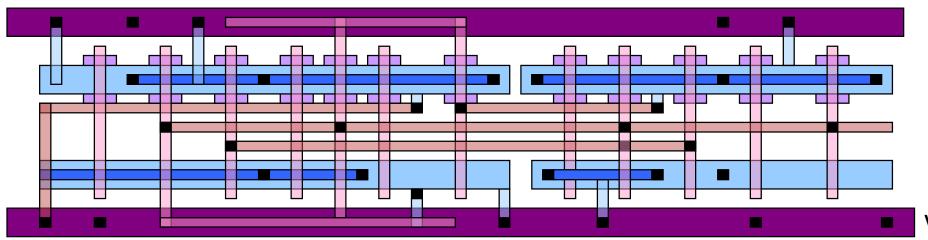

• Structural model--- collection of interconnected components or elements

VLSI TESTING & NEEDS//16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT

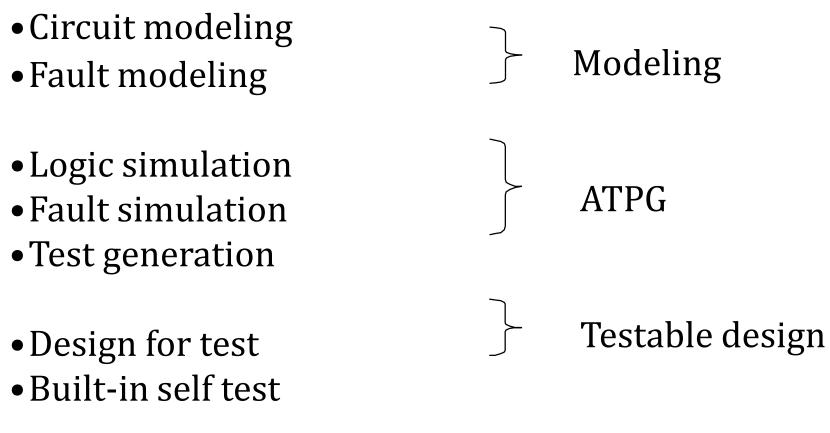

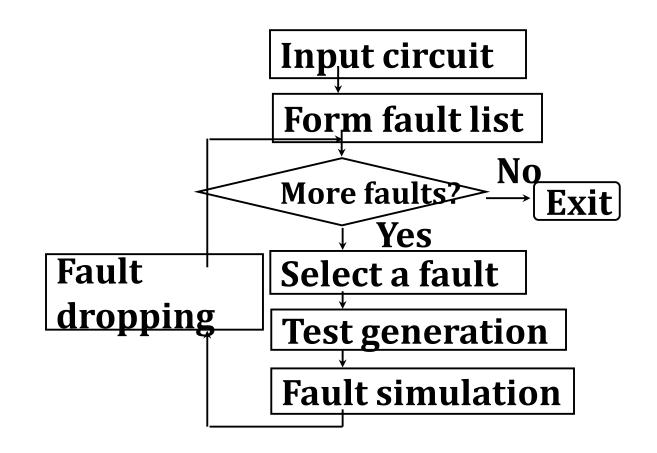

# **AUTOMATIC TEST PATTERN GENERATION**

• ATPG: Given a circuit, identify a set of test vectors to detect all faults under consideration.

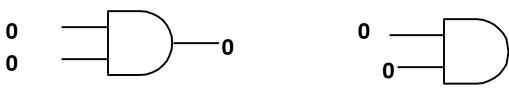

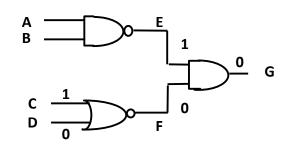

## **TEST GENERATION**

• Given a fault, identify a test to detect this fault

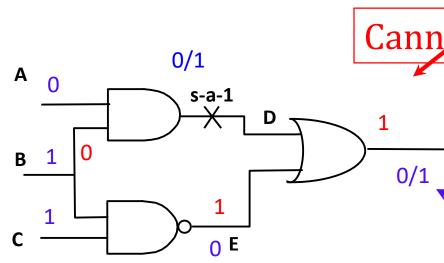

#### **Example:**

To detect D s-a-0, D must be set to 1. Thus A=B=1.

To propagate fault effect to the primary output

E must be 1. Thus C must be 0.

Test vector: A=1, B=1, C=0

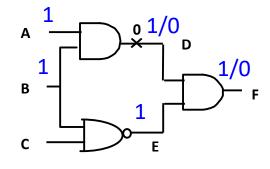

### **DIFFICULTIES IN TEST GENERATION**

**1**. Reconvergent fan-out

11/4/2022

VLSI TESTING & NEEDS//16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT

#### Cannot detect the fault

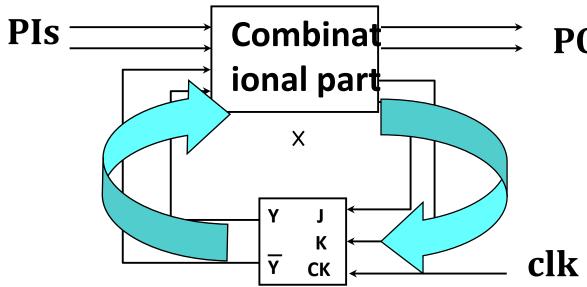

## **DIFFICULTIES IN TEST GENERATION (CONT.)**

2. Sequential test generation

11/4/2022

VLSI TESTING & NEEDS//16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT

## **TESTABLE DESIGN**

- Design for testability (DFT)

- ad hoc techniques

- Scan design

- Boundary Scan

- Built-In Self Test (BIST)

- Random number generator (RNG)

- Signature Analyzer (SA)

- Synthesis for Testability

# **CLASS ROOM ACTIVITY**

#### **Tell about yourself-any four students**

To analyze how confident you are and how you present yourself. The best way to answer this common interview question is to tell the hiring manager about your education and family background.

However, this should not look like your life's story and you should quickly concentrate on sharing a bit about your strengths that build the platform for further discussion about your suitability for the job opening.

#### **Bonus Tips:**

## Don't narrate what is already mentioned in your CV

## Focus more on talking about your achievements and learning

## Keep it short

'How to Answer the "Tell Me About Yourself" Interview Question

## **TESTING METHODS**

- A 32-bit adder --- ATPG

- A 32-bit counter --- Design for testability + ATPG

- A 32MB Cache memory --- BIST

- A 10<sup>7</sup>-transistor CPU --- All test techniques

- An SOC

- •Moore's Law results from decreasing feature size (dimensions)

- -from 10s of  $\mu m$  to 10s of nm for transistors and interconnecting wires

- •Operating frequencies have increased from 100KHz to several GHz

- •Decreasing feature size increases probability of defects during manufacturing process

- •A single faulty transistor or wire results in faulty IC

- •Testing required to guarantee fault-free products

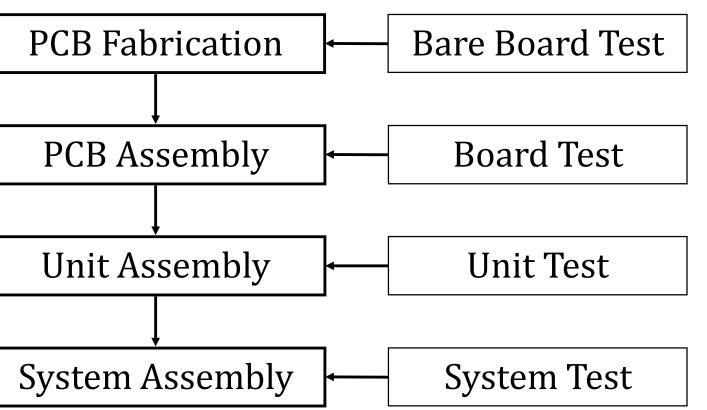

•*Rule of Ten*: cost to detect faulty IC increases by an order of magnitude as we move from: •device  $\rightarrow$  PCB  $\rightarrow$  system  $\rightarrow$  field operation •Testing performed at all of these levels •Testing also used during •Manufacturing to improve yield •Failure mode analysis (FMA) •Field operation to ensure fault-free system operation •Initiate repairs when faults are detected

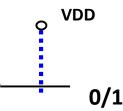

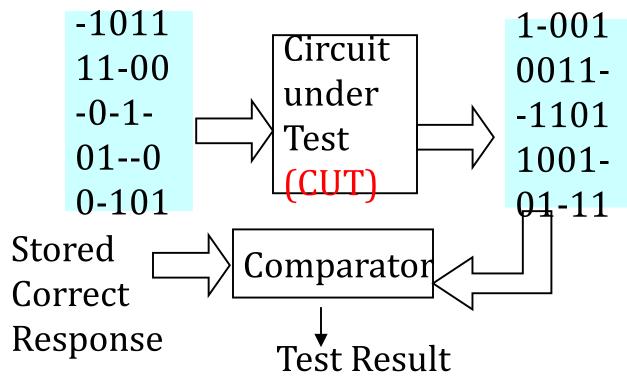

- Testing typically consists of

- Applying set of test stimuli to

- Inputs of *circuit under test* (CUT), and

- Analyzing output responses

- If incorrect (fail), CUT assumed to be faulty

- If correct (pass), CUT assumed to be fault-free

VLSI TESTING & NEEDS//16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT

#### faulty fault-free

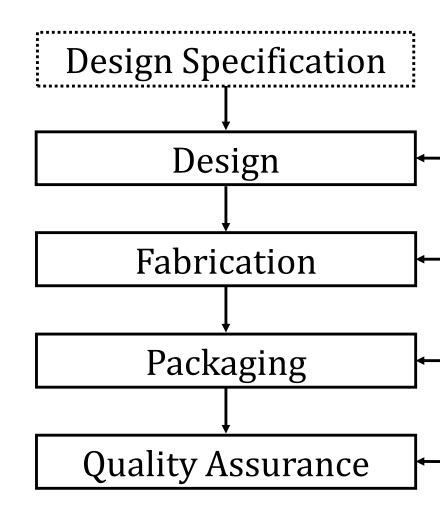

- Design verification targets • design errors

- Corrections made prior to fabrication

- Remaining tests target • manufacturing defects

- A defect is a flaw or physical imperfection that can lead to a fault

#### **Design Verification**

Wafer Test

Package Test

**Final Testing**

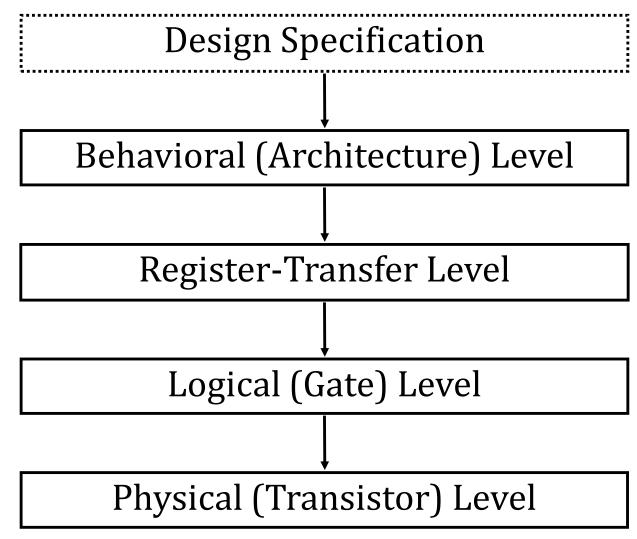

## **DESIGN VERIFICATION**

- Different levels of • abstraction during design

- CAD tools used to synthesize design from RTL to physical level

- Simulation used at various level to test for

- Design errors in behavioral or RTL

- Design meeting system timing requirements after synthesis

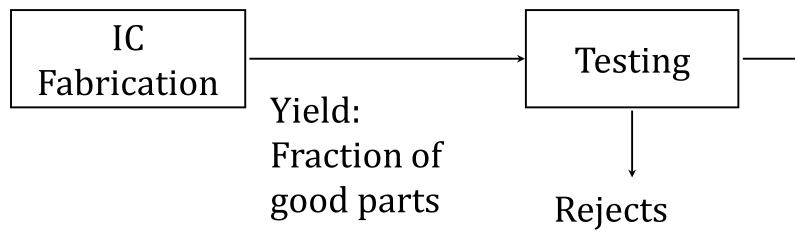

# **YIELD AND REJECT RATE**

- We expect faulty chips due to manufacturing defects  $\bullet$

- Called yield

number of acceptable parts vield = total number of part fabricated

- 2 types of yield loss

- Catastrophic due to random defects

- Parametric due to process variations

- Undesirable results during testing ullet

- Faulty chip appears to be good (passes test)

- Called reject rate

- Good chip appears to be faulty (fails test)

reject rat =

• Due to poorly designed tests or lack of DFT

number offaulty pats passing final test total number of part passingfinal test

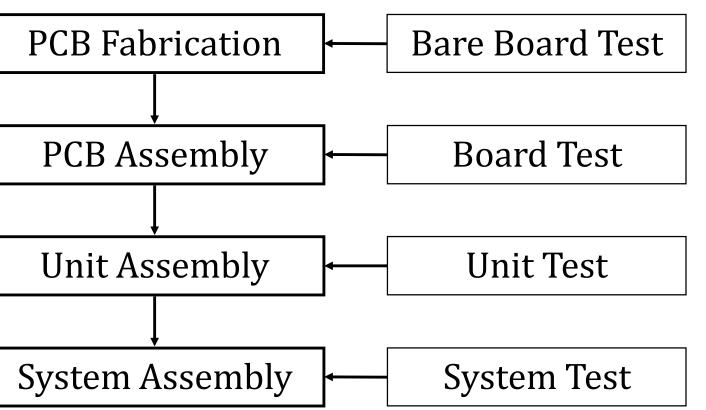

# **ELECTRONIC SYSTEM MANUFACTURING**

- A system consists of

- PCBs that consist of

- VLSI devices

- PCB fabrication similar to VLSI fabrication •

- Susceptible to defects

- Assembly steps also susceptible to defects

- Testing performed at all stages of manufacturing

## **TESTING AND QUALITY**

- Quality of shipped parts is a function of yield Y and the test (fault) coverage T

- Defect level (DL, reject rate in textbook): • fraction of shipped parts that are defective

**Shipped Parts**

Quality: Defective parts per million (DPM)

### ASSESSMENT

- How can you make test generation? 1.

- How can you generate random number? 2.

- List out the needs of testing 3.

- Define Yield and Reject Rate 4.

- 5. Match all correctly

A 32-bit adder --- BIST

A 32-bit counter --- All test techniques

A 32MB Cache memory --- ATPG

A 10<sup>7</sup>-transistor CPU --- Design for testability + ATPG

## **SUMMARY & THANK YOU**

11/4/2022

VLSI TESTING & NEEDS//16EC303-VLSI DESIGN/Dr.B.Sivasankari/Professor/ECE/SNSCT