# SNS COLLEGE OF TECHNOLOGY

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

## **DEPARTMENT OF MECHATRONICS ENGINEERING**

#### **19MCT201 - DESIGN OF DIGITAL CIRCUITS** II YEAR - III SEM

#### **UNIT 2 – COMBINATIONAL CIRCUITS**

**TOPIC 2** – Parallel Adder

# **Parallel binary adder**

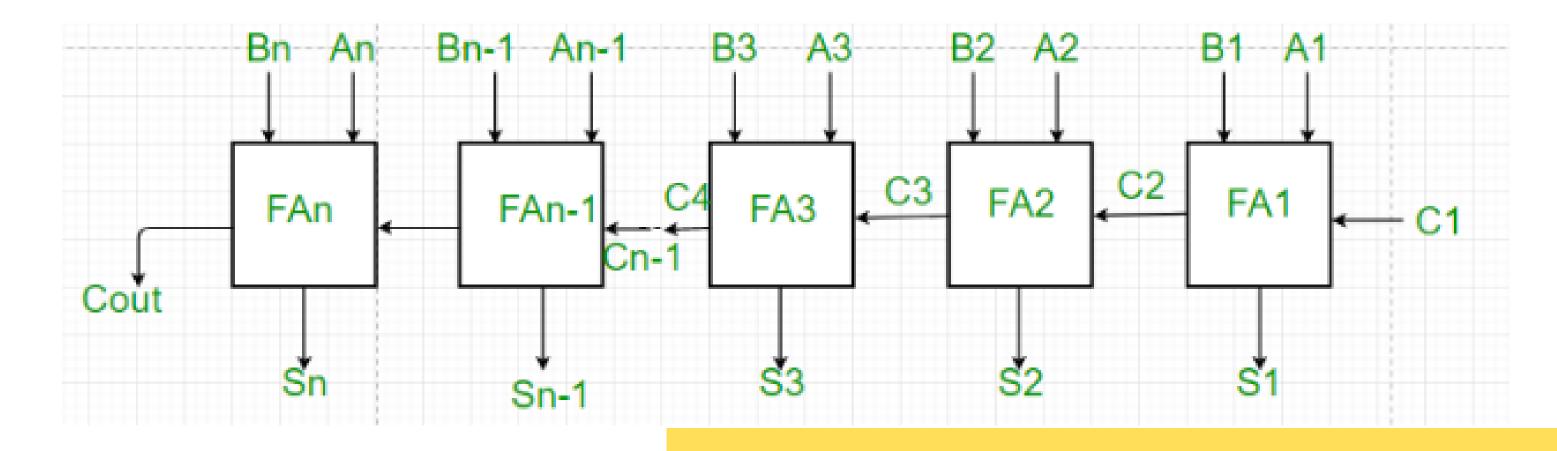

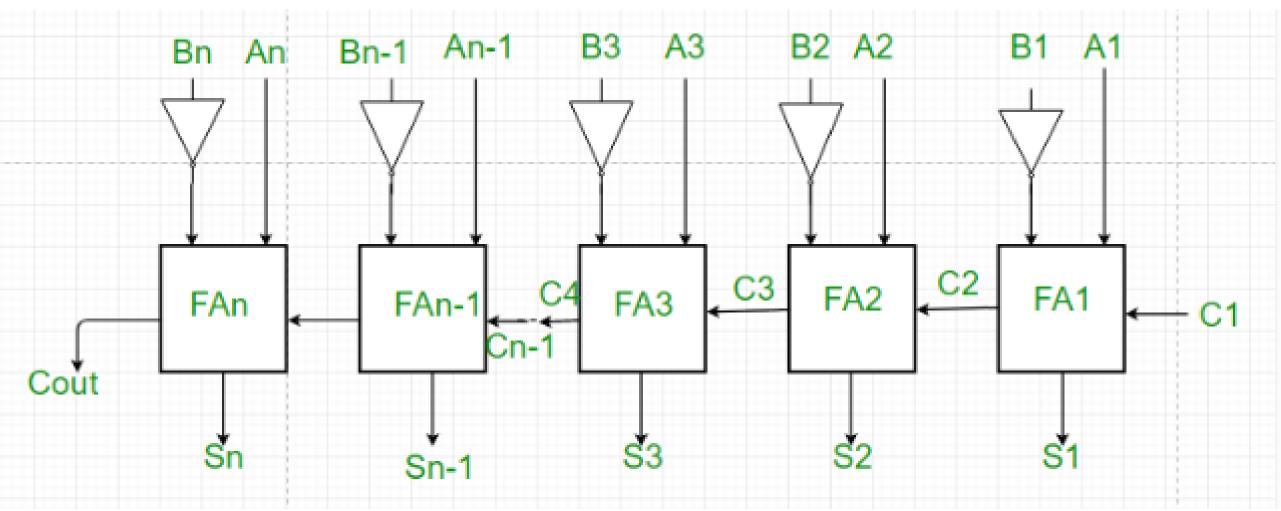

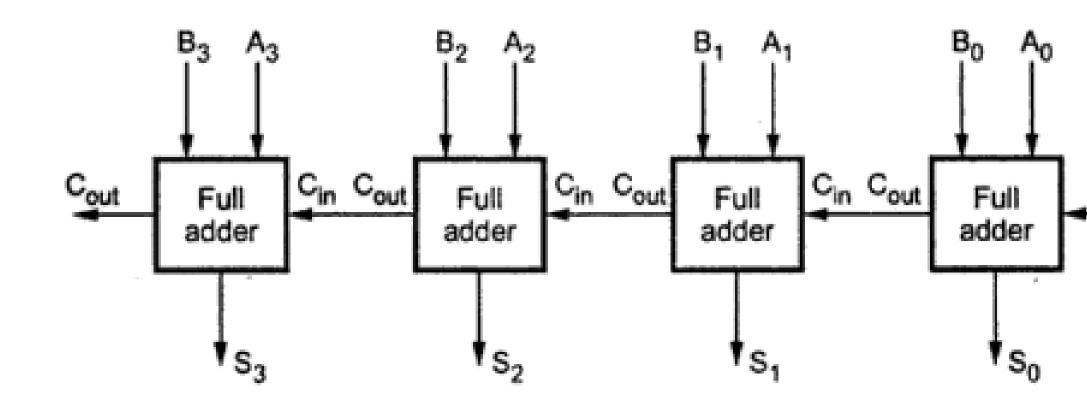

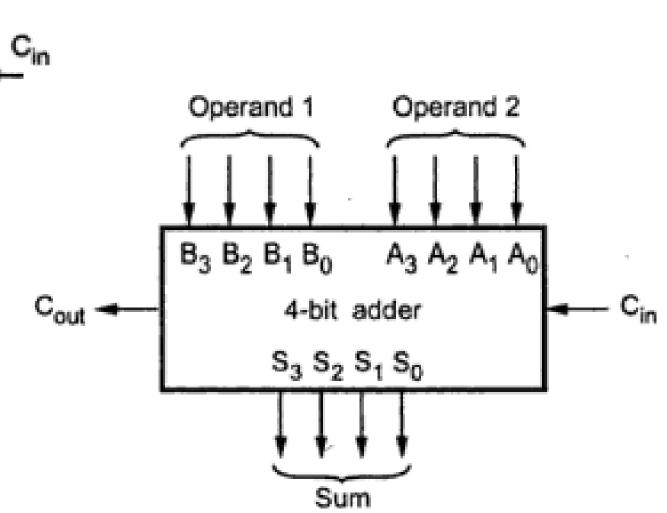

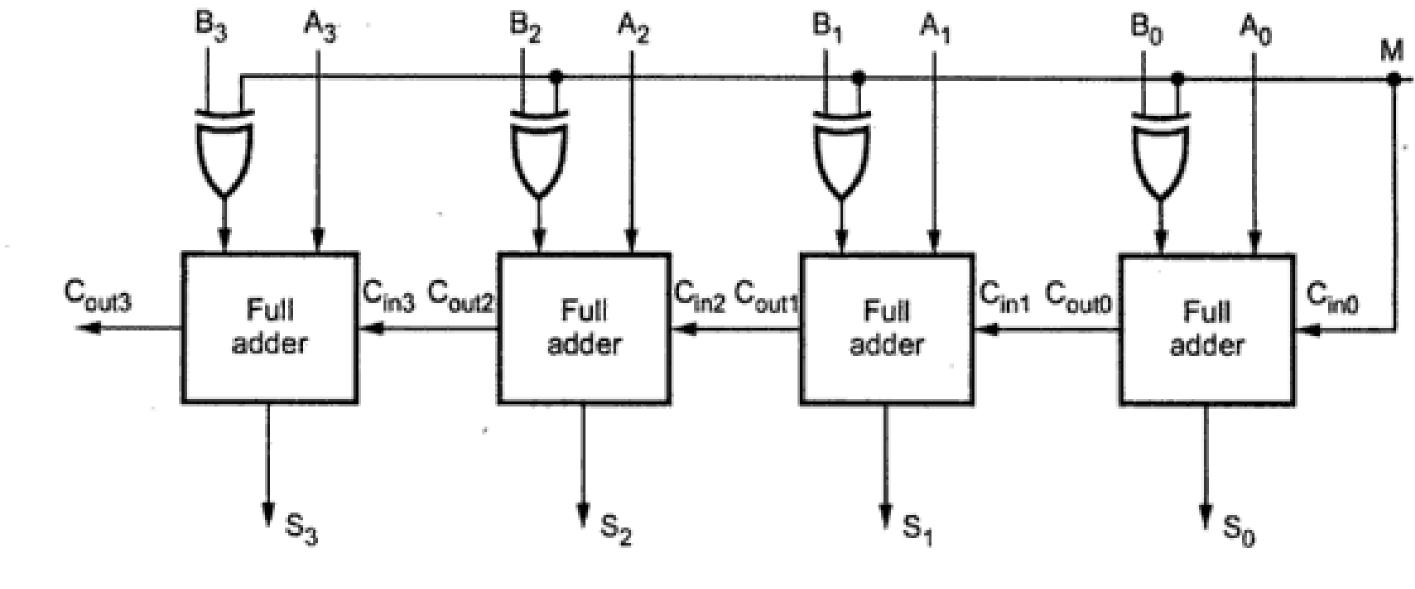

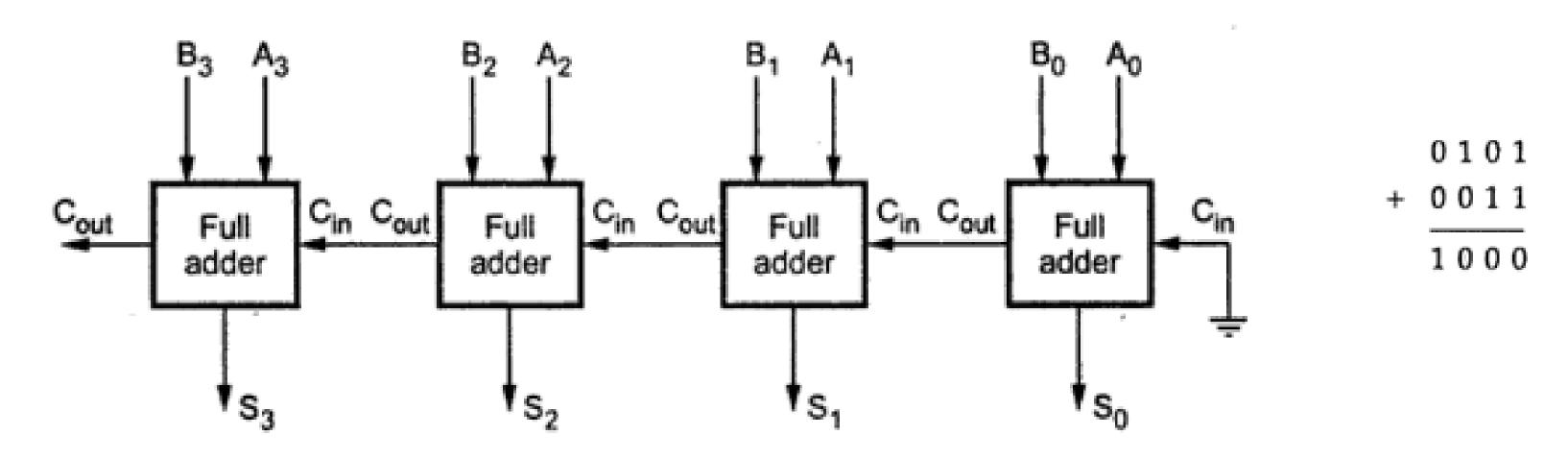

- $\checkmark$  A single full adder performs the addition of two one bit numbers and an input carry. ✓ Parallel Adder for sum of two binary numbers that is greater than one bit in length by operating on corresponding pairs of bits in parallel.

- ✓ It consists of full adders connected in a chain where the output carry from each full adder is connected to the carry input of the next higher order full adder in the chain.

- $\checkmark$  A n bit parallel adder requires n full adders to perform the operation.

- ✓ So for the two-bit number, two adders are needed while for four bit number, four adders are needed and so on.

## **Parallel binary Subtractor**

- ✓ A Parallel Subtractor is a digital circuit capable of finding the arithmetic difference of two binary numbers that is greater than one bit in length by operating on corresponding pairs of bits in parallel.

- ✓ The parallel subtractor can be designed in several ways including combination of half and full subtractors, all full subtractors or all full adders with subtrahend complement input.

## **Design a 4-bit Parallel adder**

## **Adder / Subtractor**

4-bit adder/subtractor

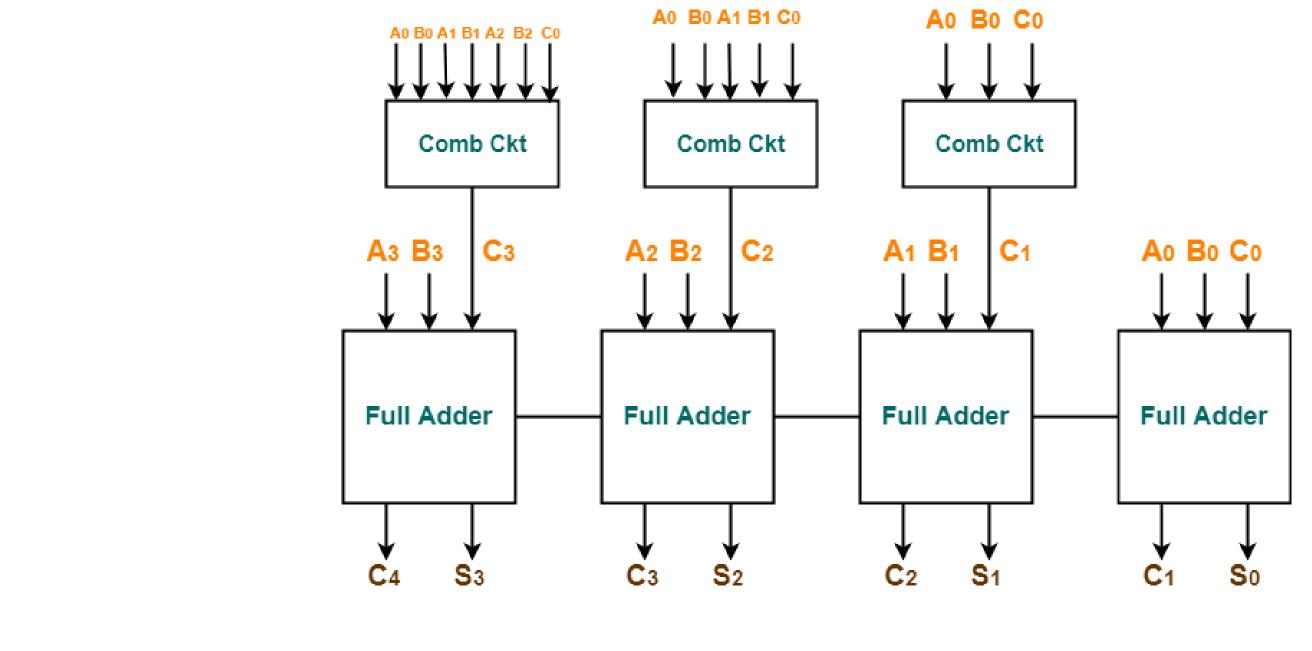

# **Carry Look Ahead Adder**

In a parallel adder circuit, the carry output of each full adder stage is connected to the carry input of the next higher-order stage, hence it is also called as **ripple carry type adder.** In such adder circuits, it is not possible to produce the sum and carry outputs of any stage until the input carry occurs. So there will be a considerable time delay in the addition process, which is known as, carry propagation delay.

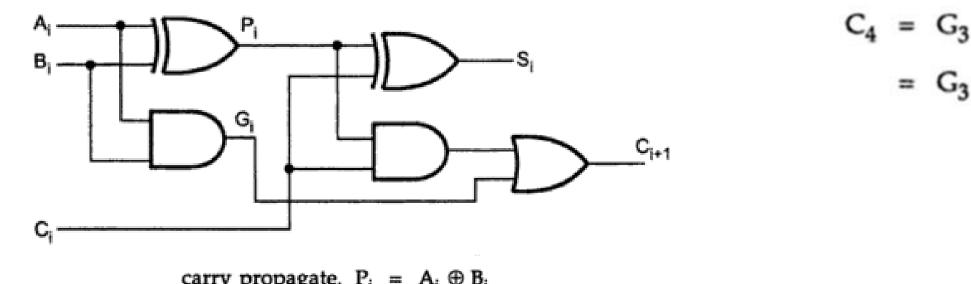

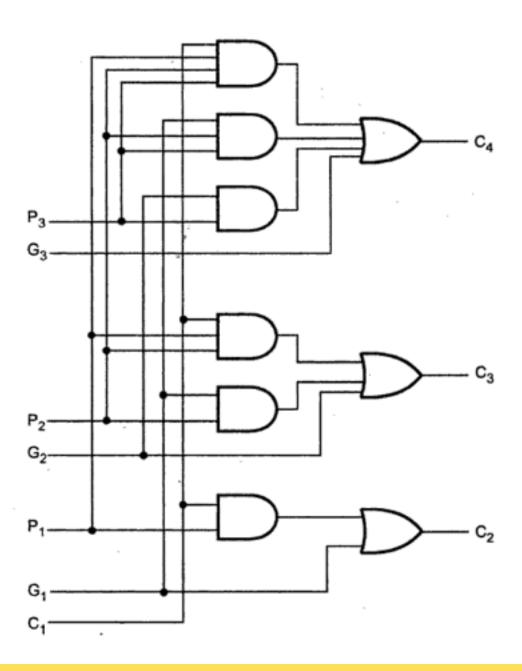

### **Carry Look Ahead Adder**

Carry Look Ahead Adder Logic Diagram

#### **Look Ahead Adder**

carry propagate.  $P_i = A_i \oplus B_i$ carry generate  $G_i = A_i B_i$

The output sum and carry can be expressed as

$$S_i = P_i \oplus C_i$$

$C_{i+1} = G_i + P_i C_i$

$C_2 = G_1 + P_1 C_1$

$C_3 = G_2 + P_2 C_2 = G_2 + P_2 (G_1 + P_1 C_1)$

$= G_2 + P_2G_1 + P_2 P_1C_1$

$C_4 = G_3 + P_3 C_3 = G_3 + P_3 (G_2 + P_2 G_1 + P_2 P_1 C_1)$ = G\_3 + P\_3 G\_2 + P\_3 P\_2 G\_1 + P\_3 P\_2 P\_1 C\_1

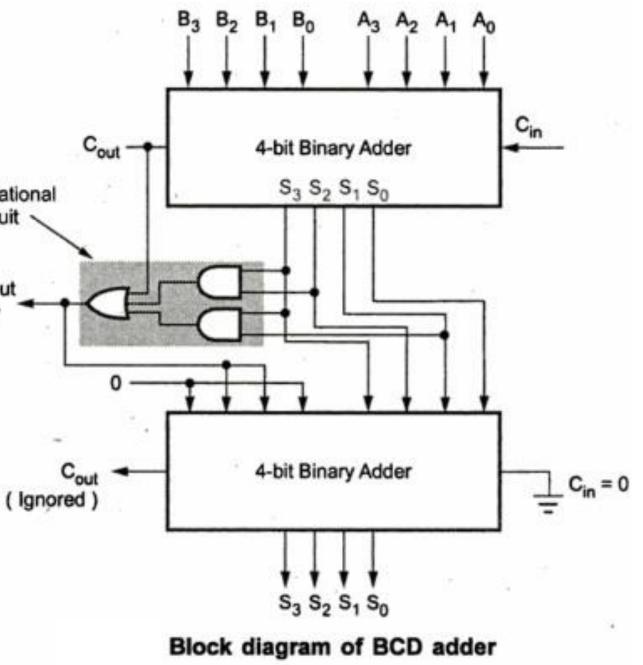

### **BCD** adder

#### each BCD digit is represented as a 4-bit binary number.

| 5    | 2     | 6    |

|------|-------|------|

| Ť    | 1     | L    |

| 0101 | 0.010 | 0110 |

The addition of two BCD numbers can be best understood by considering cases that occur when two BCD digits are added.

- 1. Add two BCD numbers using ordinary binary addition.

- 2. If four-bit sum is equal to or less than 9, no correction is needed. The sum is in proper BCD form.

- 3. If the four-bit sum is greater than 9 or if a carry is generated from the four-bit sum, the sum is invalid.

- 4. To correct the invalid sum, add 0110<sub>2</sub> to the four-bit sum. If a carry results from this addition, add it to the next higher-order BCD digit.

| the t | hree |

|-------|------|

|-------|------|

| П | l |  |

|---|---|--|

|   |   |  |

|   |   |  |

|   |   |  |

| 100.25         | Inp | uts            | 1,000          | Output |

|----------------|-----|----------------|----------------|--------|

| S <sub>3</sub> | S2  | S <sub>1</sub> | S <sub>0</sub> | Y      |

| 0              | 0   | 0              | 0              | 0      |

| 0              | 0   | 0              | 1              | 0      |

| 0              | 0   | 1              | 0              | 0      |

| 0              | 0   | 1              | . 1            | 0      |

| 0              | 1   | 0              | 0              | 0      |

| 0              | 1   | 0              | 1              | 0      |

| 0              | . 1 | 1              | 0              | 0      |

| 0              | 1   | 1              | 1              | 0      |

| 1              | 0   | 0              | 0              | 0      |

| 1              | 0   | 0              | 1              | 0      |

| 1              | 0   | 1              | 0              | 1      |

| 1              | 0   | 1              | 1              | 1.     |

| 1              | 1   | 0              | 0              | 1      |

| 1              | 1   | 0              | 1              | 1      |

| 1              | 1   | 1              | 0              | 1      |

| 1              | 1   | 1              | 1              | 1      |

### **BCD** adder

Thus to implement BCD adder we require :

- 4-bit binary adder for initial addition. ۰

- Logic circuit to detect sum greater than 9 and ۰

- One more 4-bit adder to add  $0110_2$  in the sum if sum is greater than 9 o ٠ is 1.

Combinational circuit

Output carry

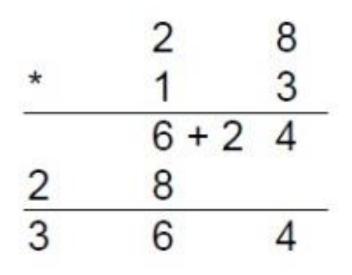

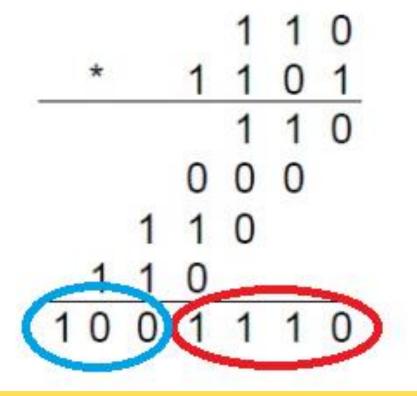

# **Binary Multiplier**

A binary multiplier is a combinational logic circuit used **in digital systems to perform the multiplication of two binary numbers**. In multiplication process, the number which is to be multiplied by the other number is called as multiplicand and the number multiplied is called as multiplier.

Types:

- 1. Partial product addition and shifting

- 2. Parallel multipliers

$$0 \times 0 = 0$$

$0 \times 1 = 0$

$1 \times 0 = 0$

$1 \times 1 = 1$

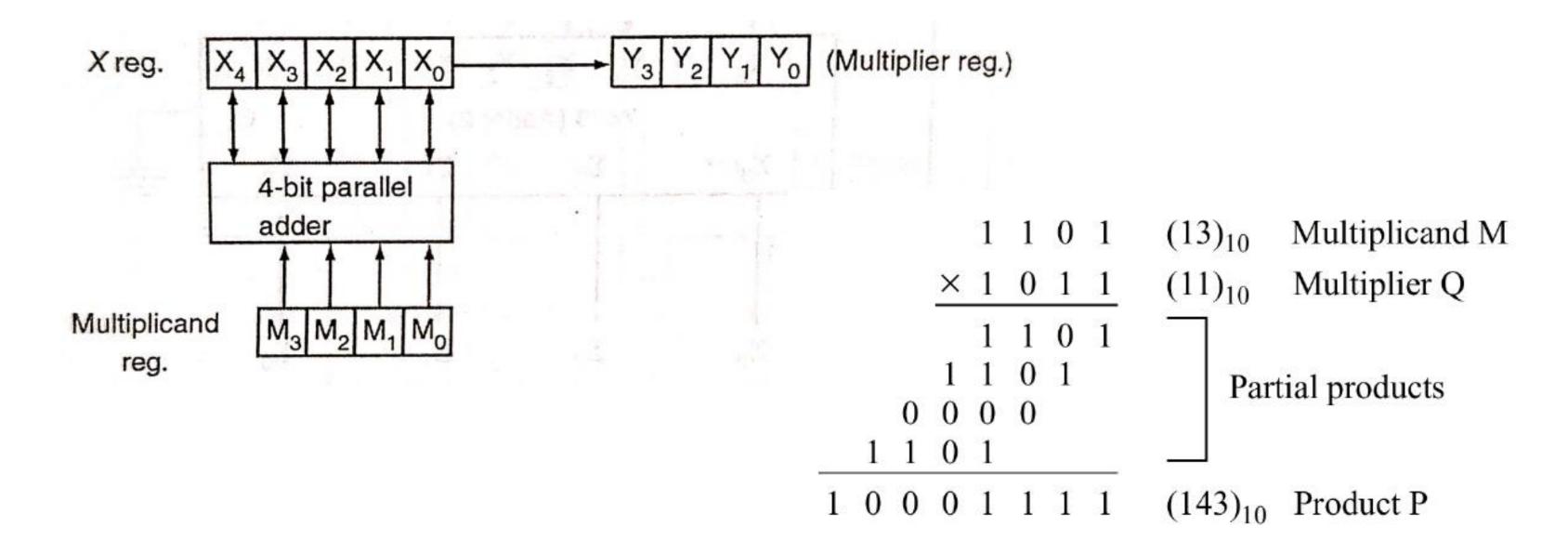

# **Partial Product and Shifting**

This manual multiplication approach can be implemented by using 4-bit adder, four registers (X, Y, C and M) and shift and control logic.

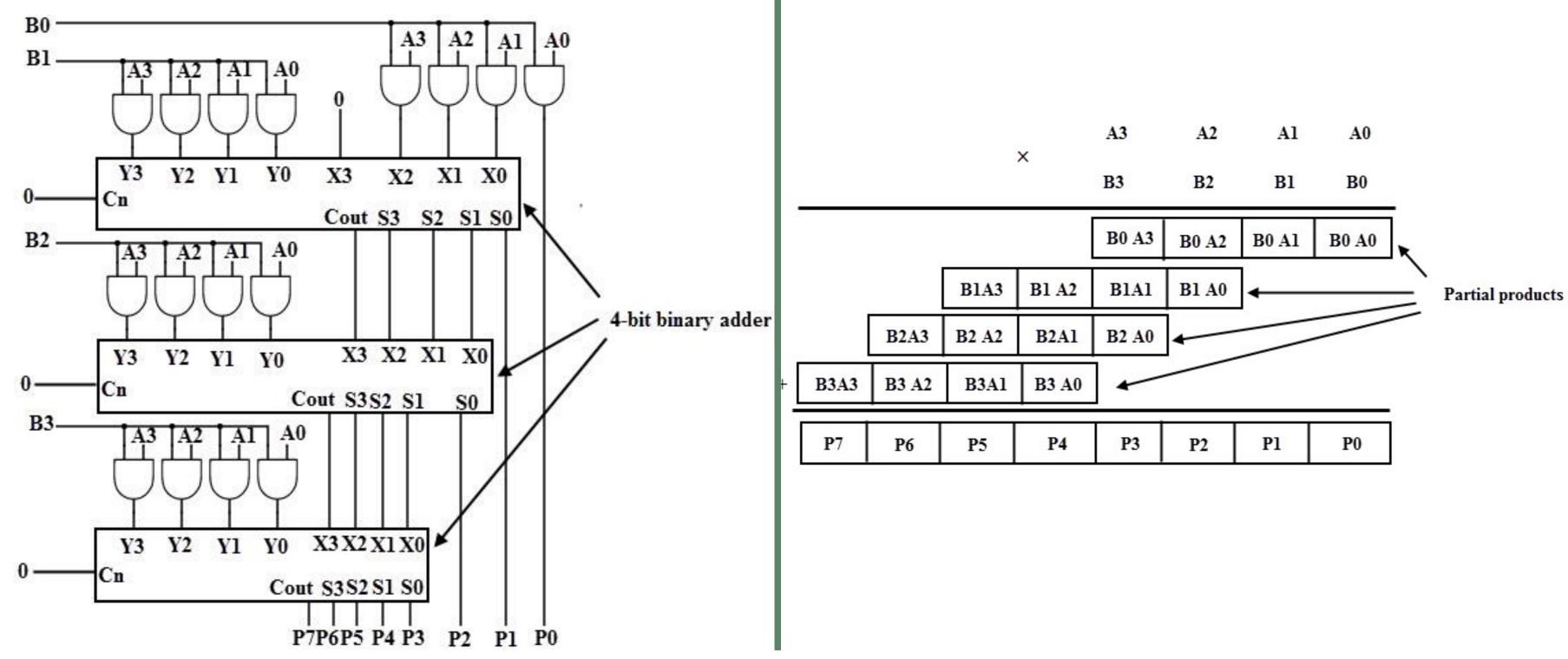

### **Parallel Multiplier**

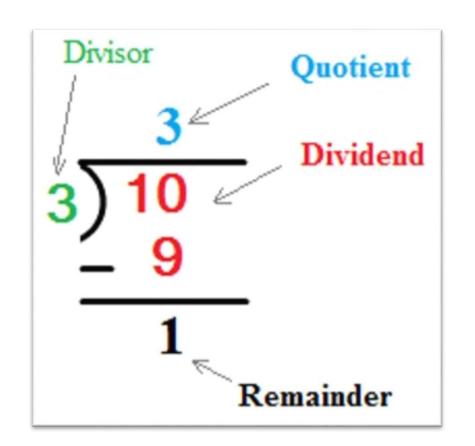

# **Binary Divider**

The binary division is one of the important operations of binary arithmetic. A binary number system or base-two is a counting technique that uses two digits: 0 and 1, and represents the number with the base 2.

| Quotient |     | 111    |

|----------|-----|--------|

| Divisor  | 110 | 101010 |

|          |     | -110   |

|          |     | 1001   |

|          |     | -110   |

|          |     | 110    |

|          |     | -110   |

| Remaind  | er  | 0      |

Dividend

$$0 - 0 = 0$$

$1 - 0 = 1$

$1 - 1 = 0$

$10 - 1 = 1$

## **Binary Divider**

Dividend reg. Y<sub>3</sub>Y<sub>2</sub>Y<sub>1</sub>Y<sub>0</sub>  $X_3 X_2 X_1 X_0$ X reg. 4-bit adder/subtractor Divisor  $D_3 D_2 D_1 D_0$ reg.

Divisor 1010 (d=10)

The 1st subtraction

s<sup>(0)</sup>

The 2nd subtraction

s<sup>(1)</sup>

The 3rd subtraction

s<sup>(2)</sup>

The 4th subtraction

s<sup>(3)</sup>

The 5th subtraction

s<sup>(4)</sup>

| 10011                           | Quotient (q=19)  |

|---------------------------------|------------------|

| 1100 0101                       | Dividend (z=197) |

| 1010                            |                  |

| 0 0100 101                      |                  |

| 0000                            | _                |

| <u>0</u> 01001 01               |                  |

| 0000                            | _                |

| <u>00</u> 1001 <mark>0</mark> 1 |                  |

| 1010                            |                  |

| <u>000</u> 10001                |                  |

| 1010                            | _                |

| <u>0000</u> 0111                | Remainder (s=7)  |

# References

- <u>https://brilliant.org/wiki/de-morgans-laws/</u>

- <u>https://circuitglobe.com/demorgans-theorem.html</u>

- <u>https://www.electrical4u.com/</u>