# UNIT III PROCESSOR AND PIPELINING

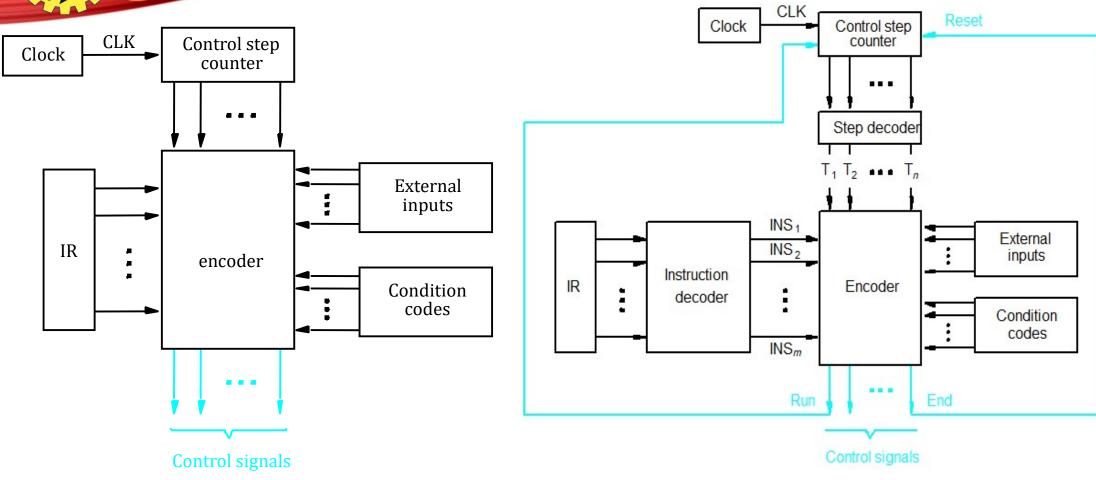

Fundamental concepts – Execution of a complete instruction – Multiple bus organization – **Hardwired control** – Micro programmed control – Pipelining: Basic concepts – Data hazards – Instruction hazards – Influence on Instruction sets – Data path and control consideration.

#### **Recap the previous Class**

A.Aruna / AP / IT / SEM 2 / COA

#### **Overview**

- To execute instructions, the processor must have some means of generating the control signals needed in the proper sequence.

- Two categories: hardwired control and microprogrammed control

- Hardwired system can operate at high speed; but with little flexibility.

A.Aruna / AP / IT / SEM 2 / COA 26-10-2022

#### **Control Unit Organization**

A.Aruna / AP / IT / SEM 2 / COA 26-10-2022

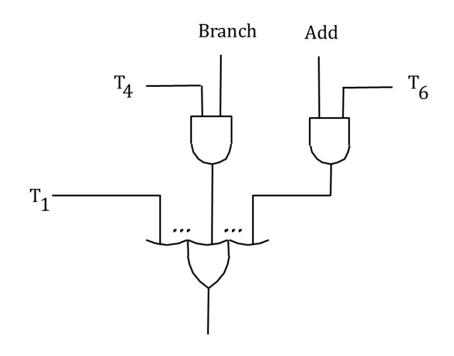

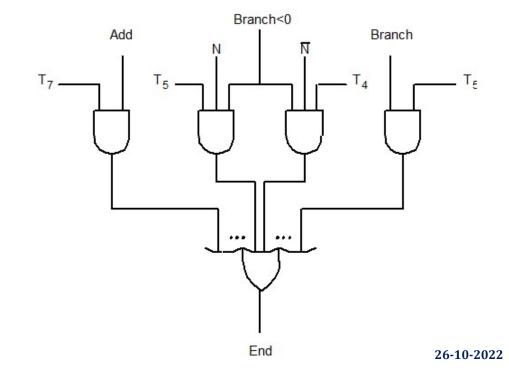

## Generation of the Z<sub>in</sub> and End control signal for the processor

$$Z_{in} = T_1 + T_6 \cdot ADD + T_4 \cdot BR + \dots$$

A.Aruna / AP / IT / SEM 2 / COA

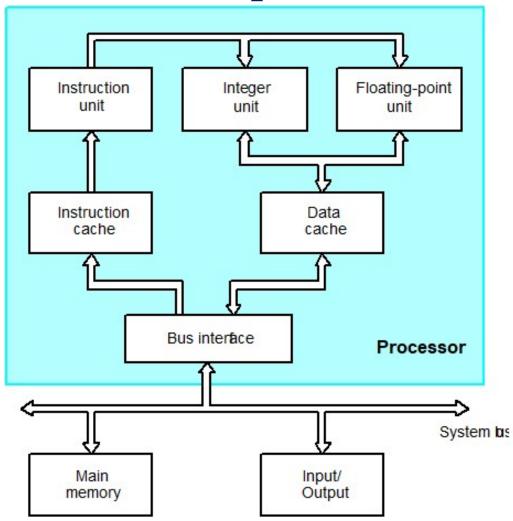

### A Complete Processor

A.Aruna / AP / IT / SEM 2 / COA 26-10-2022