Addition and subtraction of signed numbers – Design of fast adders –

Multiplication of positive numbers - Signed operand multiplication- fast

multiplication - Integer division - Floating point numb

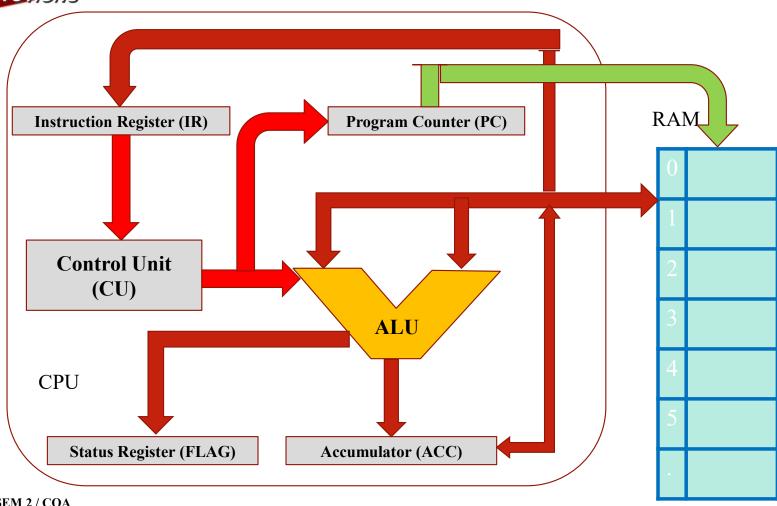

#### Recall the Unit I

- Functional units

- Basic operational concepts

- **Bus Structures**

- Performance

- Memory locations and addresses

- Memory operations

- Instruction and Instruction sequencing

- Addressing modes

- Assembly language

#### **Recall the Unit I**

A.Aruna / AP / IT / SEM 2 / COA

#### Introduction

#### Basic Arithmetic Operation

Representation

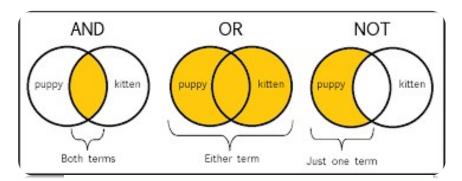

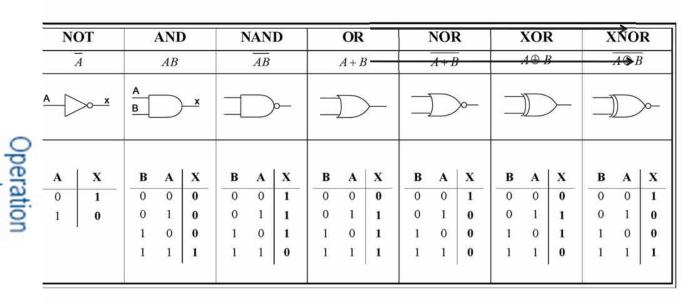

#### **Logical Operation**

#### What's ALU?

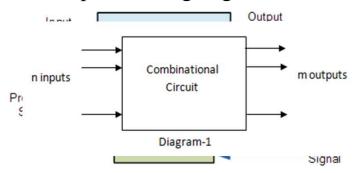

- Stands for Arithmetic and Logic Unit

- Performs Arithmetic (Add, Sub, . . .) and Logical (AND, OR, NOT) operations.

- John Von Neumann proposed the ALU in 1945 when he was working on EDVAC (electronic discrete variable automatic computer)

### **Arithmetic and Logical Unit**

#### **Operations**

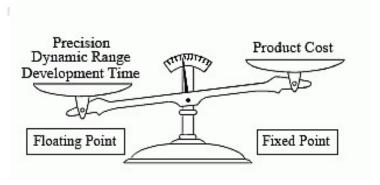

# Precision Dynamic Range Development Time Floating Point Fixed Point

#### Circuit Design

#### Seque intest dans de la Contraction de la contra

# Typical Schematic Symbol of an ALU

| ALU control lines | Function         |

|-------------------|------------------|

| 0000              | AND              |

| 0001              | OR               |

| 0010              | add              |

| 0110              | subtract         |

| 0111              | set on less than |

| 1100              | NOR              |

#### 1 Bit ALU

# Data line and control Line Logic Gates

A.Aruna / AP / IT / SEM 2 / COA

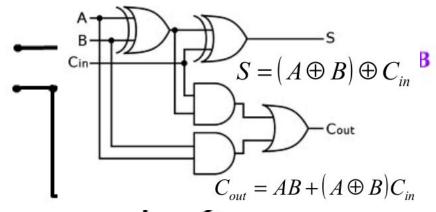

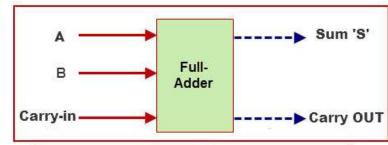

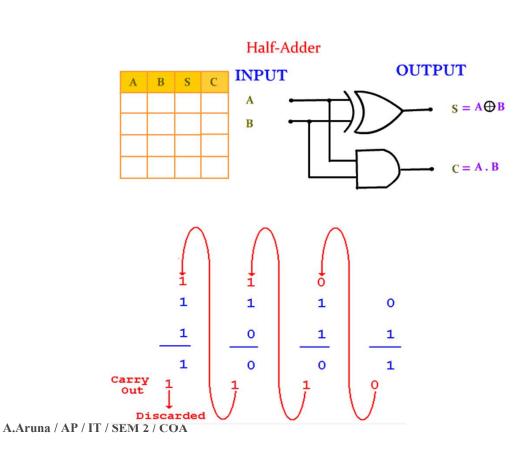

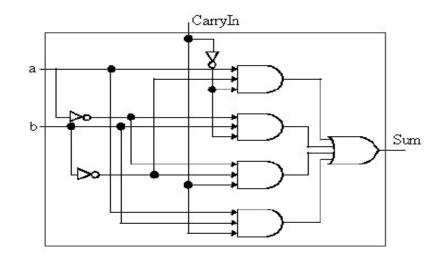

# Logic specification for a stage of "Binary Addition

|   | INPUTS | +0.  | OUTP  | UT |

|---|--------|------|-------|----|

| A | В      | C-IN | C-OUT | S  |

| 0 | 0      | 0    | 0     | 0  |

| 0 | 0      | 1    | 0     | 1  |

| 0 | 1      | 0    | 0     | 1  |

| 0 | 1      | 1    | 1     | 0  |

| 1 | 0      | 0    | 0     | 1  |

| 1 | 0      | 1    | 1     | 0  |

| 1 | 1      | 0    | 1     | 0  |

| 1 | 1      | 1    | 1     | 1  |

| UTS   |

|-------|

| CARRY |

| 0     |

| 0     |

| 0     |

| 1     |

A.Aruna / AP / IT / SEM 2 / COA

10/18

#### EXECUTION & OPERATION INSIDE PROCESSOR

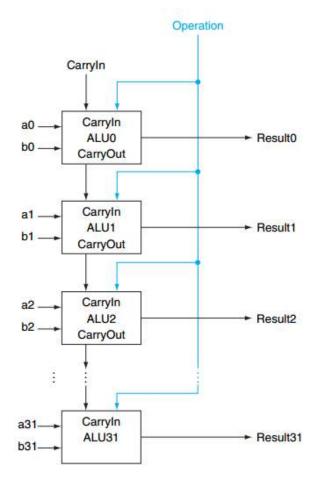

32 BIT ALU

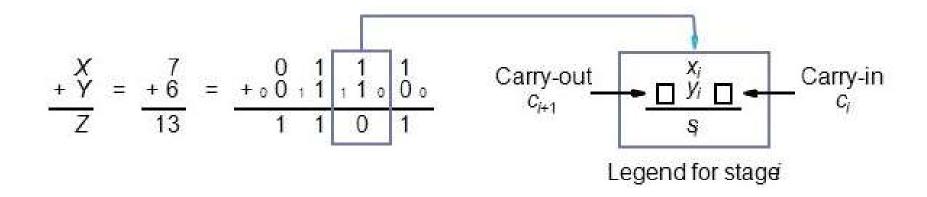

## **Example for Binary Addition**

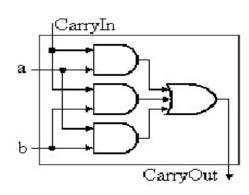

## **Addition and Subtraction Logic Unit**

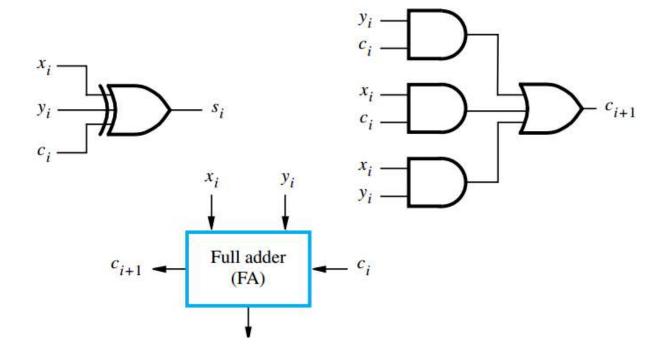

Logic for Single Stage

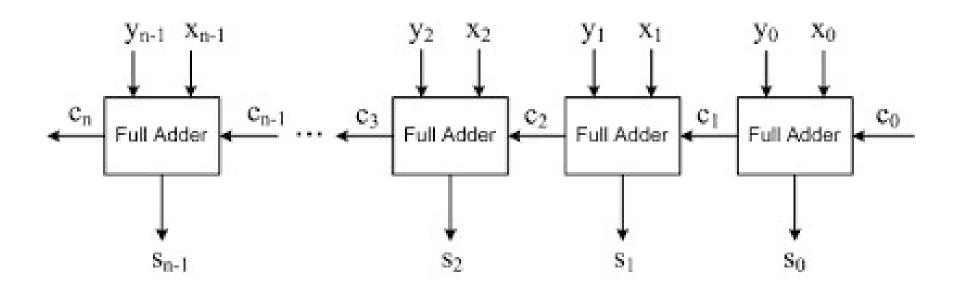

# n bit ripple carry adder

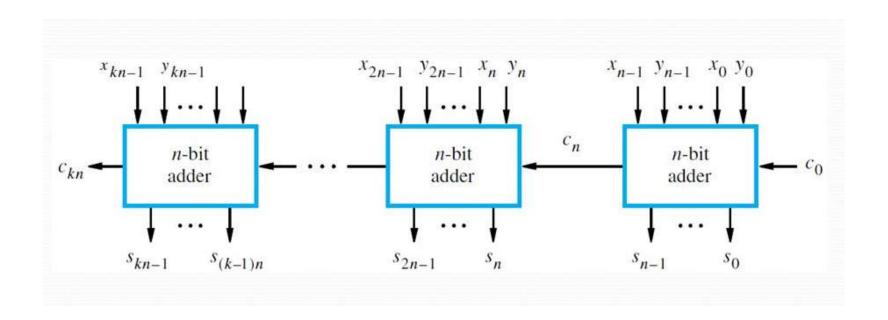

#### cascaded k n bit adders

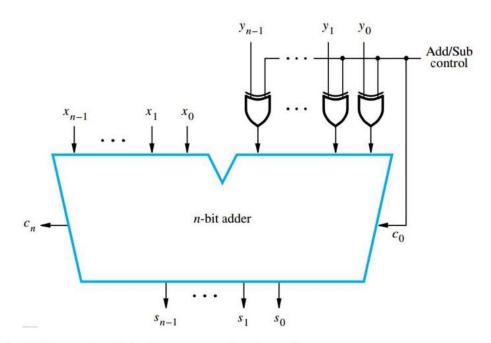

# Binary addition and subtraction logic network

- Addition → Add/sub control = 0.

- Subtraction → Add/sub control = 1

A.Aruna / AP / IT / SEM 2 / COA 01-09-2022

15/18

#### **Assessment**

| Λ | В | Output |

|---|---|--------|

| 0 | 0 | D      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

| Α | В | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 | D      |

| 1 | 0 | D      |

| 1 | 1 | 1      |

NAND

o- Output

| Α | В | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 0      |

| Α | В | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

| Α | В | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

XOR

| Α | В | Output |

|---|---|--------|

| 0 | 0 | D      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | D      |

| Α | В | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | D      |

| 1 | 0 | D      |

| 1 | 1 | 1      |

| Α | Output |

|---|--------|

| 0 | 1      |

| 1 | D      |

#### **Assessment**

Carryout = (b.CarryIn)+(a.CarryIn) +(a.b) Sum = (a.b'.CarryIn')+ (a'.b.CarryIn')+ (a'.b'.CarryIn)+ (a.b.CarryIn)