#### **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (Po), Coimbatore – 641 107

#### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### **DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING**

#### **PIC16F877-Instruction Set**

Dr.G.Arthy Assistant Professor Department of EEE SNS College of Engineering PIC16F877 Architecture/Dr.G.Arthy/EEE/SNSCE

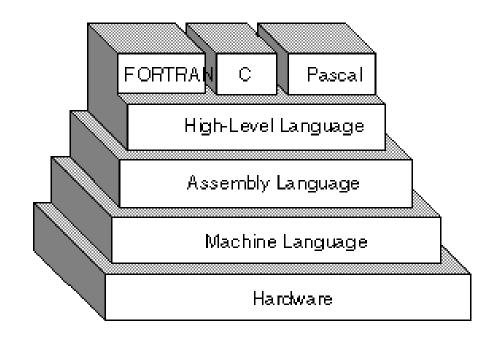

# **Programming Language**

- The lowest-level language is called <u>Machine languages</u>. It means those languages which are closer to the understanding of machine rather than human beings. A machine language thus comprises a string of binary 0's and 1's.

- Machine language is actually a coded set of instructions for a particular CPU (Central Processing Unit), and it is also known as a machine code.

- A machine language is designed to be used by a computer without the need of translation.

# Machine Language

#### Disadvantage :

- 1. It is a machine dependent programming language. Machine dependent means the program designed in one type of machine or computer could not be run on other type of computer or machine. So programs designed in the machine language in one computer are not easily portable to other computers.

- 2. It is a very difficult language to understand and learn. If there is any problem in the program, written in machine language, then it is very difficult to find out the correct mistake.

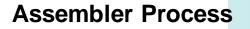

## **Assembly language**

- Assembly language is one level above the machine language. (Both Machine and Assembly language are considered low-level language)

- It uses certain predefined symbolic codes instead of binary codes. These symbolic codes are called mnemonics.

- Assembly language programs are translated into machine language by a program called an assembler.

- High-Level Language overcomes the limitation of writing a program in Machine and Assembly language as it is difficult and time consuming.

- In High-Level Language, the programs can be written using simple English words. Examples of High-Level Language are BASIC, Fortran, COBOL, C, C++.

- Programs written in high-level languages are translated into machine language by a compiler.

### Instructions of PIC

- PIC16F877 has 35 instructions.

- Each instruction if 14 bit words.

- RISC architecture

## Instruction Set

| Instruction Type     | Definition                                                                                                                                                           | Examples                                                              |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| MOVE                 | The contents of a register are copied to another.                                                                                                                    | MOVF, MOVWF,<br>MOVLW                                                 |

| REGISTER             | Register operations affect only<br>a single register, and all except<br>CLRW (clear W) operate on file<br>registers.                                                 | CLRW, CLRF, DECF,<br>INCF, SWAPF, COMF,<br>RLF, RRF, BCF, BSF         |

| ARITHMETIC           | Addition and subtraction in<br>binary gives the same result as<br>in decimal or hex                                                                                  | ADDWF, ADDLW,<br>SUBWF, SUBLW                                         |

| LOGIC                | Logic operations are carried out<br>on bit pairs in two numbers to<br>give the result which would be<br>obtained if they were fed to the<br>corresponding logic gate | ANDWF, ANDLW,<br>IORWF, IORLW, XORWF,<br>XORLW                        |

| TEST, SKIP &<br>JUMP | make decisions (conditional<br>program branches) which<br>depend on some input condition<br>or the result of a calculation                                           | BTFSC, BTFSS, DECFSZ,<br>INCFSZ, GOTO, CALL,<br>RETURN, RETLW, RETFIE |

| CONTROL              |                                                                                                                                                                      | NOP, SLEEP, CLRWDT                                                    |

1/25/2024

#### Opcode field description

| Field | Description                                                                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                         |

| W     | Working register (accumulator)                                                                                                                                               |

| b     | Bit address within an 8-bit file register                                                                                                                                    |

| k     | Literal field, constant data or label                                                                                                                                        |

| ×     | Don't care location (= 0 or 1).<br>The assembler will generate code with x = 0.<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                          |

| PC    | Program Counter                                                                                                                                                              |

| то    | Time-out bit                                                                                                                                                                 |

| PD    | Power-down bit                                                                                                                                                               |

Source:Microchip, PICmicro™ Mid-Range MCU Family Reference Manual, December 1997 /DS33023A

### **Basic Categories of Instructions**

- There are three basic categories:

- Byte-Oriented Instruction:

- F: File Register (or RAM)

- D: Destination

- D=0: Destination  $\rightarrow$  W

- − D=1: Destination → File Register

- Bit-Oriented Instruction:

- F: Register File where the Bit is located

- B: Bit Field

- Literal and Control Operation:

- K: 8-bit constant

#### Figure 29-1: General Format for Instructions

# **PIC16F877A** Instruction set

- Some instructions with alternate result destinations. The default destination for the result of an operation is the file register, but the working register W is sometimes an option.

- There are three basic categories:

- Byte-Oriented Instruction:

- F: File Register (or RAM)

- D: Destination

- D=0: Destination  $\rightarrow$  W

- D=1: Destination  $\rightarrow$  File Register

- Bit-Oriented Instruction:

- F: Register File where the Bit is located

- B: Bit Field

- Literal and Control Operation:

- K: 8-bit constant

### Byte oriented file register Operation

| Mnemo  | nic, | Description                  | Status                    |

|--------|------|------------------------------|---------------------------|

| Operar | nds  |                              | Affected                  |

| ADDWF  | f,d  | Add W and f                  | C,DC,Z                    |

| ANDWF  | f,d  | AND W with f                 | Z                         |

| CLRF   | f    | Clear f                      | Z                         |

| CLRW   | -    | Clear W                      | Z                         |

| COMF   | f,d  | Complement f                 | Z                         |

| DECF   | f,d  | Decrement f                  | Z                         |

| DECFSZ | f,d  | Decrement f, Skip if 0       |                           |

| INCF   | f,d  | Increment f                  | Z                         |

| INCFSZ | f,d  | Increment f, Skip if 0       |                           |

| IORWF  | f,d  | Inclusive OR W with f        | Z                         |

| MOVF   | f,d  | Move f                       | Z                         |

| MOVWF  | d    | Move W to f                  |                           |

| NOP    | -    | No operation                 |                           |

| RLF    | f,d  | Rotate Left f through Carry  | С                         |

| RRF    | f,d  | Rotate Right f through Carry | С                         |

| SUBWF  | f,d  | Subtract W from f            | C,DC,Z                    |

| SWAPF  | f,d  | Swap nibbles in f            | 1.0.0 × 10 0.000 0.000000 |

| XORWF  | f,d  | Exclusive OR W with f        | Z                         |

| Mnemo | onic,        | Description               | Status   |

|-------|--------------|---------------------------|----------|

| Opera | nds          |                           | Affected |

| BCF   | f,b          | Bit Clear f               |          |

| BSF   | $_{\rm f,b}$ | Bit Set f                 |          |

| BTFSC | f,b          | Bit Test f, Skip if Clear |          |

| BTFSS | $_{\rm f,b}$ | Bit Test f, Skip if Set   |          |

Source:Microchip, Plcmicro™ Mid-Range MCU Family Reference Manual, December 1997 /DS33023A

# Literal and Control operations

| Mnemo  | nic | Description                 | Status   |

|--------|-----|-----------------------------|----------|

|        |     | Description                 |          |

| Opera  | lds |                             | Affected |

| ADDLW  | k   | Add literal and W           | C,DC,Z   |

| ANDLW  | k   | AND literal with W          | Z        |

| CALL   | k   | Call subroutine             |          |

| CLRWDT | -   | Clear watchdog timer        | TO, PD   |

| GOTO   | k   | Goto address                |          |

| IORLW  | k   | Inclusive OR literal with W | Z        |

| MOVLW  | k   | Move literal to W           |          |

| RETFIE | -   | Return from interrupt       |          |

| RETLW  | k   | Return with literal in W    |          |

| RETURN | -   | Return from subroutine      |          |

| SLEEP  | -   | Clear watchdog timer        | TO, PD   |

| SUBLW  | k   | Subtract W from literal     | C,DC,Z   |

| XORLW  | k   | Exclusive OR literal with W | Z        |

Source:Microchip, PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual, December 1997 /DS33023A

ADI

Example 1

Example 2

|                                                                                                             | ADDWF                                      | Add W and f                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| DWF                                                                                                         | Syntax:                                    | [label] ADDWF f,d                                                                                                                          |

|                                                                                                             | Operands:                                  | 0 ≤ f ≤ 127<br>d ∈[0,1]                                                                                                                    |

|                                                                                                             | Operation:                                 | $(W) + (f) \rightarrow (destination)$                                                                                                      |

|                                                                                                             | Status Affected:                           | C, DC, Z                                                                                                                                   |

|                                                                                                             | Description:                               | Add the contents of the W register                                                                                                         |

| ADDWF FSR, 0<br>Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2 |                                            | with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. |

| After Instruction<br>W = 0x17<br>FSR = 0xC2                                                                 | ddress (FSR) = 0x20<br>ddress (FSR) = 0x37 |                                                                                                                                            |

| ANDWF            | A                                                                 | ND W with f                                 |                                                               |                     |

|------------------|-------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------|---------------------|

| Syntax:          | [label] AN                                                        | DWF f,d                                     |                                                               |                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ |                                             |                                                               |                     |

| Operation:       | (W).AND. (f                                                       | ) $\rightarrow$ destination                 |                                                               |                     |

| Status Affected: | Z                                                                 |                                             |                                                               |                     |

| Encoding:        | 00                                                                | 0101 dfff                                   | ffff                                                          |                     |

| Description:     |                                                                   | egister with registe<br>sult is stored back | r f'. If 'd' is 0 the result is stored in<br>in register 'f'. | the W register. If  |

| Words:           | 1                                                                 |                                             |                                                               |                     |

| Cycles:          | 1                                                                 | Example 1                                   | ANDWF FSR                                                     |                     |

|                  |                                                                   |                                             | Before Instruction                                            | ; 0001 0111 (0x17   |

|                  |                                                                   |                                             | W = 0x17                                                      | ; 1100 0010 (0xC2   |

|                  |                                                                   |                                             | FSR = 0xC2                                                    | ;                   |

|                  |                                                                   |                                             | After Instruction                                             | ; 0000 0010 (0x02   |

|                  |                                                                   |                                             | W = 0x17                                                      |                     |

|                  |                                                                   |                                             | FSR = 0x02                                                    |                     |

|                  |                                                                   | Example 2                                   | ANDWF FSR, 0                                                  |                     |

|                  |                                                                   |                                             | Before Instruction                                            | ; 0001 0111 (0x17   |

|                  |                                                                   |                                             | W = 0×17                                                      | ; 1100 0010 (0xC2   |

|                  |                                                                   |                                             | FSR = 0xC2                                                    | ;                   |

|                  |                                                                   |                                             | After Instruction                                             | ; 0000 0010 (0x02   |

|                  |                                                                   |                                             | W = 0x02                                                      | ALCON NO. IN CARLES |

|                  |                                                                   |                                             | FSR = 0xC2                                                    |                     |

INSTITUTIONS

PIC16F877 Architecture/Dr.G.Arthy/EEE/SNSCE

| CLRF             |                                                                     | Clear f     |            |          |                                                                                    |

|------------------|---------------------------------------------------------------------|-------------|------------|----------|------------------------------------------------------------------------------------|

| Syntax:          | [ label ]                                                           | CLRF f      |            |          |                                                                                    |

| Operands:        | $0 \le f \le 1$                                                     | 27          |            |          |                                                                                    |

| Operation:       | $\begin{array}{c} 00h \rightarrow f \\ 1 \rightarrow Z \end{array}$ |             |            |          |                                                                                    |

| Status Affected: | Z                                                                   |             |            |          |                                                                                    |

| Encoding:        | 0.0                                                                 | 0001        | lfff       | ffff     | ]                                                                                  |

| Description:     | The con                                                             | tents of re | egister 'f | are clea | red and the Z bit is set.                                                          |

| Words:           | 1                                                                   |             |            |          |                                                                                    |

| Cycles:          | 1                                                                   |             |            |          |                                                                                    |

|                  | [                                                                   | Exam        | ple 1      |          | CLRF FLAG_REG                                                                      |

|                  |                                                                     |             |            |          | Before Instruction<br>FLAG_REG=0x5A<br>After Instruction<br>FLAG_REG=0x00<br>Z = 1 |

| Contact and |

|-------------|

|         | Clear W                                         |                                                                                                                                  |

|---------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| [ label | ] CLRW                                          |                                                                                                                                  |

| None    |                                                 |                                                                                                                                  |

|         |                                                 |                                                                                                                                  |

| Z       |                                                 |                                                                                                                                  |

| 00      | 0001 0xxx                                       | xxxx                                                                                                                             |

| W regi  | ister is cleared. Ze                            | ro bit (Z) is set.                                                                                                               |

| 1       |                                                 |                                                                                                                                  |

| 1       | Example 1                                       | CLRW                                                                                                                             |

|         |                                                 | Before Instruction                                                                                                               |

|         |                                                 | W = 0                                                                                                                            |

|         |                                                 | After Instruction                                                                                                                |

|         |                                                 | W = 0                                                                                                                            |

|         |                                                 | Z =                                                                                                                              |

|         | None<br>00h →<br>1 → Z<br>Z<br>00<br>W reg<br>1 | [ <i>label</i> ] CLRW<br>None<br>$00h \rightarrow W$<br>$1 \rightarrow Z$<br>Z<br>00 0001 0xxx<br>W register is cleared. Ze<br>1 |

0x5A

0x00

1

| COMF             |                         | Comple    | ement f |      |                                                 |           |        |

|------------------|-------------------------|-----------|---------|------|-------------------------------------------------|-----------|--------|

| Syntax:          | [ label ]               | COMF      | f,d     |      |                                                 |           |        |

| Operands:        | 0 ≤ f ≤ 1<br>d ∈ [0,1]  |           |         |      |                                                 |           |        |

| Operation:       | $(\overline{f}) \to de$ | stination |         |      |                                                 |           |        |

| Status Affected: | z                       |           |         |      |                                                 |           |        |

| Encoding:        | 00                      | 1001      | dfff    | ffff |                                                 |           |        |

| Description:     |                         |           | -       |      | omplemented. If 'd' is<br>pred back in register |           | is     |

| Words:           | 1                       |           |         |      | Evenue                                          | 4         |        |

| Cycles:          | 1                       |           |         |      | Example                                         | 1         |        |

|                  |                         |           |         |      |                                                 |           |        |

|                  |                         |           |         |      | COMF                                            | REG1      | , 0    |

|                  |                         |           |         |      | Before I                                        | nstructi  | on     |

|                  |                         |           |         |      |                                                 | REG1=     | = 0x13 |

|                  |                         |           |         |      | After Ins                                       | struction | 1      |

|                  |                         |           |         |      | 1                                               | REG1=     |        |

|                  |                         |           |         |      |                                                 | W =       | 0xEC   |

|                  |                         |           |         |      |                                                 | vv –      | UXEC   |

|--|

| DECF             | Decrement f                                                                                      |                                    |

|------------------|--------------------------------------------------------------------------------------------------|------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                               |                                    |

| Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                         |                                    |

| Operation:       | (f) - 1 $\rightarrow$ destination                                                                |                                    |

| Status Affected: | Z                                                                                                |                                    |

| Encoding:        | 00 0011 dfff ffff                                                                                |                                    |

| Description:     | Decrement register 'f. If 'd' is 0 the result is stored<br>result is stored back in register 'f. | in the W register. If 'd' is 1 the |

| Words:           | 1                                                                                                | Example 1                          |

| Cycles:          | 1                                                                                                |                                    |

|                  |                                                                                                  | DECF CNT                           |

|                  |                                                                                                  | Before Instruction                 |

|                  |                                                                                                  | CNT = 0x01                         |

|                  |                                                                                                  | Z = 0                              |

|                  |                                                                                                  | After Instruction                  |

|                  |                                                                                                  | CNT = 0x00                         |

|                  |                                                                                                  | Z = 1                              |

| DECFSZ                      | Decrement f, Skip if 0                                                                                   | I                  |                                              |                                                                |

|-----------------------------|----------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------|----------------------------------------------------------------|

| Syntax:                     | [label] DECFSZ f,d                                                                                       |                    |                                              |                                                                |

| Operands:                   | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                 |                    |                                              |                                                                |

| Operation:                  | (f) - 1 $\rightarrow$ destination; skip if result                                                        | it = 0             |                                              |                                                                |

| tatus Affected: None        |                                                                                                          |                    |                                              |                                                                |

| Encoding: 00 1011 dfff ffff |                                                                                                          | f                  |                                              |                                                                |

| Manda                       | If the result is 0, then the next in instruction execution) is discarded ing this a 2 cycle instruction. | ed and a NOP is ex | ecuted instea                                | d, mak-                                                        |

| Words:<br>Cycles:           | 1<br>1(2)                                                                                                | Case 1:            | Before Inst<br>PC =<br>CNT =<br>After Instru | <ul> <li>address HERE</li> <li>0x01</li> </ul>                 |

| Example                     |                                                                                                          |                    | CNT =                                        | = 0x00                                                         |

| C=04,84                     |                                                                                                          |                    | PC =                                         | address CONTINUE                                               |

| HEF                         | E DECFSZ CNT, 1                                                                                          |                    |                                              | truction                                                       |

|                             | and the standards                                                                                        | Case 2:            | Before Inst                                  |                                                                |

| 201                         | GOTO LOOP                                                                                                | Case 2:            | PC =<br>CNT =                                | <ul> <li>address HERE</li> <li>0x02</li> </ul>                 |

| CON                         | and the standards                                                                                        | Case 2:            | PC<br>CNT =<br>After Instru                  | <ul> <li>address HERE</li> <li>0x02</li> <li>action</li> </ul> |

| CON                         | GOTO LOOP                                                                                                | Case 2:            | PC<br>CNT<br>After Instru<br>CNT             | <ul> <li>address HERE</li> <li>0x02</li> <li>action</li> </ul> |

INSTITUTIO

PIC16F877 Architecture/Dr.G.Arthy/EEE/SNSCE