### SNS COLLEGE OF ENGINEERING

Kurumbapalayam (Po), Coimbatore – 641 107

#### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

## **ARM-Registers**

Dr.G.Arthy

Assistant Professor

Department of EEE

SNS College of Engineering

### **ARE YOU USING THIS?**

## REGISTERS

- ARM processors have 37 registers.

- The registers are arranged in partially overlapping banks.

- There is a different register bank for each processor mode.

- The banked registers give rapid context switching for dealing with processor exceptions and privileged operations.

### REGISTERS

- Thirty general-purpose registers (32 bit each)

- The Program Counter (PC)

- The Application Program Status Register (APSR)

- Saved Program Status Registers (SPSRs).

- Current Program Status Registers (CPSRs).

## **ARM-OPERATING MODES**

| Mode Privilegeo      |     | Purpose                                                                              |  |  |

|----------------------|-----|--------------------------------------------------------------------------------------|--|--|

| User                 | No  | Normal operating mode for most programs (tasks)                                      |  |  |

| Fast Interrupt (FIQ) | Yes | Used to handle a high-priority (fast) interrupt                                      |  |  |

| Interrupt (IRQ)      | Yes | Used to handle a low-priority (normal) interrupt                                     |  |  |

| Supervisor           | Yes | Used when the processor is reset, and to handle the softwa interrupt instruction swi |  |  |

| Abort                | Yes | Used to handle memory access violations                                              |  |  |

| Undefined            | Yes | Used to handle undefined or unimplemented instructions                               |  |  |

| System               | Yes | Uses the same registers as User mode                                                 |  |  |

**Table 1: ARM Processor Operating Modes**

### **EXECUTION MODES**

- A privileged execution has access to all resources.

- Unprivileged execution limits or excludes access to some resources.

## **REGISTERS**

Privileged Modes

#### Exception Modes

| User   | System | Supervisor | Abort    | Undefined | Interrupt | Fast interrupt |

|--------|--------|------------|----------|-----------|-----------|----------------|

| r0     | r0     | r0         | r0       | r0        | r0        | 10             |

| r1     | r1     | orl.       | rI       | 21        | rI        | rI             |

| r2     | r2     | 12         | r2       | 12        | 72        | 12             |

| r3     | r3     | 13         | 13       | 13        | 13        | 13             |

| r4     | r4     | 14         | r4       | 14        | r4        | r4             |

| r5     | r5     | 15         | 15       | 15        | V5        | 15             |

| r6     | r6     | 16         | r6       | 16        | rifo .    | 16             |

| r7     | r7     | - 17       | 77       | r7        | 77        | r7:            |

| r8     | r8     | 78         | 25       | r8        | 18        | r8_fiq         |

| r9     | r9     | 79         | 19       | 19        | 19        | r9_fiq         |

| r10    | r10    | rIO        | r10      | r10       | rIO       | r10_fiq        |

| r11    | r11    | rH         | rH       | F11       | rH        | r11_fiq        |

| r12    | r12    | r12        | r12      | r12       | r12       | r12_fiq        |

| r13 sp | r13 sp | r13_svc    | r13_abt  | r13_und   | r13_irq   | r13_fiq        |

| r14 lr | r14 lr | r14_svc    | r14_abt  | r14_und   | r14_irq   | r14_fiq        |

| r15 pc | r15 pc | r15 pc     | r15 pc   | r15 pc    | r15 pc    | r15 pc         |

| cpsr   | cpsr   | CDSF       | cpsr     | cpsr      | cpsr      | cpsr           |

| _      | _      | spsr_svc   | spsr_abt | spsr_und  | spsr_irq  | spsr_fiq       |

Banked register

## LINK REGISTER

- r14 or lr In user mode, used as a link register to store the return address when a subroutine call is made.

- r14 or lr In exception mode, lr holds the return address for the exception, or a subroutine return address if subroutine calls are executed within an exception.

## PROGRAM COUNTERS

- Program Counter is accessed as pc (or r15).

- It is incremented by one word (four bytes) for each instruction.

•

Branch instructions load the destination address into pc.

# **Application Program Status Register** (APSR)

- APSR holds copies of the Arithmetic Logic Unit (ALU) status flags.

- They are used to determine whether conditional instructions are executed or not.

# Saved Program Status Registers (SPSRs)

• The SPSRs are used to store the CPSR when an exception is taken.

User mode and System mode do not have an SPSR because they are not exception handling modes.

# Current Program Status Register (CPSR)

### The CPSR holds:

- The APSR flags

- The current processor mode

- Interrupt disable flags

- · Current processor state (ARM, Thumb, or Jazelle)

# Current Program Status Register (CPSR)

- CPSR to monitor and control internal operations.

- The CPSR is a dedicated 32-bit register and resides in the register file.

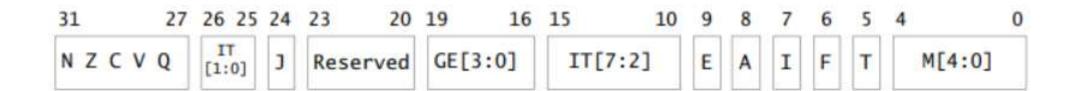

## Current Program Status Register (CPSR)

27 26 25 24 23

NZCVQ

16 15

IT[7:2]

Reserved GE[3:0]

M[4:0]

- N Negative result from ALU.

- Z Zero result from ALU.

- C ALU operation Carry out.

- V ALU operation oVerflowed.

- Q cumulative saturation (also described as sticky).

- J indicates whether the core is in Jazelle state.

- GE used by some SIMD instructions.

- IT [7:2] If-Then conditional execution of Thumb-2 instruction groups.

- E bit controls load/store endianness.

- A bit disables asynchronous aborts.

- I bit disables IRQ.

- F bit disables FIQ.

- T bit indicates whether the core is in Thumb state.

- • M[4:0] specifies the processor mode

## **EXCEPTIONS**