### **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (PO), Coimbatore - 641 107 Accredited by NAAC-UGC with 'A' Grade Approved by AICTE, Recognized by UGC & Affiliated to Anna University, Chennai

### **DEPARTMENT OF INFORMATION TECHNOLOGY COURSE NAME: 19IT301 COMPUTER ORGANIZATION**

**AND ARCHITECTURE**

**II YEAR/ III SEM**

**Unit 3 : Processor and Pipelining**

**Topic 3.2: Execution of a Complete Instruction –**

**Multiple bus organization**

SNSCE / IT / III Sem / V. Vaishnavee AP-IT

11/18/2023

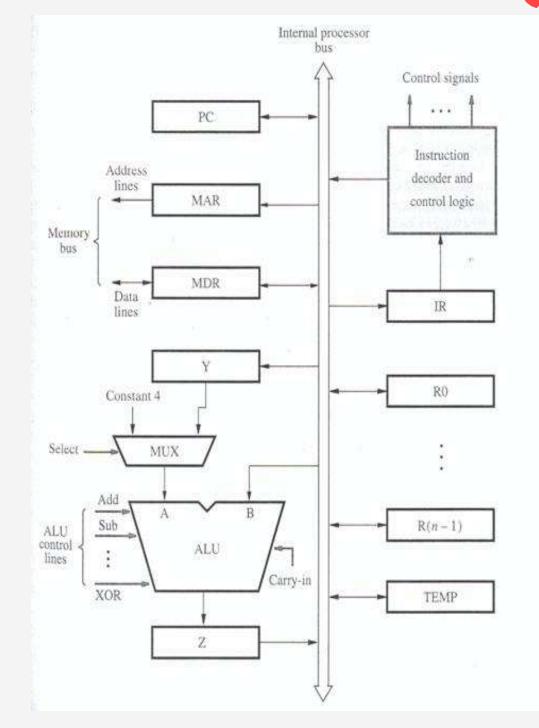

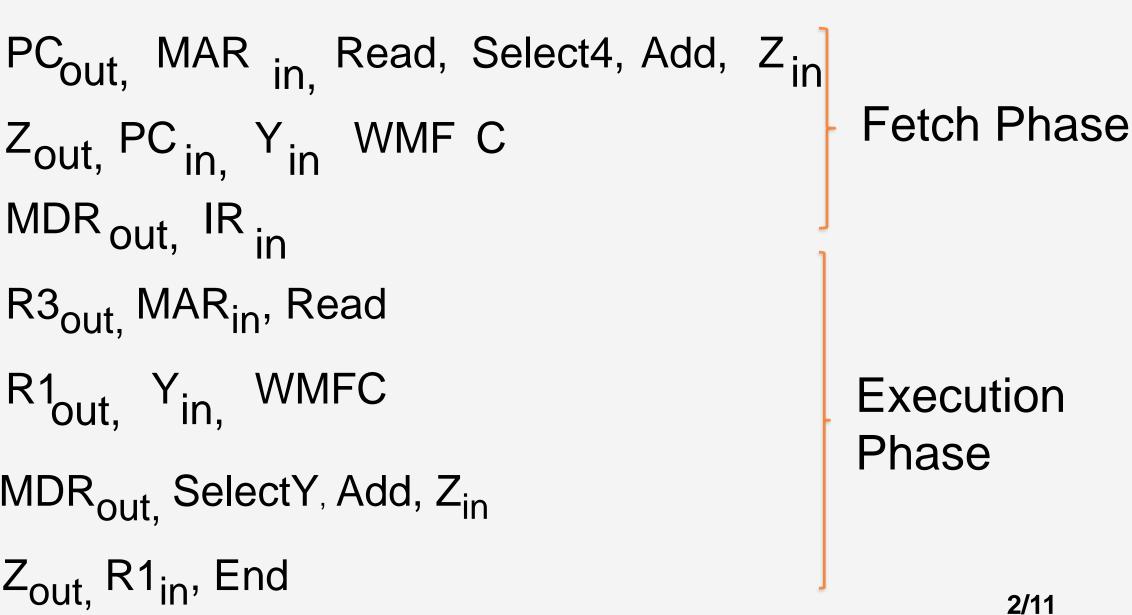

## **Execution of a Complete Instruction**

Sequence of elementary operations to execute Add (R3), R1 requires the following actions:

- Fetch the instruction

- Fetch the first operand (the contents of the memory location) pointed to by R3)

- Perform the addition

- Load the result into R1

# Execution of a Complete Instruction

11/18/2023

R1 in a single-bus architecture

### **Step Action**

2

4

5

- Zout, PC in, Y in WMF C

- MDR<sub>out</sub>, IR<sub>in</sub> 3

- R3<sub>out.</sub> MAR<sub>in</sub>, Read

- R1<sub>out.</sub> Y<sub>in.</sub> WMFC

6 MDR<sub>out.</sub> SelectY, Add, Z<sub>in</sub>

Z<sub>out.</sub> R1<sub>in</sub>, End 7 **SNSCE / IT / V Sem / V. Vaishnavee AP-IT**

# Control Sequence for execution of the instruction Add (R3),

## **Execution of Branch Instructions**

- A branch instruction replaces the contents of PC with the branch target address, which is usually obtained by adding an offset X given in the branch instruction.

- The offset X is usually the difference between the branch target ulletaddress and the address immediately following the branch instruction.

- UnConditional branch ullet

### Control sequence for an unconditional branch instruction

### **Step Action**

| 1 | PC <sub>out</sub> , MAR in, Read, Select4                     |

|---|---------------------------------------------------------------|

| 2 | Z <sub>out</sub> , PC <sub>in</sub> , Y <sub>in</sub> , WMF C |

| 3 | MDR <sub>out</sub> , IR in                                    |

| 4 | Offset-field-of-IR <sub>out</sub> , Add, Z <sub>il</sub>      |

| 5 | Z <sub>out</sub> , PC <sub>in</sub> , End                     |

PC=2000, Target address=2050 X = 46

**SNSCE / IT / V Sem / V. Vaishnavee AP-IT**

**1**1/18/2023

### 4, Add, Z<sub>in</sub>

### n

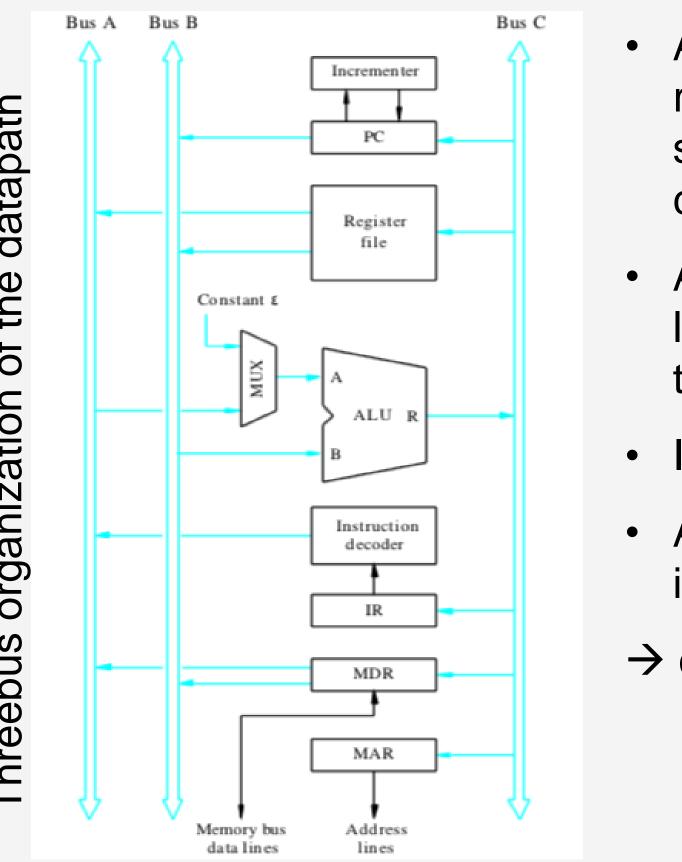

## **Multiple-Bus Organization**

Threebus organization of the datapath

11/18/2023

- Allow the contents of two different registers to be accessed simultaneously and have their contents placed on buses A and B.

- Allow the data on bus C to be loaded into a third register during the same clock cycle.

- Incrementer unit.

- ALU simply passes one of its two input operands unmodified to bus C

- $\rightarrow$  control signal: R=A or R=B

## **Multiple-Bus Organization**

- General purpose registers are combined into a single block called register file.

- Register file has 3 ports, 2 outputs ports –access two different registers and have their contents on buses A and B Third port allows data on bus C during same clock cycle. Buses A & B are used to transfer the source operands to A & B

- inputs of the ALU.

- ALU operation is performed.

- The result is transferred to the destination over the bus C.

## Multiple-Bus Organization

- ALU may simply pass one of its 2 input operands unmodified to bus C. •

- The ALU control signals for such an operation R=A or R=B. ullet

- Incrementer unit is used to increment the PC by 4. •

- Using the incrementer eliminates the need to add the constant value 4 ulletto the PC using the main ALU.

- The source for the constant 4 at the ALU input multiplexer can be used lacksquareto increment other memory address such as loadmultiple & storemultiple instructions

11/18/2023

### Control sequence for the instruction Add R4,R5,R6, for the three-bus organization

### **Step Action**

- PCout, R=B, MAR in. Read, IncPC 1 2 WMFC

- 3 MDR<sub>outB</sub>, R=B, IR<sub>in</sub>

- R4outA, R5outB, SelectA, Add, R6in, End 4

11/18/2023

**SNSCE / IT / V Sem / V. Vaishnavee AP-IT**

8/11

## Explanation

Step 1: The contents of PC are passed through the ALU using R=B control signal & loaded into MAR to start a memory read operation.

At the same time PC is incrementer by 4 Step 2: The processor waits for MFC Step 3: Loads the data , received into MDR, then transfers them to IR.

Step 4: The execution phase of the instruction requires only one control step to complete.

> Advantage: Reduction in the number of clock cycles to execute an instruction

11/18/2023

What is the control sequence for execution of the instruction Add R1, R2 including the instruction fetch phase? (Assume single bus architecture)

11/18/2023

## Thank You

**11/18/2**023