#### SNS COLLEGE OF ENGINEERING

Kurumbapalayam (Po), Coimbatore - 641 107

#### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

**COURSE NAME: 19EE101-BASIC ELECTRICAL & ELECTRONICS ENGINEERING**

I YEAR /I SEMESTER

Unit 5: Linear and Digital Electronics

Topic : Half Adder

# **GRADUATE ATTRIBUTES**

## INTRODUCTION TO LOGIC GATES

A logic gate is an idealized model of computation or physical electronic device implementing a Boolean function, a logical operation performed on one or more binary inputs that produces a single binary output.

## **TYPES OF LOGIC GATE**

#### Six types of gates

- •NOT

- •AND

- •OR

- •XOR

- •NAND

- •NOR

Typically, logic diagrams are black and white with gates distinguished only by their shape

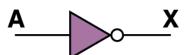

### **NOT GATE**

A NOT gate accepts one input signal (0 or 1) and returns the opposite signal as output

#### **Boolean Expression**

**Logic Diagram Symbol**

**Truth Table**

| Y | _ | Δ | ١ |

|---|---|---|---|

| Λ | _ | A |   |

| Α | X |  |

|---|---|--|

| 0 | 1 |  |

| 1 | 0 |  |

# **AND GATE**

An AND gate accepts two input signals If both are 1, the output is 1; otherwise, the output is 0

| Boolean Expression | Logic Diagram Symbol | T | ruth Tabl | е |

|--------------------|----------------------|---|-----------|---|

|                    | A x                  | Α | В         | Х |

| $X = A \cdot B$    | ^                    | 0 | 0         | 0 |

|                    | В                    | 0 | 1         | 0 |

|                    |                      | 1 | 0         | 0 |

|                    |                      | 1 | 1         | 1 |

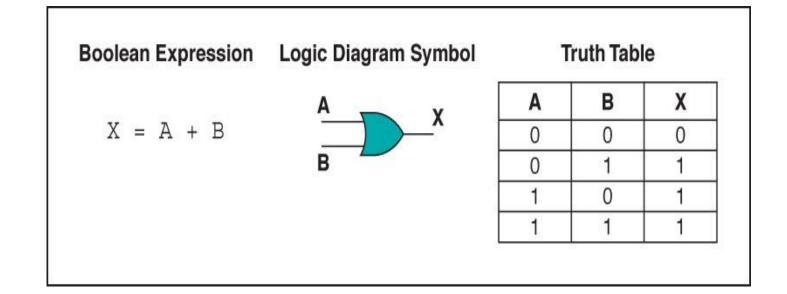

# **OR GATE**

An OR gate accepts two input signals If both are 0, the output is 0; otherwise, the output is 1

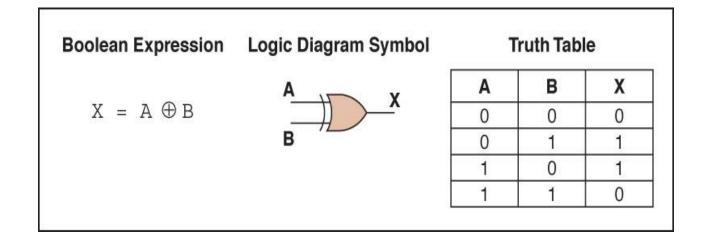

# **XOR GATE**

An XOR gate accepts two input signals If both are the same, the output is 0; Otherwise, the output is 1

## **NAND GATE**

The NAND gate accepts two input signals If both are 1, the output is 0; otherwise,the output is 1

| <b>Boolean Expression</b> | Logic Diagram Symbol | Truth Table |   |   |

|---------------------------|----------------------|-------------|---|---|

|                           | A X                  | Α           | В | Х |

| $X = (A \cdot B)'$        |                      | 0           | 0 | 1 |

|                           | В                    | 0           | 1 | 1 |

|                           |                      | 1           | 0 | 1 |

|                           |                      | 1           | 1 | 0 |

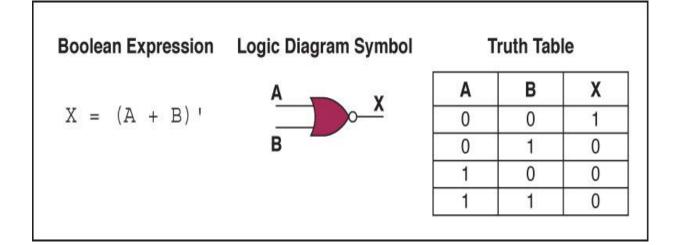

# **NOR GATE**

The NOR gate accepts two input signals If both are 0, the output is 1; otherwise, the output is 0

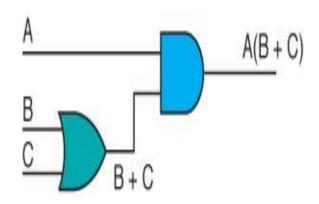

#### SAMPLE COMBINATIONAL CIRCUIT

Consider the following Boolean expression A(B + C)

| Α | В | С | B + C | A(B+C) |

|---|---|---|-------|--------|

| 0 | 0 | 0 | 0     | 0      |

| 0 | 0 | 1 | 1     | 0      |

| 0 | 1 | 0 | 1     | 0      |

| 0 | 1 | 1 | 1     | 0      |

| 1 | 0 | 0 | 0     | 0      |

| 1 | 0 | 1 | 1     | 1      |

| 1 | 1 | 0 | 1     | 1      |

| 1 | 1 | 1 | 1     | 1      |

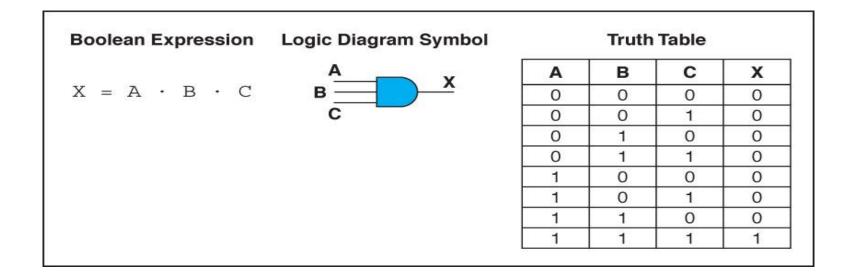

### **GATES WITH MORE INPUTS**

Gates can be designed to accept three or more input values

A three-input AND gate, for example, produces an output of 1 only if all input values are 1

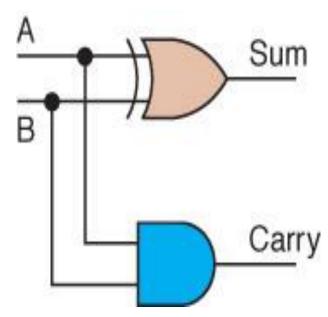

## **APPLICATION-HALF ADDER**

The result of adding two binary digits could produce a carry value

Recall that 1 + 1 = 10 in base two

#### Half adder

A circuit that computes the sum of two bits and produces the correct carry bit

Circuit diagram representing a half adder Boolean expressions

$$sum = A \oplus B$$

$$carry = AB$$

| A | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

#### REFERENCES

- 1. Muthusubramanian R, Salivahanan S, "Basic Electrical and Electronics Engineering", Tata McGraw Hill Publishers, (2009) UNIT I V

- 2. Bhattacharya. S.K, "Basic Electrical and Electronics Engineering", Pearson Education, (2017) UNIT I IV

- Mehta V K, Mehta Rohit, "Principles of Electrical Engineering and Electronics",

S.Chand & Company Ltd, (2010)- UNIT I and II

- 4. Mehta V K, Mehta Rohit, "Principles of Electronics", S.Chand & Company Ltd, (2005)- UNIT IV and V

#### THANK YOU