## UNIT III PROCESSOR AND PIPELINING

**Fundamental concepts** – Execution of a complete instruction – Multiple bus organization – Hardwired control – Micro programmed control – Pipelining: Basic concepts – Data hazards – Instruction hazards – Influence on Instruction sets – Data path and control consideration.

- Instruction Set Processor (ISP)

- Central Processing Unit (CPU)

- A typical computing task consists of **a series of steps** specified by a **sequence of machine instructions** that constitute a program.

- An instruction is executed by carrying out a sequence of more rudimentary operations.

- Processor fetches **one instruction at a time and perform** the operation specified.

- Instructions are **fetched from successive memory locations** until a branch or a jump instruction is encountered.

- Processor keeps track of the address of the memory location containing the next instruction to be fetched using **Program Counter (PC)**.

- Instruction Register (IR)

• Fetch the contents of the memory location pointed to by the PC. The contents of this location are loaded into the IR (fetch phase).

#### $\mathsf{IR} \leftarrow \llbracket\mathsf{PC}\rrbracket$

• Assuming that the memory is byte addressable, increment the contents of the PC by 4 (fetch phase).

#### $\mathsf{PC} \leftarrow [\mathsf{PC}] + 4$

• Carry out the actions specified by the instruction in the IR (execution phase).

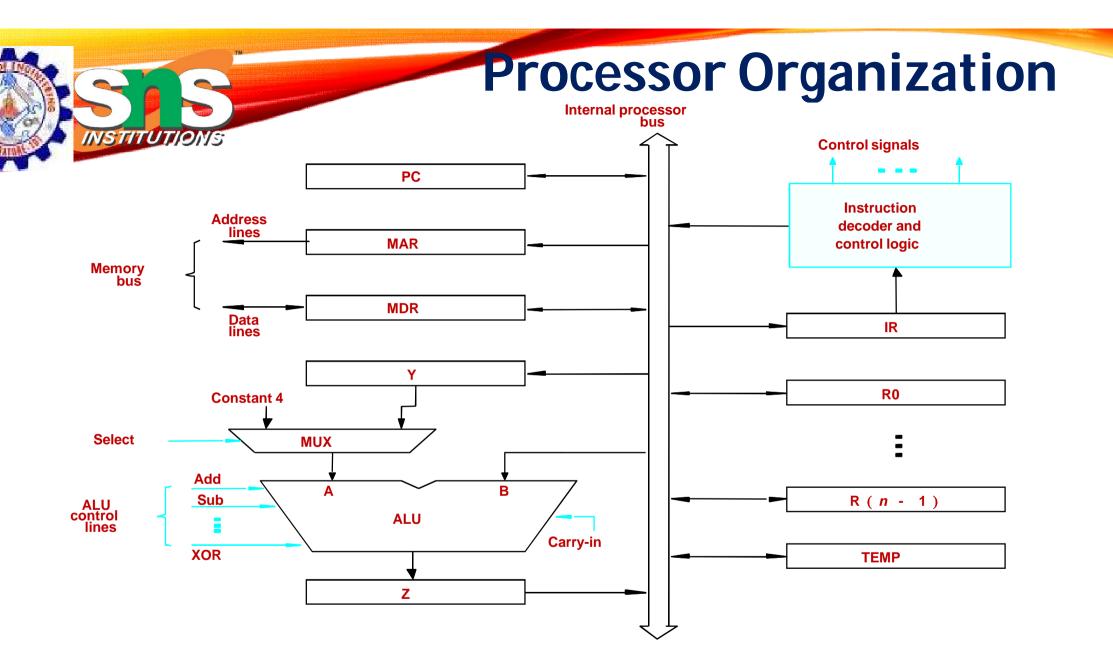

Figure : Single-bus organization of the datapath inside a processor.

- ALU

- Registers for temporary storage

- Various digital circuits for executing different micro operations.(gates, MUX,decoders,counters).

- Internal path for movement of data between ALU and registers.

- Driver circuits for transmitting signals to external units.

- Receiver circuits for incoming signals from external units.

NSTITUTIONS

- Keeps track of execution of a program

- Contains the memory address of the next instruction to be fetched and executed. **MAR:**

- Holds the address of the location to be accessed.

- I/P of MAR is connected to Internal bus and an O/p to external bus.

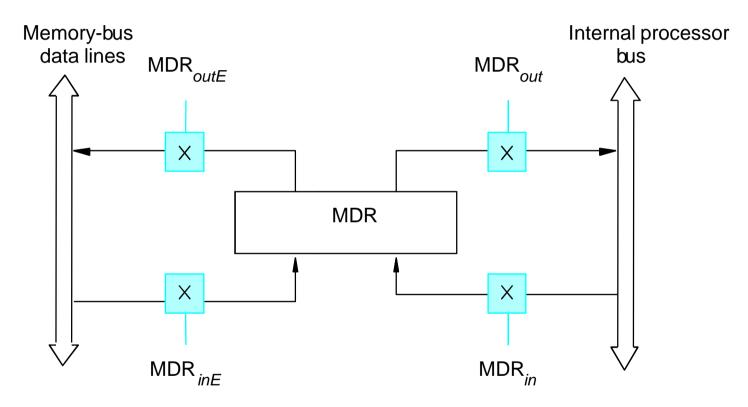

#### <u>MDR:</u>

PC:

- Contains data to be written into or read out of the addressed location.

- IT has 2 inputs and 2 Outputs.

- Data can be loaded into MDR either from memory bus or from internal processor bus.

The data and address lines are connected to the internal bus via MDR and MAR

- The processor registers R0 to Rn-1 vary considerably from one processor to another.

- Registers are provided for general purpose used by programmer.

- Special purpose registers-index & stack registers.

- Registers Y,Z &TEMP are temporary registers used by processor during the execution of some instruction.

#### Multiplexer:

- Select either the output of the register Y or a constant value 4 to be provided as input A of the ALU.

- Constant 4 is used by the processor to increment the contents of PC.

#### ALU:

Used to perform arithmetic and logical operation.

### Data Path:

The registers, ALU and interconnecting bus are collectively referred to as the data path.

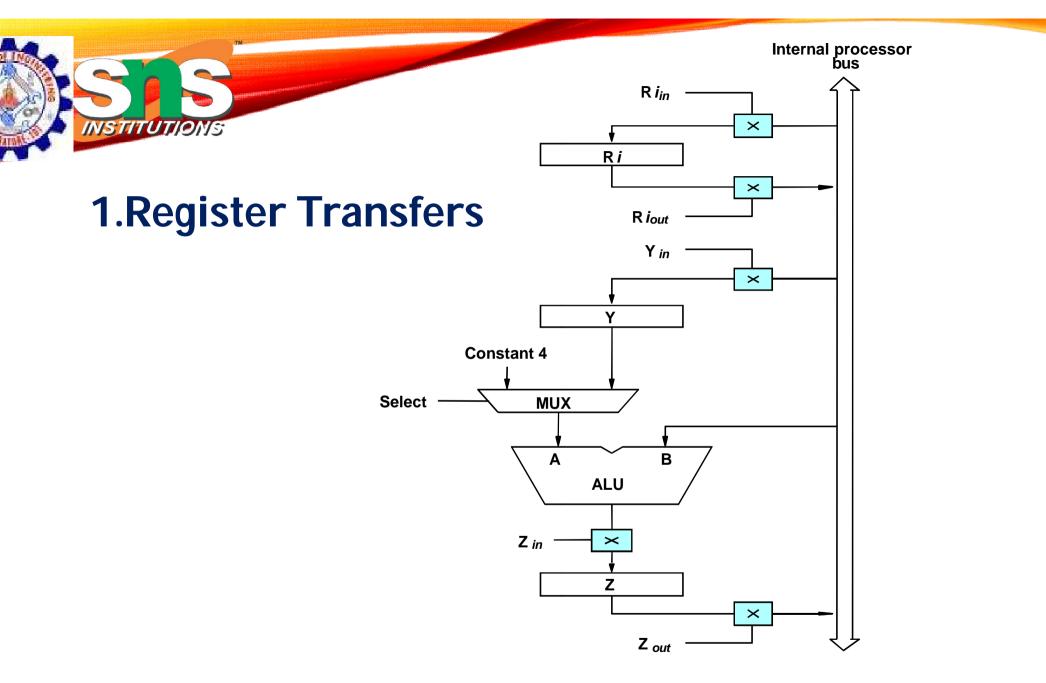

Figure:. Input and output gating for the registers.

- STITUTIONS

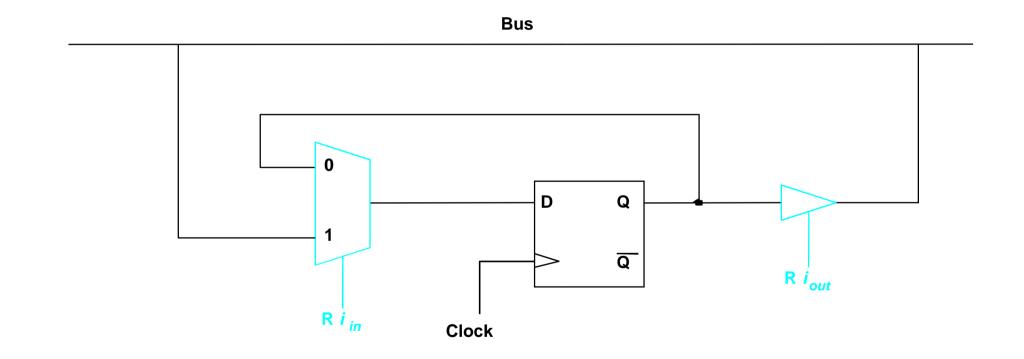

- The input and output gates for register Ri are controlled by signals is  $R_{in}$  and  $R_{iout}$ .

- R<sub>in</sub> Is set to1 data available on common bus are loaded into Ri.

- R<sub>iout</sub> Is set to1 the contents of register are placed on the bus.

- R<sub>iout</sub> Is set to 0 the bus can be used for transferring data from other registers.

#### EX:

Transfer the contents of R1 to R4.

- Enable output of register R1 by setting R1out=1. This places the contents of R1 on the processor bus.

- Enable input of register R4 by setting R4in=1. This loads the data from the processor bus into register R4.

## 2.Performing an Arithmetic or Logic Operation

- The ALU is a combinational circuit that has no internal storage.

- ALU gets the two operands from MUX and bus. The result is temporarily stored in register Z.

- What is the sequence of operations to add the contents of register R1 to those of R2 and store the result in R3?

- 1. R1out, Yin

- 2. R2out, SelectY, Add, Zin

- 3. Zout, R3in

**Step 1:** Output of the register R1 and input of the register Y are

enabled, causing the contents of R1 to be transferred to Y.

**Step 2:** The multiplexer's select signal is set to select Y causing the multiplexer to gate the contents of register Y to input A of the ALU.

**Step 3:** The contents of Z are transferred to the destination register R3.

Figure : Input and output gating for one register bit.

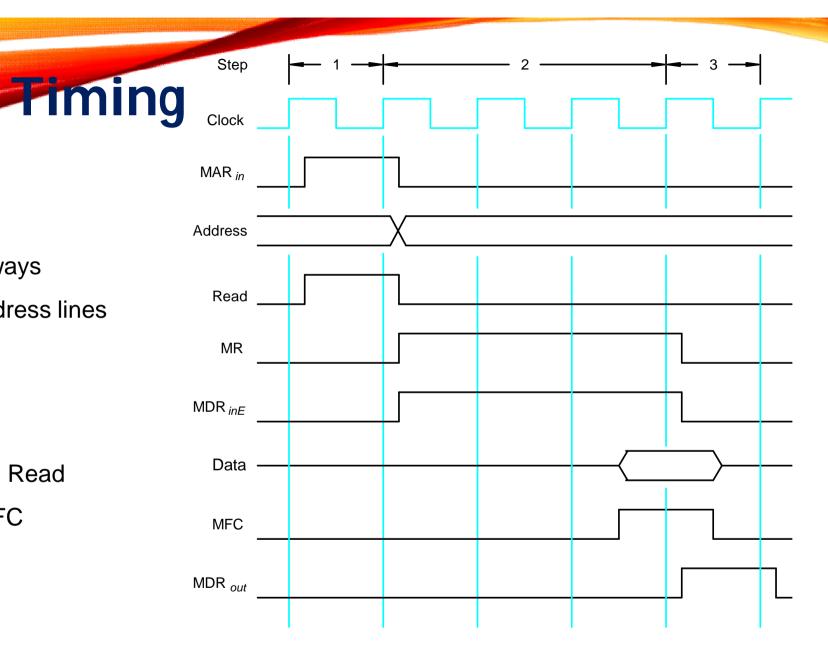

• Address into MAR; issue Read operation; data into MDR.

#### Figure:

Connection and control signals for register MDR.

# Section 3. Fetching a Word from Memory The response time of each memory access varies (cache miss, memory-mapped I/O,...).

- To accommodate this, the processor waits until it receives an indication that the requested operation has been completed (Memory-Function-Completed, MFC).

- Move (R1), R2

- ≻ MAR ← [R1]

- > Start a Read operation on the memory bus

- > Wait for the MFC response from the memory

- ► Load MDR from the memory bus

- ightarrow R2 ← [MDR]

Assume MAR is always available on the address lines of the memory bus.

• Move (R1), R2

VSTITUTIONS

- 1. R1out, MARin, Read

- 2. MDRinE, WMFC

- 3. MDRout, R2in

- Address is loaded into MAR

- Data to be written loaded into MDR.

- Write command is issued.

Example: Move R2,(R1)

R1<sub>out</sub>,MAR<sub>in</sub>

R2<sub>out</sub>,MDR<sub>in</sub>,Write

$MDR_{outE}$ , WMFC

TEXT BOOK

Carl Hamacher, Zvonko Vranesic and Safwat Zaky, "Computer Organization", McGraw-Hill, 6th Edition 2012.

#### REFERENCES

1. David A. Patterson and John L. Hennessey, "Computer organization and design", MorganKauffman ,Elsevier, 5th edition, 2014.

2. William Stallings, "Computer Organization and Architecture designing for Performance", Pearson Education 8th Edition, 2010

3. John P.Hayes, "Computer Architecture and Organization", McGraw Hill, 3rd Edition, 2002

4. M. Morris R. Mano "Computer System Architecture" 3rd Edition 2007

5. David A. Patterson "Computer Architecture: A Quantitative Approach", Morgan Kaufmann; 5th edition 2011

#### **THANK YOU**

Dr.B.Anuradha / ASP / CSE / SEM 3 / COA