# UNIT II ARITHMETIC OPERATIONS

Addition and subtraction of signed numbers – Design of fast adders -Multiplication of positive numbers - Signed operand multiplication- fas multiplication – Integer division – Floating point numbers and operations

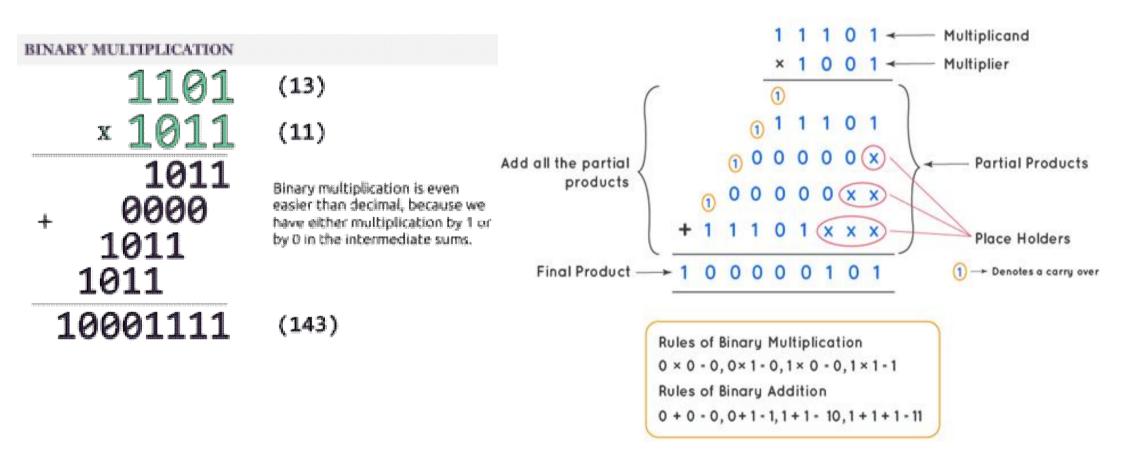

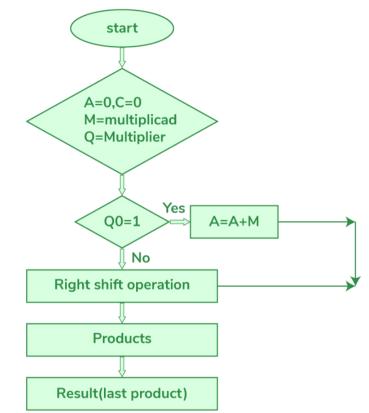

**Manual Multiplication Algorithm**

INSTITUTIONS

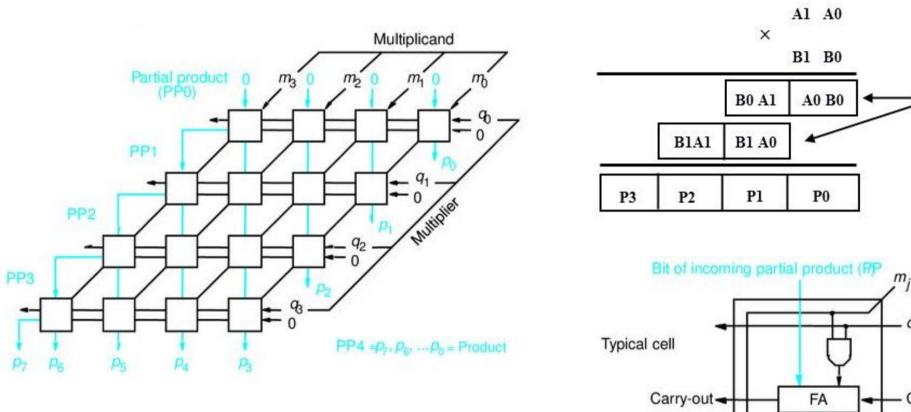

## Array Multiplication of Positive Binary Operands

**Partial products**

P1 = B0 A1 + B1 A0

P3 = Carryout of P2

P2 = B1A1 + Carryout of P1

P0 = A0 B0

q;

Bit of outgoing partial product [PP(1)]

Carry-in

INSTITUTIONS

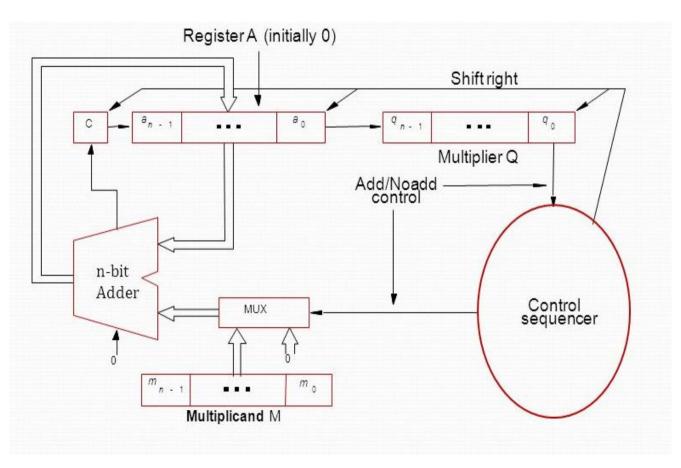

## Sequential Circuit Binary Multiplier

### **Register Configuration**

INSTITUTIONS

Dr.B.Anuradha / ASP / CSE / SEM 2 / COA

## Sequential Circuit Binary Multiplier

|                | 8   | B 1 | 1             | 0 | 1 |   |   |   |   |                |         |

|----------------|-----|-----|---------------|---|---|---|---|---|---|----------------|---------|

| 13 X 11        | C A |     |               |   |   | Q |   |   |   | Initial Values |         |

| 7 X 3          | 0   | 0   | 0             | 0 | 0 | 1 | 0 | 1 | 1 |                |         |

|                | 0   | 1   | 1             | 0 | 1 | 1 | 0 | 1 | 1 | ▲<br>Add       | First   |

| Multiplication | 0   | 0   | 1             | 1 | 0 | 1 | 0 | 0 | 1 | Shift          | Cycle   |

| Example        | 1   | 0   | 0             | 1 | 1 | 1 | 1 | 0 | 1 | Add            | Second  |

|                | 0   | 1   | 0             | 1 | 1 | 1 | 1 | 0 | 0 | Shift          | Cycle   |

|                |     |     |               |   |   |   |   |   |   |                |         |

|                | 0   | 1   | 0             | 0 | 1 | 1 | 1 | 1 | 0 | No Add         | 7 Third |

|                | 0   | 0   | 1             | 0 | 0 | 1 | 1 | 1 | 1 | Shift          | Cycle   |

|                |     |     |               |   |   |   |   |   |   |                |         |

|                | 1   | 0   | 0             | 0 | 1 | 1 | 1 | 1 | 1 | Add            | Fourth  |

|                | 0   | 1   | 0             | 0 | 0 | 1 | 1 | 1 | 1 | Shift          | Cycle   |

|                |     | L   | Final Product |   |   |   |   |   |   |                |         |

NSTITUTIO

Carl Hamacher, Zvonko Vranesic and Safwat Zaky, "Computer Organization", McGraw-Hill, 6th Edition 2012.

#### REFERENCES

1. David A. Patterson and John L. Hennessey, "Computer organization and design", MorganKauffman ,Elsevier, 5th edition, 2014.

2. William Stallings, "Computer Organization and Architecture designing for Performance", Pearson Education 8th Edition, 2010

3. John P.Hayes, "Computer Architecture and Organization", McGraw Hill, 3rd Edition, 2002

4. M. Morris R. Mano "Computer System Architecture" 3rd Edition 2007

5. David A. Patterson "Computer Architecture: A Quantitative Approach", Morgan Kaufmann; 5th edition 2011

#### **THANK YOU**

Dr.B.Anuradha / ASP / CSE / SEM 2 / COA