| Generation           | Main Technology                                         | Representative Systems                                           |  |  |  |

|----------------------|---------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| First (1945-54)      | Vacuum tubes, relays                                    | Machine & assembly language<br>ENIAC, IBM-701                    |  |  |  |

| Second (1955-64)     | Transistors, memories, I/O<br>processors                | Batch processing systems, HLL<br>IBM-7090                        |  |  |  |

| Third (1965-74)      | SSI and MSI integrated circuits<br>Microprogramming     | Multiprogramming / Time sharing<br>IBM 360, Intel 8008           |  |  |  |

| Fourth (1975-84)     | LSI and VLSI integrated circuits                        | Multiprocessors<br>Intel 8086, 8088                              |  |  |  |

| Fifth (1984-90)      | VLSI, multiprocessor on-chip                            | Parallel computing, Intel 486                                    |  |  |  |

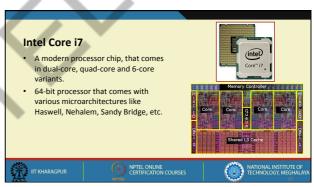

| Sixth (1990 onwards) | ULSI, scalable architecture, post-<br>CMOS technologies | Massively parallel processors<br>Pentium, SUN Ultra workstations |  |  |  |

|                      |                                                         | NATIONAL INSTITUTE OF<br>TECHNOLOGY, MEGHALAY/                   |  |  |  |

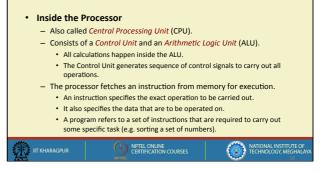

## • What is the role of ALU?

- It contains several registers, some general-purpose and some specialpurpose, for temporary storage of data.

- It contains circuitry to carry out logic operations, like AND, OR, NOT, shift, compare, etc.

- It contains circuitry to carry out arithmetic operations like addition, subtraction, multiplication, division, etc.

- During instruction execution, the data (operands) are brought in and stored in some registers, the desired operation carried out, and the result stored back in some register or memory.

| IIT KHARAGPUR |       | NATIONAL INSTITUTE OF<br>TECHNOLOGY, MEGHALAYA |

|---------------|-------|------------------------------------------------|

|               | NPTEL | 19                                             |

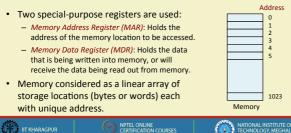

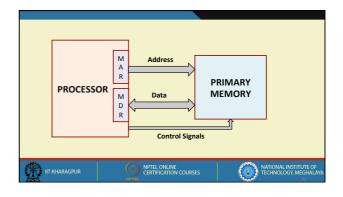

## For Interfacing with the Primary Memory

Address

0

5

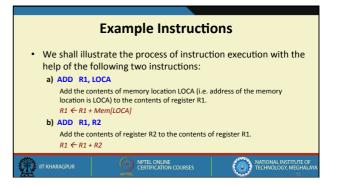

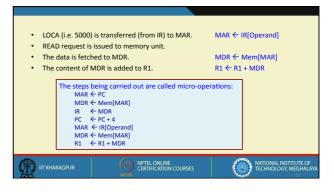

| Execution of ADD R                                                                                  | 1,LOCA                                         |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------|

| <ul> <li>Assume that the instruction is stored in memory lo<br/>is 50, and LOCA is 5000.</li> </ul> | cation 1000, the initial value of R1           |

| <ul> <li>Before the instruction is executed, PC contains 100</li> </ul>                             | 0.                                             |

| <ul> <li>Content of PC is transferred to MAR.</li> </ul>                                            | $MAR \leftarrow PC$                            |

| <ul> <li>READ request is issued to memory unit.</li> </ul>                                          |                                                |

| <ul> <li>The instruction is fetched to MDR.</li> </ul>                                              | MDR ← Mem[MAR]                                 |

| <ul> <li>Content of MDR is transferred to IR.</li> </ul>                                            |                                                |

| <ul> <li>PC is incremented to point to the next instruction.</li> </ul>                             | $PC \leftarrow PC + 4$                         |

| • The instruction is decoded by the control unit.                                                   | ADD R1 5000                                    |

| IIT KHARAGPUR OPTEL ONLINE CERTIFICATION COURSES                                                    | NATIONAL INSTITUTE OF<br>TECHNOLOGY, MEGHALAYA |

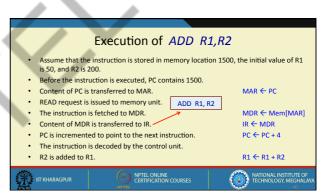

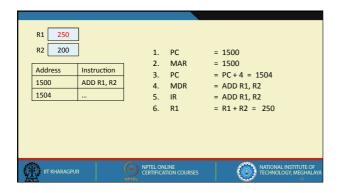

| R1 125                                  |                                   | 1.                                           | PC                                               | _                                              | 1000                                                                                                           |

|-----------------------------------------|-----------------------------------|----------------------------------------------|--------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Address<br>1000<br>1004<br>5000<br>LOCA | Content<br>ADD R1, LOCA<br><br>75 | 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8. | PC<br>MAR<br>PC<br>MDR<br>IR<br>MAR<br>MDR<br>R1 | =<br>=<br>=<br>=                               | 1000<br>1000<br>PC + 4 = 1004<br>ADD R1, LOCA<br>ADD R1, LOCA<br>LOCA = 5000<br>75<br>R1 + MDR = 50 + 75 = 125 |

| IIT KHARAGPU                            | NPTEL O<br>CERTIFIC               | NLINE<br>ATION COURSES                       |                                                  | NATIONAL INSTITUTE OF<br>TECHNOLOGY, MECHALAYA |                                                                                                                |

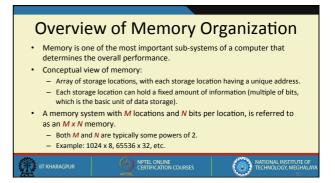

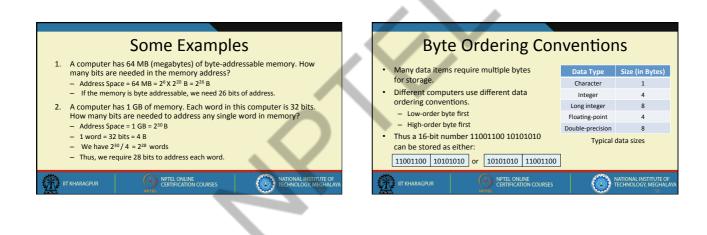

|               | How do we Specify Memory Sizes? |      |                                       |                  |                                         |  |

|---------------|---------------------------------|------|---------------------------------------|------------------|-----------------------------------------|--|

|               | Unit                            |      | Bytes                                 | In Decimal       |                                         |  |

|               | 8 bits                          | (B)  | 1 or 20                               | 100              |                                         |  |

|               | Kilobyte                        | (KB) | 1024 or 2 <sup>10</sup>               | 10 <sup>3</sup>  |                                         |  |

|               | Megabyte                        | (MB) | 1,048,576 or 220                      | 10 <sup>6</sup>  |                                         |  |

|               | Gigabyte                        | (GB) | 1,073,741,824 or 230                  | 10 <sup>9</sup>  |                                         |  |

|               | Terabyte                        | (TB) | 1,099,511,627,776 or 240              | 1012             |                                         |  |

|               | Petabyte                        | (PB) | 2 <sup>50</sup>                       | 10 <sup>15</sup> |                                         |  |

|               | Exabyte                         | (EB) | 2 <sup>60</sup>                       | 10 <sup>18</sup> |                                         |  |

|               | Zettabyte                       | (ZB) | 270                                   | 1021             |                                         |  |

| IIT KHARAGPUR |                                 |      | NPTEL ONLINE<br>CERTIFICATION COURSES |                  | L INSTITUTE OF<br>.OGY, MEGHALAYA<br>54 |  |

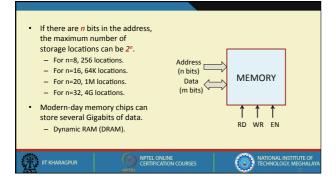

|                                        |                                                              | r                   | , |

|----------------------------------------|--------------------------------------------------------------|---------------------|---|

|                                        | Address                                                      | Contents            |   |

|                                        | 0000 0000                                                    | 0000 0000 0000 0001 |   |

|                                        | 0000 0001                                                    | 0000 0100 0101 0000 |   |

|                                        | 0000 0010                                                    | 1010 1000 0000 0000 |   |

|                                        | :                                                            | :                   | - |

|                                        | 1111 1111                                                    | 1011 0000 0000 1010 |   |

| An example: 2 <sup>8</sup> x 16 memory |                                                              |                     |   |

| IIT KHARAGPUR                          | NPTEL ONLINE<br>CERTIFICATION COURSES OF TECHNOLOGY, MEGALAW |                     |   |

## <section-header><list-item><list-item><list-item><list-item><list-item><list-item>

|               | An Example |                                       |                                                |  |  |  |

|---------------|------------|---------------------------------------|------------------------------------------------|--|--|--|

| • <u>Comp</u> | oute S =   | (A + B) – (C – D)                     |                                                |  |  |  |

| LOAD          | R1,A       |                                       |                                                |  |  |  |

| LOAD          | R2,B       |                                       |                                                |  |  |  |

| ADD           | R3,R1,R2   | // R3 = A + B                         |                                                |  |  |  |

| LOAD          | R1,C       |                                       |                                                |  |  |  |

| LOAD          | R2,D       |                                       |                                                |  |  |  |

| SUB           | R4,R1,R2   | // R4 = C – D                         |                                                |  |  |  |

| SUB           | R3,R3,R4   | // R3 = R3 – R4                       |                                                |  |  |  |

| STORE S,R3    |            |                                       |                                                |  |  |  |

|               | R          | NPTEL ONLINE<br>CERTIFICATION COURSES | NATIONAL INSTITUTE OF<br>TECHNOLOGY, MEGHALAYA |  |  |  |

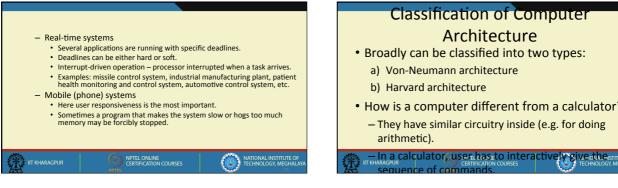

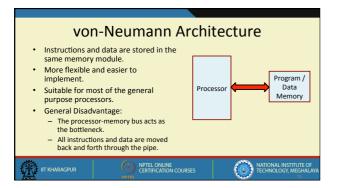

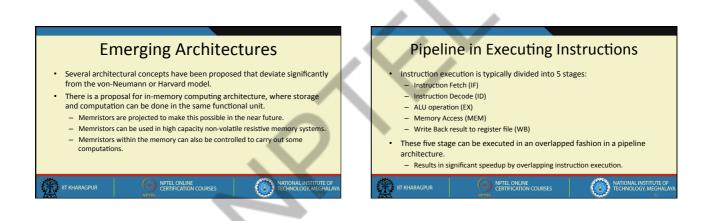

## Classification of Computer Architecture

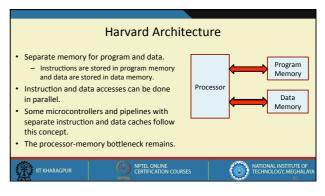

- Broadly can be classified into two types:

- b) Harvard architecture

- How is a computer different from a calculator? - They have similar circuitry inside (e.g. for doing arithmetic).

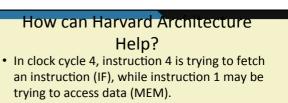

In von-Neumann architecture, one of these two operations will have to wait resulting in pipeline slowdown.

In Harvard architecture, the operations can go on

In Harvard any speed penalty-as the instruction and some of the second secon

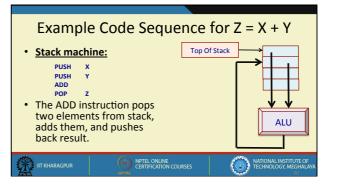

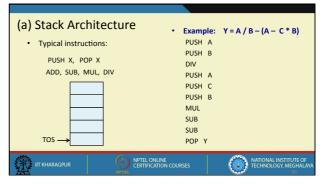

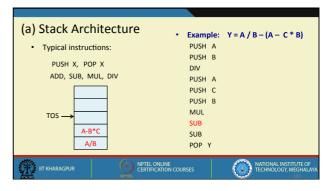

| (a) Stack Architecture | • Example: Y = A / B – (A – C * B)                    |

|------------------------|-------------------------------------------------------|

| Typical instructions:  | PUSH A                                                |

|                        | PUSH B                                                |

| PUSH X, POP X          | DIV                                                   |

| ADD, SUB, MUL, DIV     | PUSH A                                                |

|                        | PUSH C                                                |

|                        | PUSH B                                                |

|                        | MUL                                                   |

|                        | SUB                                                   |

| B                      | SUB                                                   |

| A                      | POP Y                                                 |

| IIT KHARAGPUR          | DURSES NATIONAL INSTITUTE OF<br>TECHNOLOGY, MEGHALAYA |

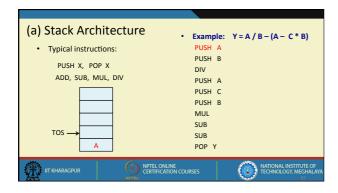

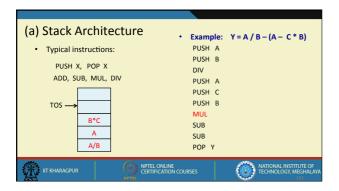

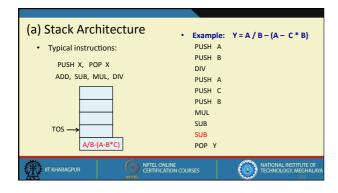

| 4 | (a) Stack Architect                       | Ure • Example: Y = A / B - (A - C * B)                                                     |

|---|-------------------------------------------|--------------------------------------------------------------------------------------------|

|   | <ul> <li>Typical instructions:</li> </ul> | PUSH A                                                                                     |

|   |                                           | PUSH B                                                                                     |

|   | PUSH X, POP X                             | DIV                                                                                        |

|   | ADD, SUB, MUL, DIV                        | PUSH A                                                                                     |

|   | TOS ->                                    | PUSH C                                                                                     |

|   | В                                         | PUSH B                                                                                     |

|   | C                                         | MUL                                                                                        |

|   |                                           | SUB                                                                                        |

|   | A                                         | SUB                                                                                        |

|   | A/B                                       | POP Y                                                                                      |

|   | IT KHARAGPUR                              | NPTEL ONLINE     CERTIFICATION COURSES     NATIONAL INSTITUTE OF     TECHNOLOGY, MEGHALAYA |

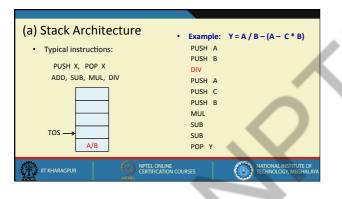

| (a) Stack Architecture                    | • Example: Y = A / B – (A – C * B)                   |

|-------------------------------------------|------------------------------------------------------|

| <ul> <li>Typical instructions:</li> </ul> | PUSH A                                               |

|                                           | PUSH B                                               |

| PUSH X, POP X                             | DIV                                                  |

| ADD, SUB, MUL, DIV                        | PUSH A                                               |

|                                           | PUSH C                                               |

|                                           | PUSH B                                               |

|                                           | MUL                                                  |

|                                           | SUB                                                  |

|                                           | SUB                                                  |

|                                           | POP Y Y = RESULT                                     |

|                                           | DURSES NATIONAL INSTITUTE OF<br>TECHNOLOGY, MEGALAYA |

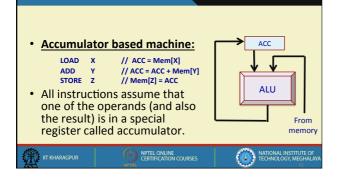

| (b) Accumulator Architecture | Example: $Y = A / B - (A - C * B)$ |

|------------------------------|------------------------------------|

|                              | LOAD C                             |

| Typical instructions:        | MUL B                              |

| LOAD X, STORE X              | STORE D // D = C*B                 |

| ADD X, SUB X, MUL X, DIV X   | LOAD A                             |

|                              | SUB D                              |

|                              | STORE D // D = A – C*B             |

|                              | LOAD A                             |

|                              | DIV B                              |

|                              | SUB D                              |

|                              | STORE Y                            |

|                              | NATIONAL INSTITUTE OF              |

|                              | COURSES TECHNOLOGY, MEGHALA        |

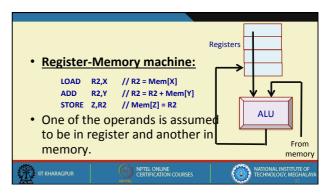

| <ul> <li>(c) Memory-Memory Architecture</li> <li>Typical instructions (3 operands):<br/>ADD x, Y, Z<br/>SUB X, Y, Z<br/>MUL X, Y, Z</li> <li>Typical instructions (2 operands):<br/>MOV X, Y<br/>ADD X, Y<br/>SUB X, Y<br/>MUL X, Y</li> </ul> | Example: Y = A / B - (A - C * B)<br>DIV A,B,D<br>MUL E,C,B<br>SUB E,A,E<br>SUB Y,D,E<br>MOV D,A<br>DIV D,B<br>MOV E,C<br>MUL E,B<br>SUB A,E<br>SUB D,A |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| IIT KHARAGPUR                                                                                                                                                                                                                                  | NATIONAL INSTITUTE OF                                                                                                                                  |

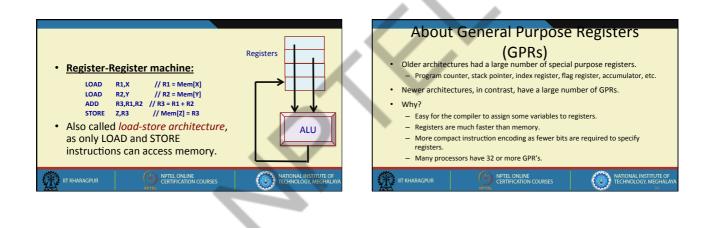

| (d) Load-Store Archite<br>• Typical instructions:<br>LOAD R1,X<br>STORE Y,R2<br>ADD R1,R2,R3<br>SUB R1,R2,R3 | LOAD | R2,B<br>R3,C<br>R4,R1,R2<br>R5,R3,R2<br>R5,R1,R5<br>R4,R4,R5 |

|--------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------|

| IIT KHARAGPUR                                                                                                |      | NATIONAL INSTITUTE OF<br>TECHNOLOGY, MEGHALAYA               |

24/07/17