Performance – Memory locations and addresses – Memory operations – nstruction and Instruction sequencing — Addressing modes – Assembly anguage – Case study: RISC and CISC Architecture.

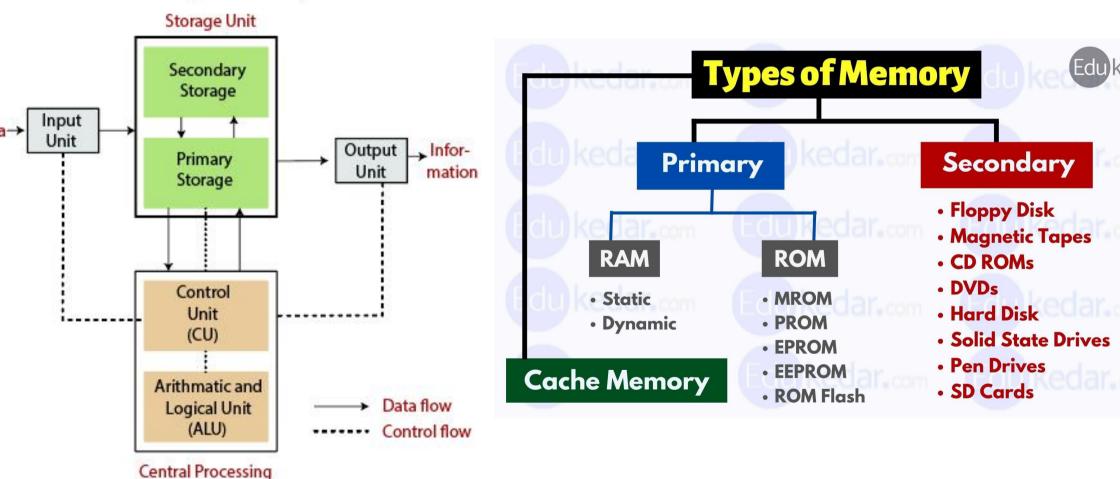

#### Block diagram of Computer

## Functional Unit

4/14

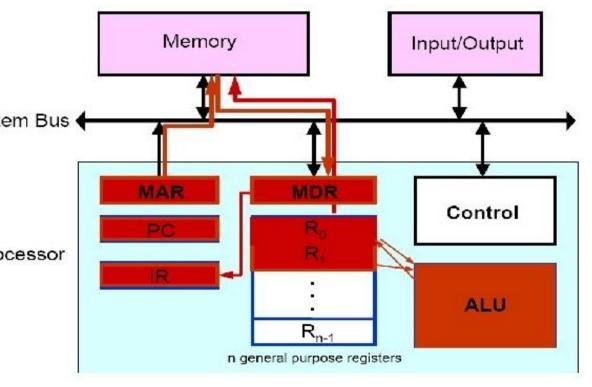

# Analysing how processor and memory are connected

- Processors have various registers to perform various functions

- Program Counter It contains the memory address of next instruction to be fetched.

- Instruction Register It holds the instruction which is currently being executed

- MDR It facilities communication with memory. It contains the data to be written into or read out of the addressed location.

- MAR It holds the address of the location that is to be accessed n general purpose registers that is R0 to Rn-1

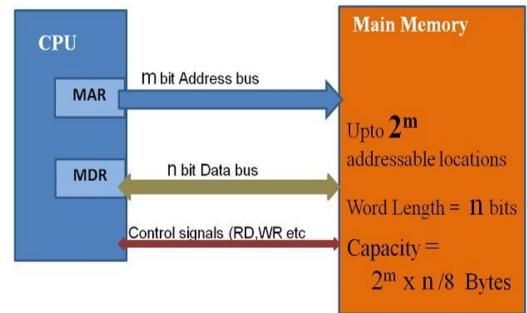

# Connection between Processor & Memory

## **Basic Operational Concepts**

Instruction consists of 2 parts

OPCODE

**OPERANDS**

Example

ADD LOCA, RO

Load LOCA, R1 Add R1, R0

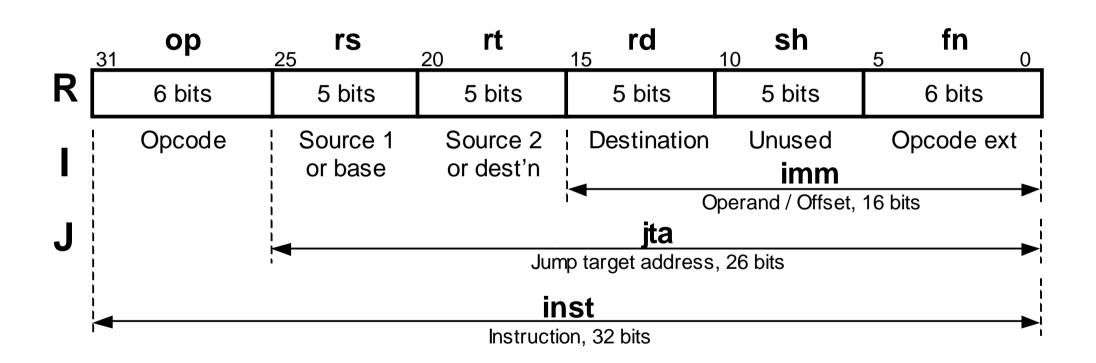

## **Instructions Format**

| rs     | rt     | rd                  | shamt                    | funct                                     |  |

|--------|--------|---------------------|--------------------------|-------------------------------------------|--|

| 5 bits | 5 bits | 5 bits              | 5 bits                   | 6 bits                                    |  |

|        |        |                     |                          |                                           |  |

| rs     | rt     | constant or address |                          |                                           |  |

| 5 bits | 5 bits | 16 bits             |                          |                                           |  |

|        | 5 bits | 5 bits 5 bits rs rt | 5 bits 5 bits rs rt cons | 5 bits 5 bits 5 bits rs rt constant or ac |  |

| ор     | Target Address |

|--------|----------------|

| 6 bits | 26 bits        |

### **Instructions Format**

9/1/

# Translating Arm Assembly Instructions into Machine Instructions

| op     | rs  | 6       | rt     | rd           | sham   | t fund | ct    | add \$t0, \$s1, \$s2 |   |

|--------|-----|---------|--------|--------------|--------|--------|-------|----------------------|---|

| 6 bits | 5 b | its     | 5 bits | 5 bits       | 5 bits | 6 bit  |       |                      |   |

|        |     |         |        |              |        |        |       | _                    | • |

|        |     | special |        | <b>\$</b> s1 | \$s2   | \$tO   | 0     | add                  |   |

|        |     |         |        |              |        |        | •     | •                    |   |

|        |     |         | 0      | 17           | 18     | 8      | 0     | 32                   |   |

|        | _   |         |        |              |        |        |       |                      |   |

|        |     | 00      | 0000   | 10001        | 10010  | 01000  | 00000 | 100000               |   |

$00000010001100100100000000100000_2 = 02324020_{16}$

## **Operating System**

### **TEXT BOOK**

Carl Hamacher, Zvonko Vranesic and Safwat Zaky, "Computer Organization", McGraw-Hill, 6th Edition 2012.

#### **REFERENCES**

- 1. David A. Patterson and John L. Hennessey, "Computer organization and design", MorganKauffman ,Elsevier, 5th edition, 2014.

- 2. William Stallings, "Computer Organization and Architecture designing for Performance", Pearson Education 8th Edition, 2010

- 3. John P.Hayes, "Computer Architecture and Organization", McGraw Hill, 3rd Edition, 2002

- 4. M. Morris R. Mano "Computer System Architecture" 3rd Edition 2007

- 5. David A. Patterson "Computer Architecture: A Quantitative Approach", Morgan Kaufmann; 5th edition 2011

### **THANK YOU**