# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

### **19ECT221 – MICROPROCESSORS AND MICROCONTROLLERS**

### **II YEAR - IV SEM**

UNIT 3–8051 MICROCONTROLLER

## **SPECIAL FUNCTION REGISTERS**

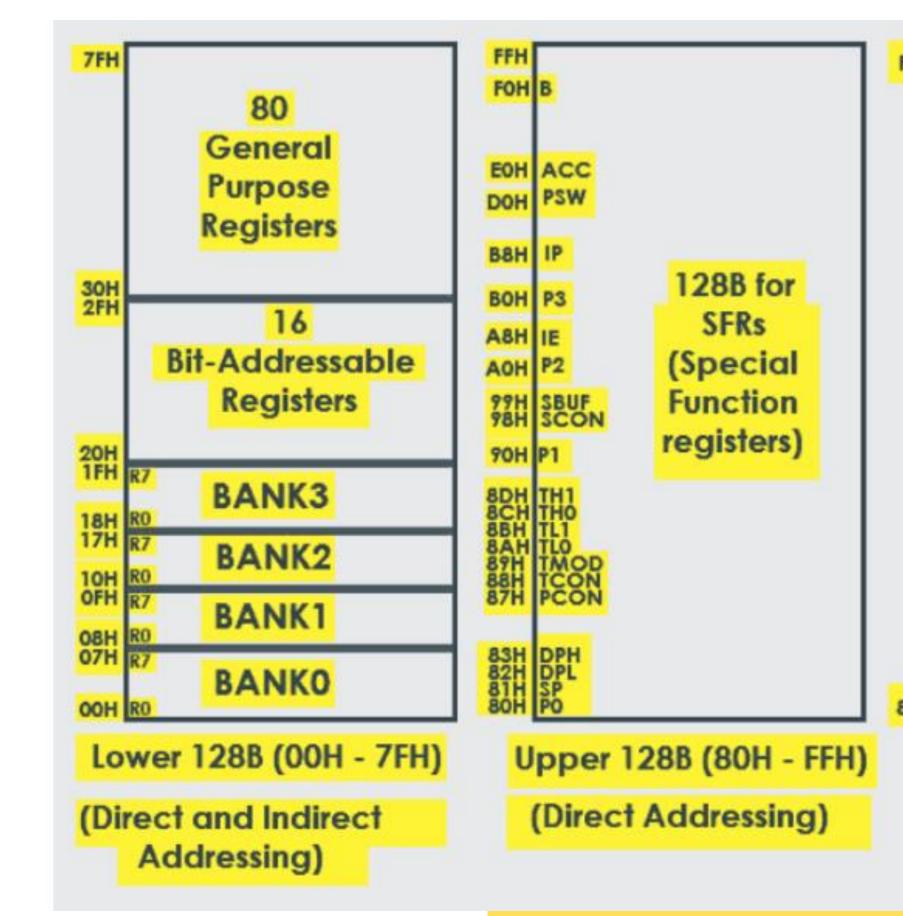

The internal RAM or Data Memory of the 8051 Microcontroller is divided in to General Purpose Registers, Bit Addressable Registers, Register Banks and Special Function Registers or SFRs. The 8051 Microcontroller Special Function Registers are used to program and control different hardware peripherals like Timers, Serial Port, I/O Ports etc.

> By manipulating the 8051 Microcontroller Special Function Registers (SFRs), you can assess or change the operating mode of the 8051 Microcontroller.

# DATA MEMORY(RAM) OF 8051

### (Indirect Addressing)

### **CATEGORY OF SFRs**

| Name of the Register | Function                     | Internal RAM Address (HEX)<br>E0H |  |  |

|----------------------|------------------------------|-----------------------------------|--|--|

| ACC                  | Accumulator                  |                                   |  |  |

| В                    | B Register (for Arithmetic)  | F0H                               |  |  |

| DPH                  | Addressing External Memory   | 83H                               |  |  |

| DPL                  | Addressing External Memory   | 82H                               |  |  |

| IE                   | Interrupt Enable Control     | A8H                               |  |  |

| IP                   | Interrupt Priority           | B8H                               |  |  |

| P0                   | PORT 0 Latch                 | 80H                               |  |  |

| P1                   | PORT 1 Latch                 | 90H                               |  |  |

| P2                   | PORT 2 Latch                 | A0H                               |  |  |

| P3                   | PORT 3 Latch                 | B0H                               |  |  |

| PCON                 | Power Control                | 87H                               |  |  |

| PSW                  | Program Status Word          | D0H                               |  |  |

| SCON                 | Serial Port Control          | 98H                               |  |  |

| SBUF                 | Serial Port Data Buffer      | 99H                               |  |  |

| SP                   | Stack Pointer                | ONICS FUE 81H                     |  |  |

| TMOD                 | Timer / Counter Mode Control | 89H                               |  |  |

| TCON                 | Timer / Counter Control      | 88H                               |  |  |

| TL0                  | Timer 0 LOW Byte             | 8AH                               |  |  |

| TH0                  | Timer 0 HIGH Byte            | 8CH                               |  |  |

| TL1                  | Timer 1 LOW Byte             | 8BH                               |  |  |

| TH1                  | Timer 1 HIGH Byte            | 8DH                               |  |  |

### **CATEGORY OF SFRs**

>Math or CPU Registers: A and B Status Register: PSW (Program Status Word) > Pointer Registers: DPTR (Data Pointer – DPL, DPH) and SP (Stack Pointer) I/O Port Latches: P0 (Port 0), P1 (Port 1), P2 (Port 2) and P3 (Port 3) > Peripheral Control Registers: PCON, SCON, TCON, TMOD, IE and IP > Peripheral Data Registers: TL0, TH0, TL1, TH1 and **SBUF**

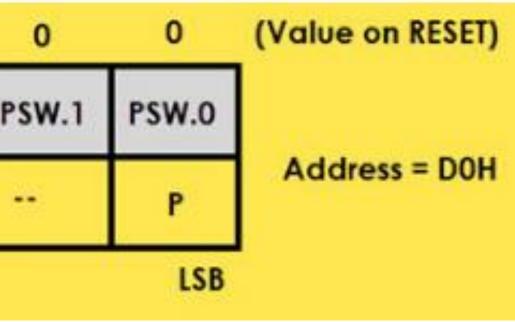

## **CATEGORY OF SFRs – Program Status Word**

The PSW or Program Status Word Register is also called as Flag Register and is one of the important SFRs.

> The PSW Register consists of Flag Bits, which help the programmer in checking the condition of the result and also make decisions.

Flags are 1-bit storage elements that store and indicate the nature of the result that is generated by execution of certain instructions.

$\succ$  The following image shows the contents of the PSW Register.

|     | 0     | 0     | 0     | 0     | 0     | 0     |   |

|-----|-------|-------|-------|-------|-------|-------|---|

|     | PSW.7 | PSW.6 | PSW.5 | PSW.4 | PSW.3 | PSW.2 | P |

| PSW | СҮ    | AC    | FO    | RS1   | RSO   | ov    |   |

|     | MSB   |       |       |       |       |       |   |

## **CATEGORY OF SFRs – Program Status Word**

|        | FLAG NAME |               |     | SYMBOL  | BIT |

|--------|-----------|---------------|-----|---------|-----|

| U      | Carry     |               |     | C or CY | 7   |

|        |           | AC            | 6   |         |     |

|        |           | FO            | 5   |         |     |

|        | n Bit 1   | Bank Selectio | RS1 | 4       |     |

|        | n Bit 1   | RS0           | 3   |         |     |

|        | Bank      | RS0           | RS1 |         |     |

|        | Bank 0    | 0             | 0   |         |     |

|        | Bank 1    | 1             | 0   |         |     |

|        | Bank 2    | 0             | 1   |         |     |

|        | Bank 3    | 1             | 1   |         |     |

|        |           | Overflow      | OV  | 2       |     |

| Ma     | Reserved  |               |     |         | 1   |

| Set to |           | Р             | 0   |         |     |

### DESCRIPTION

Ised in Arithmetic, Logic & Boolean Operations

Used in BCD Arithmetic

General Purpose User Flag

Used in Arithmetic Operations

ay be used as a General Purpose Flag

1 if A has odd # of 1's; otherwise Reset

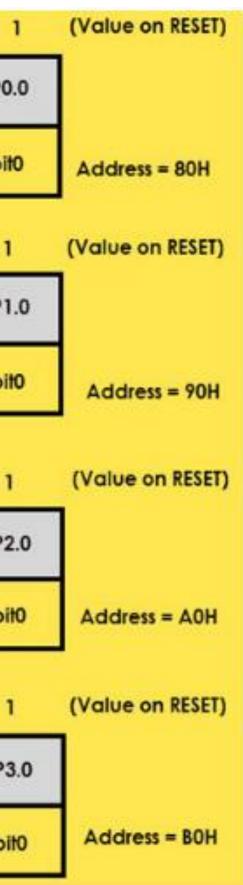

# **CATEGORY OF SFRs –I/O Ports** $\succ$ The 8051 Microcontroller four Ports which can be used as Input and/or Output $2^{2772}$

- $\succ$  These four ports are P0, P1, P2 and P3. The addresses of the Port Registers are as follows: P0 – 80H, P1 – 90H, P2 – A0H and P2 – B0H. Each bit in these SFRs corresponds to one physical Pin in the 8051 Microcontroller. All these Port Registers are both Bit Addressable and Byte Addressable. Writing 1 or 0 on a Port Register Bit will reflect as an appropriate voltage (5V and 0V) on the corresponding Pin.

- $\blacktriangleright$  If a Port Bit is SET (declared as 1), the corresponding Port Pin will be configured as Input and similarly if a Port Bit is CLEARED (declared as 0), the corresponding Port Pin is configured as Output. Upon reset, all the Port Bits are SET (1) and hence, all the Port Pins are configured as Inputs.

## **CATEGORY OF SFRs –I/O Ports**

|    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1   |

|----|------|------|------|------|------|------|------|-----|

|    | P0.7 | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | PO  |

| PO | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit |

|    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1   |

|    | P1.7 | P1.6 | P1.5 | P1.4 | P1.3 | P1.2 | P1.1 | P1  |

| P1 | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit |

|    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1   |

|    | P2.7 | P2.6 | P2.5 | P2.4 | P2.3 | P2.2 | P2.1 | P2  |

| P2 | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bi  |

|    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1   |

|    | P3.7 | P3.6 | P3.5 | P3.4 | P3.3 | P3.2 | P3.1 | P3  |

| P3 | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bi  |

19ITT204- Interfacing Requ<mark>irements /M.BHUVANESWARI/ECE/SNSCT</mark>

# References

https://www.electronicshub.org/8051-microcontroller-special-function-registers/

https://rcet.org.in/uploads/academics/rohini\_38214305809.pdf

Ramesh S.Gaonkar," Microprocessor – Architecture, Programming and Applications with the 8085", Penram International Publisher,7<sup>th</sup> Ed., 2016

19ITT204-8086 Addressing modes /M.BHUVANESWARI/ECE/SNSCT

Thank You

10/11