# SNS COLLEGE OF TECHNOLOGY

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

# 19ECT221 - MICROPROCESSORS AND MICROCONTROLLERS

II YEAR - IV SEM

UNIT 2- ALARM CONTROLLER

# **Alarm Controller Case Study**

Design a pre-settable alarm system using 8253/54 timer. Usethumbwheel switches to accept 4 digit value in seconds. Alarm should last for5 seconds. Do not use interrupt

# **Alarm Controller**

NSTITUTIONS

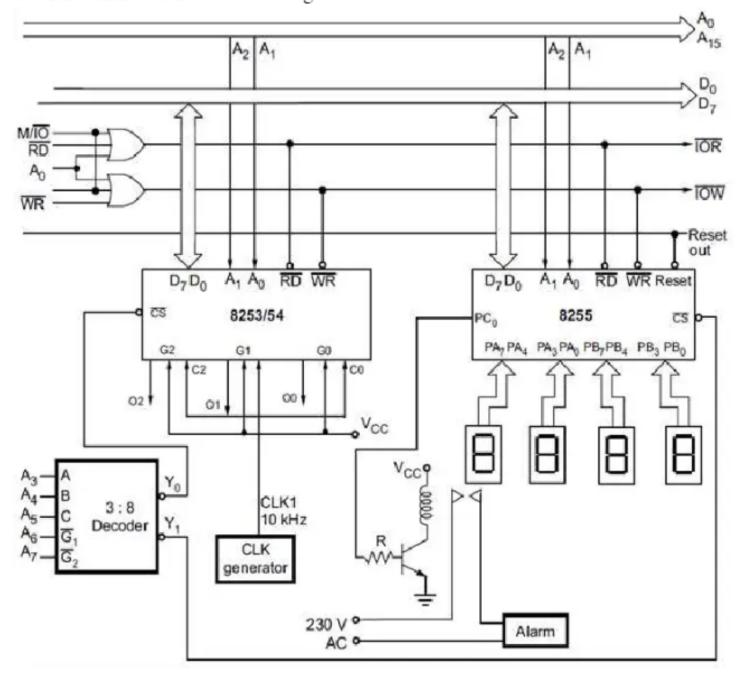

**Solution:** Fig shows the 8086 microprocessor based pre-settable alarm system. Thumbwheel switches are interfaced through 8255 ports. Timing parameters are derived from the 8253/54. 74LS138 decoder is used to generate chip select signals for 8253/54 and 8255. One more 74LS138 decoder is used to generate TOR, TOW, MEMR, and MEMW signals.

f=10 kHz

clock period  $t = 1/f = 1/10x10^3 = 100\mu sec$

Count =

$$\frac{\text{Required Period}}{\text{Clock Period}} = \frac{1 \text{ sec.}}{100 \text{ µs}} = 10000 = 2710 \text{H}$$

This count value is loaded in the count register of the counter 1 and counter 1 is programmed in mode 2 to generate square wave with frequency 1 Hz. The output of counter 1 is fed to the clock input of counter 0 and counter 2. To read four digit of count, we need four thumbwheels. One thumbwheel switch can be interfaced using four input lines. So to interface four thumbwheels we need 16 lines. The IC 8255 is used to interface these thumbwheel switches. Two thumbwheel switches are connected to port A and other two are connected to port B.

Address Mapping:

| Ports/           | Address Lines  |       |       |       |       |       |       |       | Address |

|------------------|----------------|-------|-------|-------|-------|-------|-------|-------|---------|

| Control Register | A <sub>7</sub> | $A_6$ | $A_5$ | $A_4$ | $A_3$ | $A_2$ | $A_1$ | $A_0$ | 1       |

| Counter 0        | 0              | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 00H     |

| Counter 1        | 0              | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 02H     |

| Counter 2        | 0              | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 04H     |

| Control Register | 0              | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 06H     |

| Port A           | 0              | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 08H     |

| Port B           | 0              | 0     | 0     | 0     | 1     | 0     | 1     | 0     | 0AH     |

| Port C           | 0              | 0     | 0     | 0     | 1     | 1     | 0     | 0     | 0CH     |

| Control Register | 0              | 0     | 0     | 0     | 1     | 1     | 1     | 0     | 0EH     |

## 1. Control Word to Read/Write value in count register of counter 0 of 8254

| $D_7$  | $D_6$  | $D_5$  | $D_4$  | $D_3$ | $D_2$ | $D_1$  | $D_0$ |      |

|--------|--------|--------|--------|-------|-------|--------|-------|------|

| $SC_1$ | $SC_0$ | $RW_1$ | $RW_0$ | $M_2$ | $M_1$ | $-M_0$ | BCD   |      |

| 0      | 0      | 1      | 1      | 0     | 0     | 0      | 1     | =31H |

D0=1; BCD count

D3, D2, D1=000; Mode: interrupt on terminal count

D5, D4=11; Read/write lower byte first and then higher byte

D7, D6=00; Counter 0

### 2. Control Word to Read/Write value in count register of counter 1 of 8254

|   | $D_7$  | $D_6$  | $D_5$           | $D_4$  | $D_3$ | $D_2$ | $D_1$ | $D_0$ |      |

|---|--------|--------|-----------------|--------|-------|-------|-------|-------|------|

|   | $SC_1$ | $SC_0$ | RW <sub>1</sub> | $RW_0$ | $M_2$ | $M_1$ | $M_0$ | BCD   |      |

| ĺ | 0      | 1      | 1               | 1      | 0     | 1     | 1     | 1     | =77H |

D0=1; BCD count

D3, D2, D1=011; Mode: Square wave rate generator

D5, D4=11; Read/write lower byte first and then higher byte

D7, D6=01; Counter 1

# 3. Control Word to latch value in count register of counter 0 of 8254

| $D_7$  | $D_6$  | $D_5$           | $D_4$  | $D_3$ | $D_2$ | $D_1$  | $D_0$ |      |

|--------|--------|-----------------|--------|-------|-------|--------|-------|------|

| $SC_1$ | $SC_0$ | RW <sub>1</sub> | $RW_0$ | $M_2$ | $M_1$ | $-M_0$ | BCD   |      |

| 0      | 0      | 0               | 0      | 0     | 0     | 0      | 1     | =01H |

D0=1; BCD count

D3, D2, D1=000; Mode: interrupt on terminal count

D5, D4= 00; counter latch command

D7, D6=00; Counter 0

## 4. Control Word to Read/Write value in count register of counter 2 of 8254

| $D_7$  | $D_6$  | $D_5$           | $D_4$  | $D_3$ | $D_2$ | $D_1$ | $D_0$ | _     |

|--------|--------|-----------------|--------|-------|-------|-------|-------|-------|

| $SC_1$ | $SC_0$ | RW <sub>1</sub> | $RW_0$ | $M_2$ | $M_1$ | $M_0$ | BCD   | ]     |

| 1      | 0      | 1               | 1      | 0     | 0     | 0     | 1     | = B1H |

D0=1; BCD count

D3, D2, D1=000; Mode: interrupt on terminal count

D5, D4=11; Read/write lower byte first and then higher byte

D7, D6=10; Counter 2

## 5. Control Word to latch value in count register of counter 2 of 8254

| $D_7$  | $D_6$  | $D_5$           | $D_4$  | $D_3$ | $D_2$ | $D_1$  | $D_0$ | _     |

|--------|--------|-----------------|--------|-------|-------|--------|-------|-------|

| $SC_1$ | $SC_0$ | RW <sub>1</sub> | $RW_0$ | $M_2$ | $M_1$ | $-M_0$ | BCD   |       |

| 1      | 0      | 0               | 0      | 0     | 0     | 0      | 1     | = 81H |

D0=1; BCD count

D3, D2, D1=000; Mode: interrupt on terminal count

D5, D4=00; counter latch command

D7, D6=10; Counter 2

## 6. Control Word to initialize 8255: Port A=I/P, Port B=I/P, Port C=O/P

| $D_7$  | $D_6$  | $D_5$ | $D_4$ | $D_3$  | $D_2$     | $D_1$ | $D_0$  |       |

|--------|--------|-------|-------|--------|-----------|-------|--------|-------|

| BSR/IO | Mode A |       | PA    | $PC_H$ | Mode B PB |       | $PC_L$ |       |

| 1      | 0      | 0     | 1     | 0      | 0         | 1     | 0      | = 92H |

### Program:

MOV AL, 92H ; Load control word in the control register of 8255

OUT 0EH, AL

START: IN AL, 08H ; Get the lower two digit of count from Port A

MOV BL, AL ; Store the lower two digit of the count in BL register

IN AL, 0AH ; Get the higher two digit of count from Port B

MOV BH, AL ; Store the higher two digit of the count in BH register

MOV AL, 31H ; Load control word (31H) in the control register of 8254

OUT 06, AL

MOV AL, BL ; Load 16-bit Count in count register of counter 0

OUT 00, AL ; Load lower byte of the count

MOV AL, BH

OUT 00, AL ; Load higher byte of the count

BACK: MOV AL, 01H ; Load control word (01H) in control register to latch

OUT 06, AL ; 16-bit count in the count register of counter 0

IN AL, 00H ; Get the lower two digit of count from counter 0

CMP AL, 00H ; Compare with zero

JNZ BACK ; Repeat

IN AL, 00H ; Get the higher two digit of count from counter 0

CMP AL, 00H ; Compare with zero

JNZ BACK ; Repeat

MOV AL, 01H ; Load bit pattern to run alarm

OUT 0CH, AL ; Send it to Port C

CALL DELAY ; Wait for 5 seconds

MOV AL, 00H ; Load bit pattern to stop alarm

OUT 0CH, AL ; Send it to Port C

JMP START ; Repeat

#### Delay Routine:

This delay routine gives a delay of 5 seconds. Counter1 of 8253/54 is used to give delay of 1 second. As output of counter1 is used as a clock for counter2, the count in the counter2 acts as a multiplying factor. Therefore, by loading 05H in the count register of counter2 we get a delay of 5 (5x1) seconds.

OUT 06, AL

MOV AL, 10H ; Load lower byte of the count in counter1

OUT 02, AL

; Load higher byte of the count in counter1 MOV AL, 27H

OUT 02H, AL

MOV AL, B1H ; Load control word in the control register of 8254

OUT 06H, AL ; to write a value in the count register of counter2. MOV AL, 05H ; Load lower byte 05H in the count register of

OUT 04, AL ; counter2

; Loads higher byte 00H in the count register of MOV AL, 00H

OUT 04, AL ; counter2

LP1: MOV AL, 81H ; Load control word (81H) in the control register to

> OUT 06, AL ; latch 16-bit count in the count register of counter2 ; Get the lower two digits of the count from counter2 IN AL, 04H

CMP AL, 00 ; Compare with 00H JNZ LP1 ; If not zero, Repeat

; Get the higher two digits of the count from counter2 IN AL, 04H

; Return to main program

; Compare with 00H CMP AL, 00 JNZ LP1 ; If not zero, Repeat RET

# References

https://www.scribd.com/document/691553361/Unit-3-Alarm-controller

Yu-Cheng Liu, Glenn A.Gibson, Micrcomputer systems: The 886/8088 Family – Architecture, Prgramming and Design, Second Edition, Prentice Hall of India, 2007