# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

### **19ECT221 – MICROPROCESSORS AND MICROCONTROLLERS**

### **II YEAR - IV SEM**

UNIT 2 – 8257 DMA Controller

# **8257-DMA Controller**

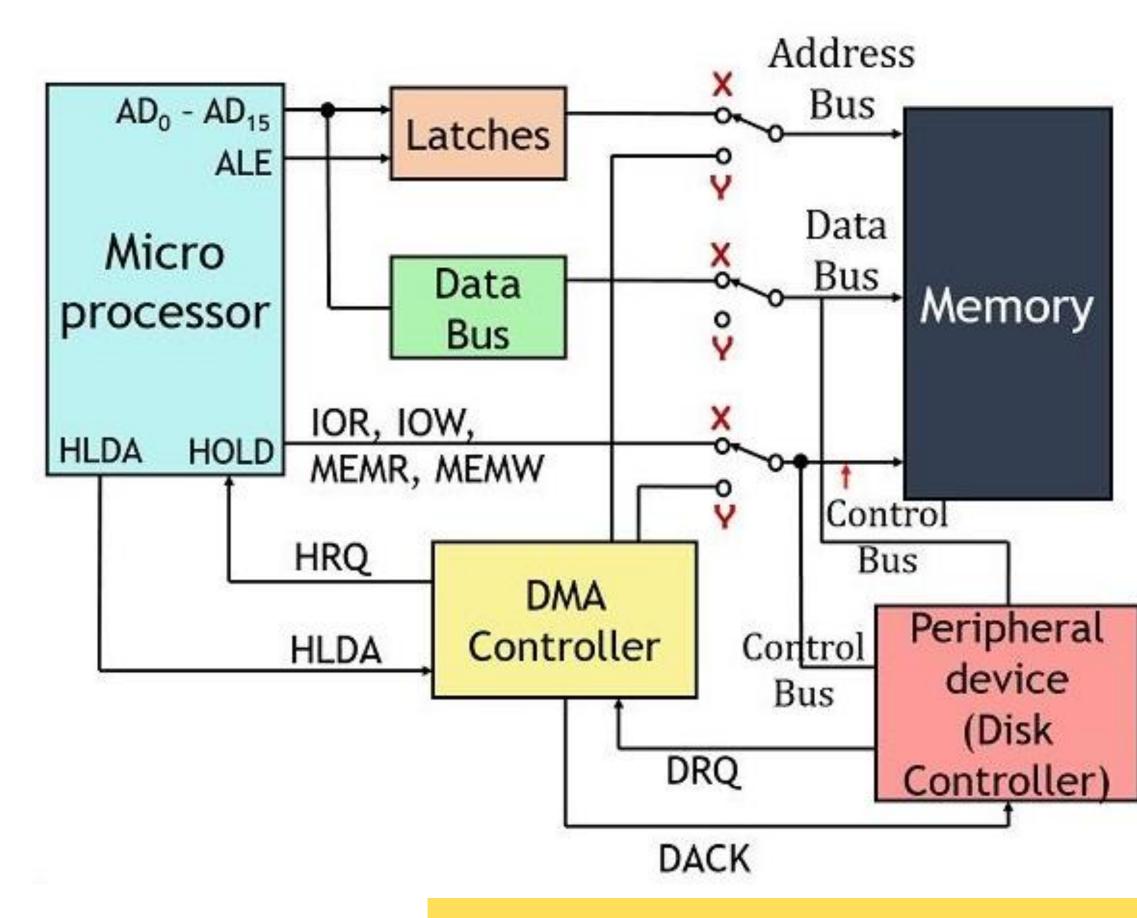

>DMA stands for Direct Memory Access designed by Intel to transfer data at the fastest rate.

$\blacktriangleright$  It allows the device to transfer the data directly to/from memory without any interference of the CPU.

$\succ$ Using a DMA controller, the device requests the CPU to hold its data, address and control bus, so the device is free to transfer data directly to/from the memory.

The DMA data transfer is initiated only after receiving HLDA signal from the CPU.

# **Sequence of DMA Operation**

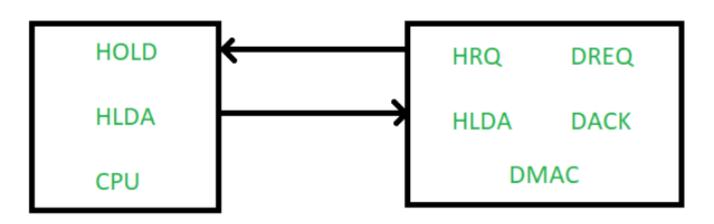

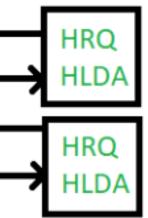

$\succ$  Initially, the device has to send DMA request (DRQ) to DMA controller.  $\succ$  The DMA controller sends Hold request (HRQ) to the CPU and waits for the CPU to assert the HLDA.

$\succ$  Then the microprocessor tri-states all the data bus, address bus, and control bus. The CPU leaves the control over bus and acknowledges the HOLD request through HLDA signal.  $\triangleright$ Now the CPU is in HOLD state and the DMA controller has to manage the operations over buses between the CPU, memory, and I/O devices.

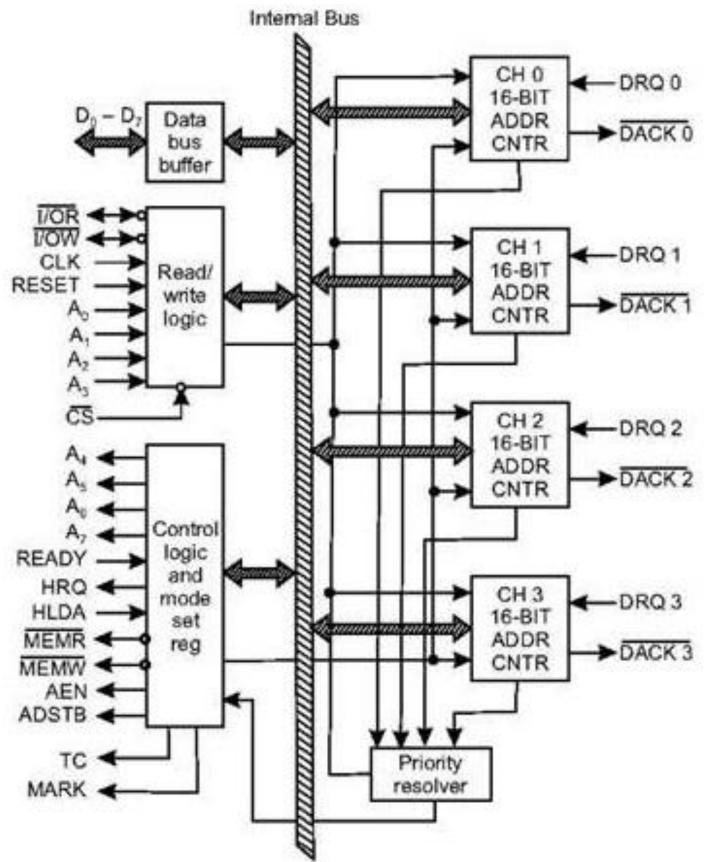

### Architecture of 8257

## Architecture of 8257

### **Modes of DMAC**

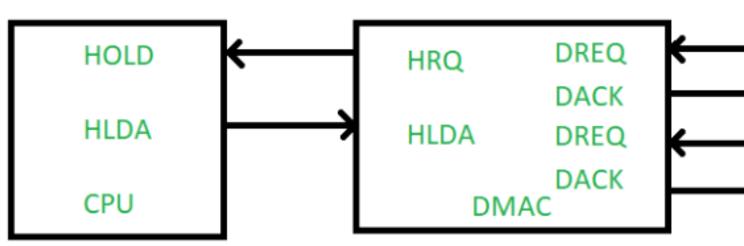

**1. Single Mode** – In this only one channel is used, means only a single DMAC is connected to the bus system.

**2.** Cascade Mode – In this multiple channels are used, we can further cascade more number of DMACs.

### Features of 8257

- ➢Four independent DMA channels

- >Address and Data Bus- Separately available for DMA

- **Burst Mode Transfer** transfer the data blocks quickly

- **Priority Schemes** Assign priorities based on the device preferance

- **>Auto Initialization-** automatically reload the DMA address and count

- register after every transfer.

- **Compatible with diff processor-** with 8085, 8086, z80

# References

https://www.tutorialspoint.com/microprocessor/microprocessor\_8257\_dma\_controller.htm

https://electronicsdesk.com/dma-controller.html

Ramesh S.Gaonkar," Microprocessor – Architecture, Programming and Applications with the 8085", Penram International Publisher,7<sup>th</sup> Ed., 2016

Thank You