### **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

### 19ECB231 – DIGITAL ELECTRONICS

PLD/19ECB202/ LINEAR AND DIGITAL CIRCUITS/Dr.B.Sivasankarii/ASP/ECE/SNSCT

II YEAR/ III SEMESTER

UNIT 5 – SEQUENTIAL CIRCUITS

TOPIC 7 – Introduction to PLD implementation

12/12/2022

### Problem definition

| Device | AND-array    | OR-array     |

|--------|--------------|--------------|

| PROM   | Fixed        | Programmable |

| PLA    | Programmable | Programmable |

| PAL    | Programmable | Fixed        |

| GAL    | Programmable | Fixed        |

- The differences between the first three categories are these:

- -1. In a ROM, the input connection matrix is hardwired. The user can modify the output connection matrix.

- -In a PAL/GAL the output connection matrix is hardwired. The user can modify the input connection matrix.

- -In a PLA the user can modify both the input connection matrix and the output connection matrix.

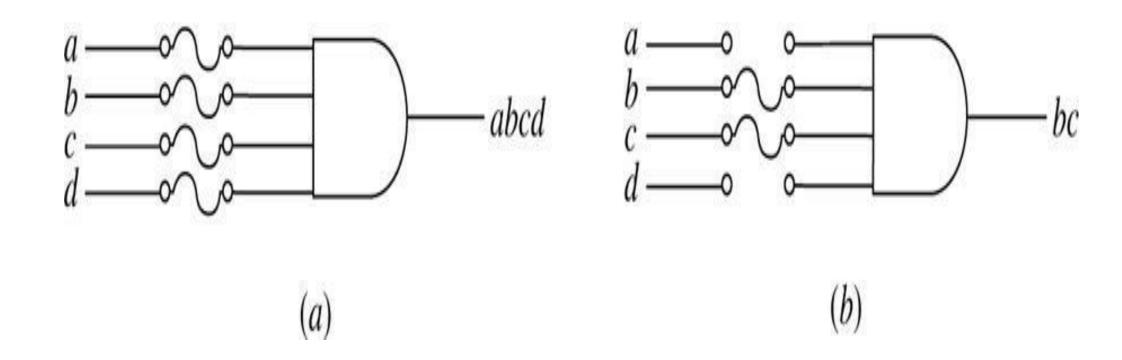

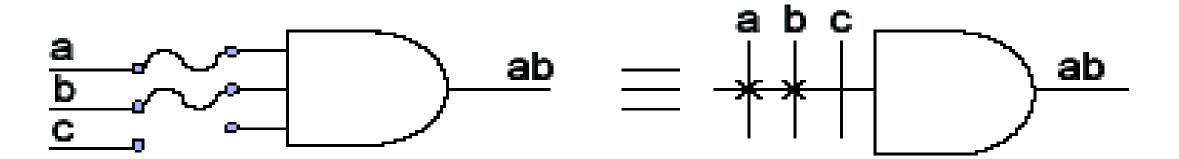

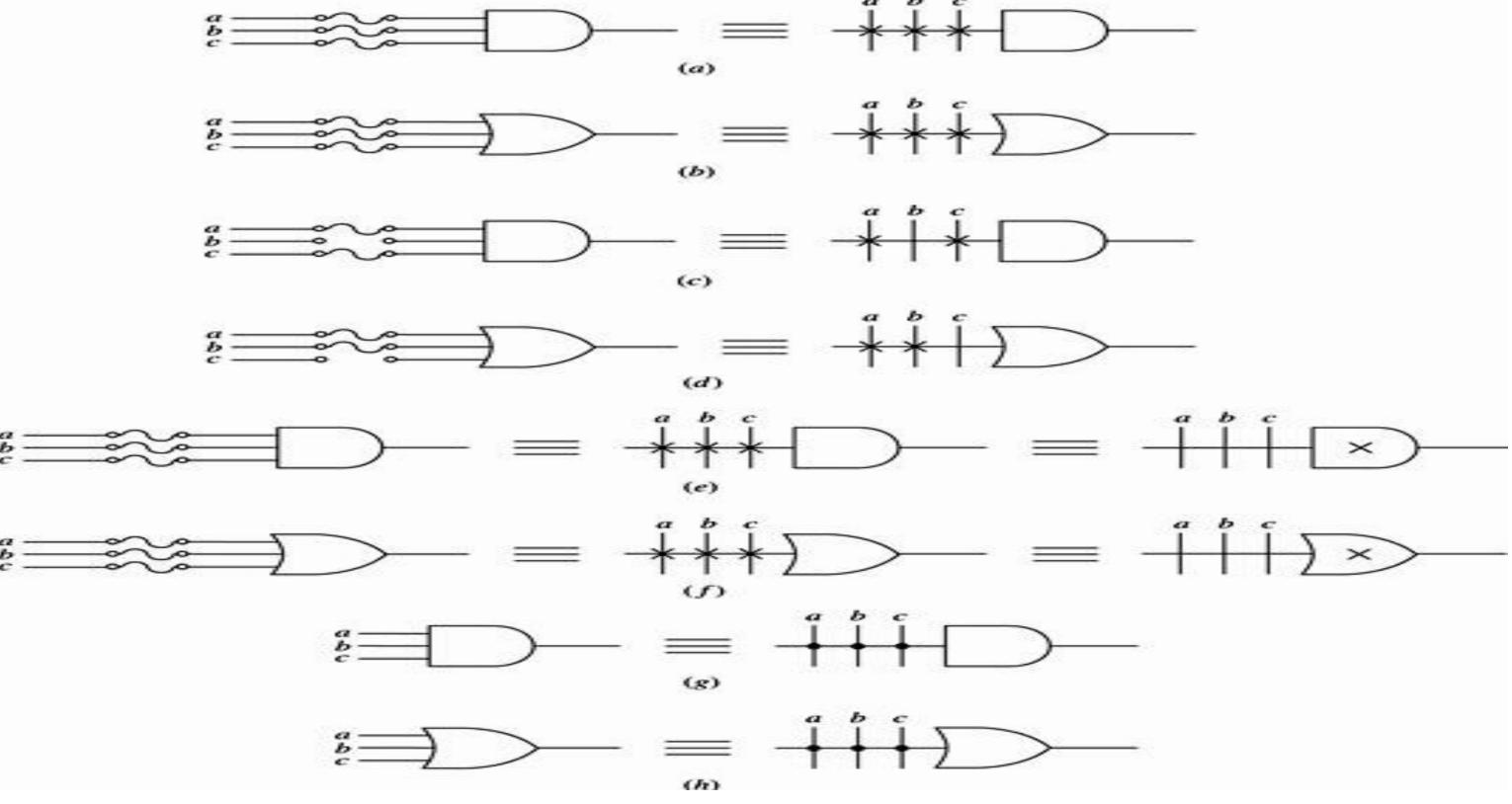

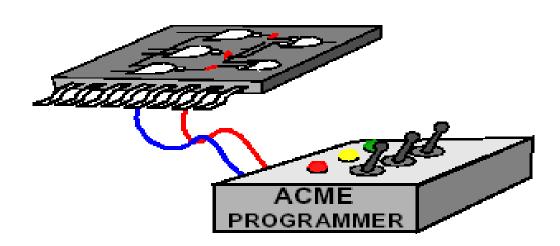

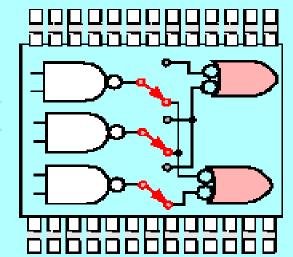

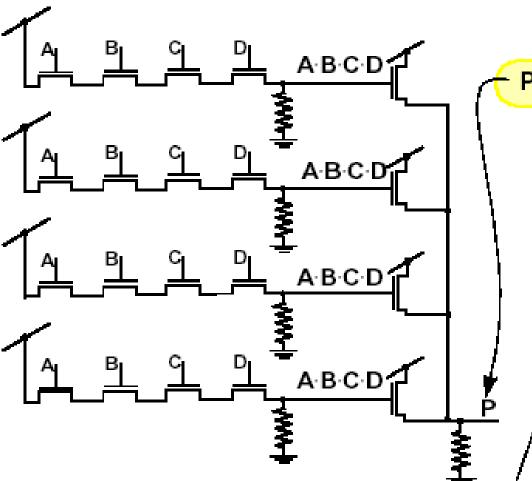

# Programming by blowing fuses.

(a) Before programming.

(b) After programming.

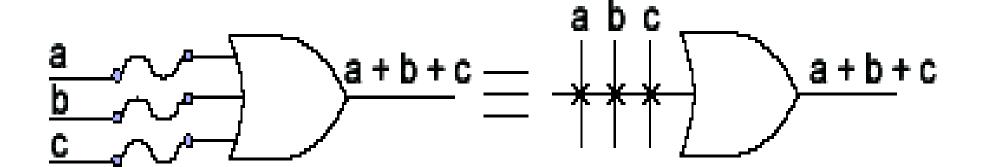

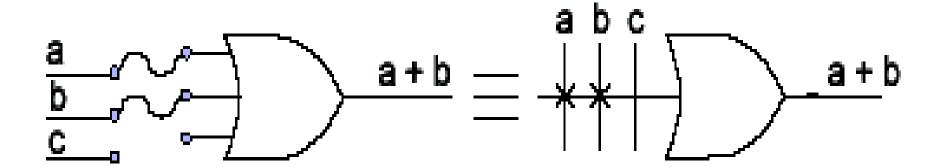

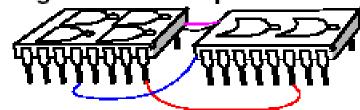

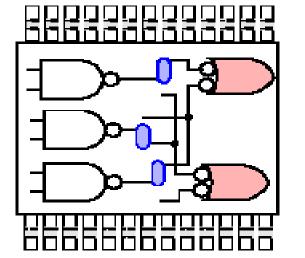

# **OR- PLD Implementation**

# OR gate before programming

OR gate after programming

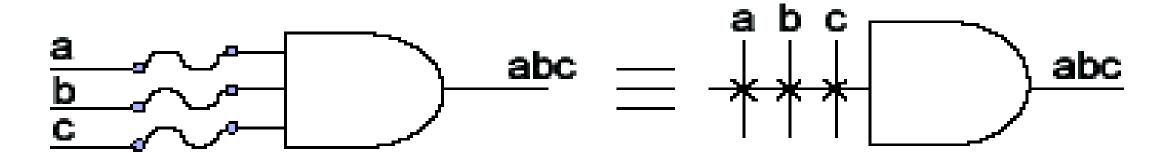

# AND- PLD Implementation

### AND gate before programming

AND gate after programming

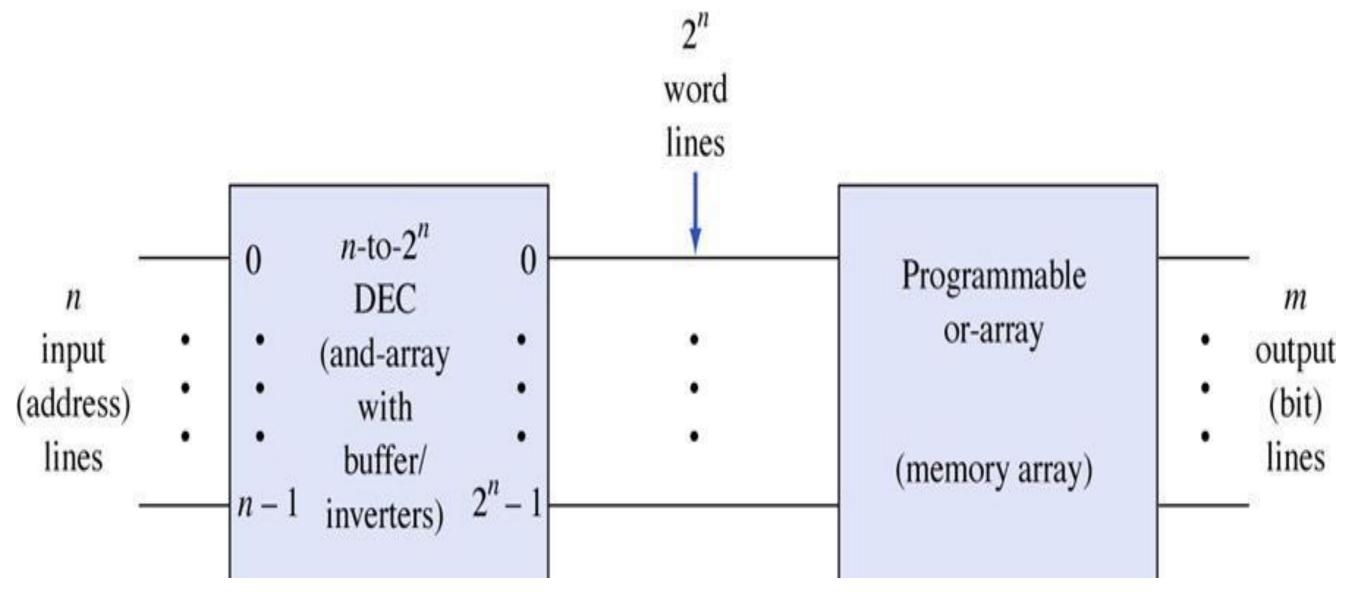

## **PLDs**

## **PROM Notation**

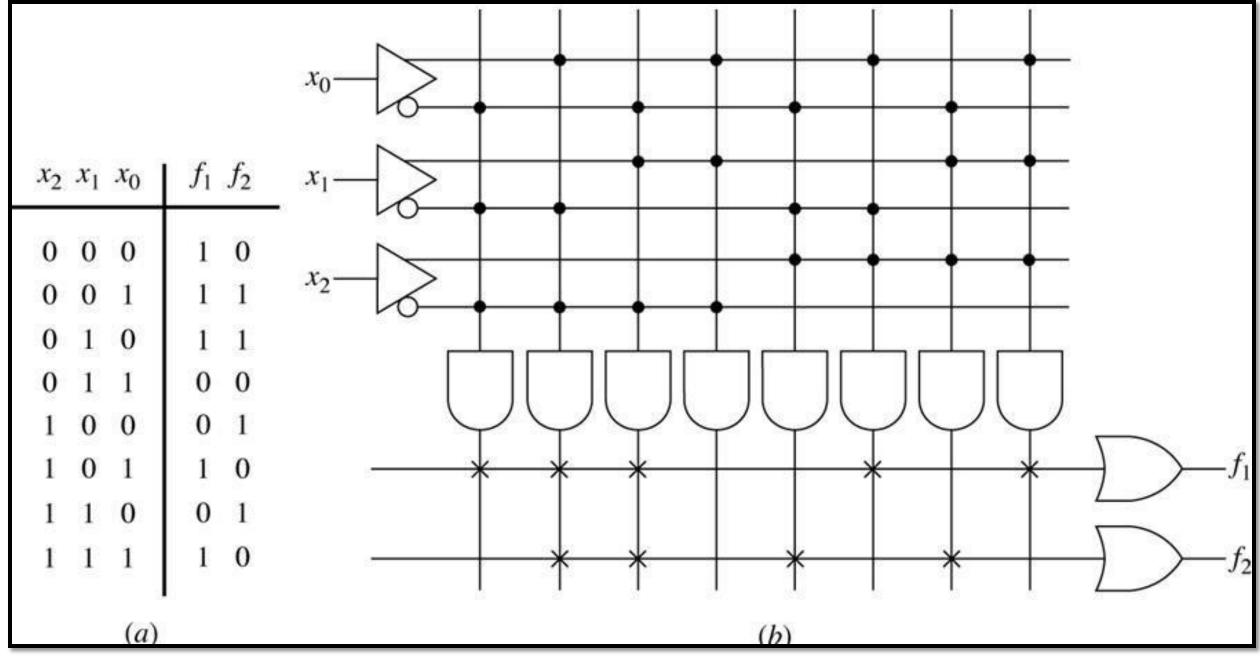

# Using a PROM for logic design

(a) Truth table.

(b) PROM realization.

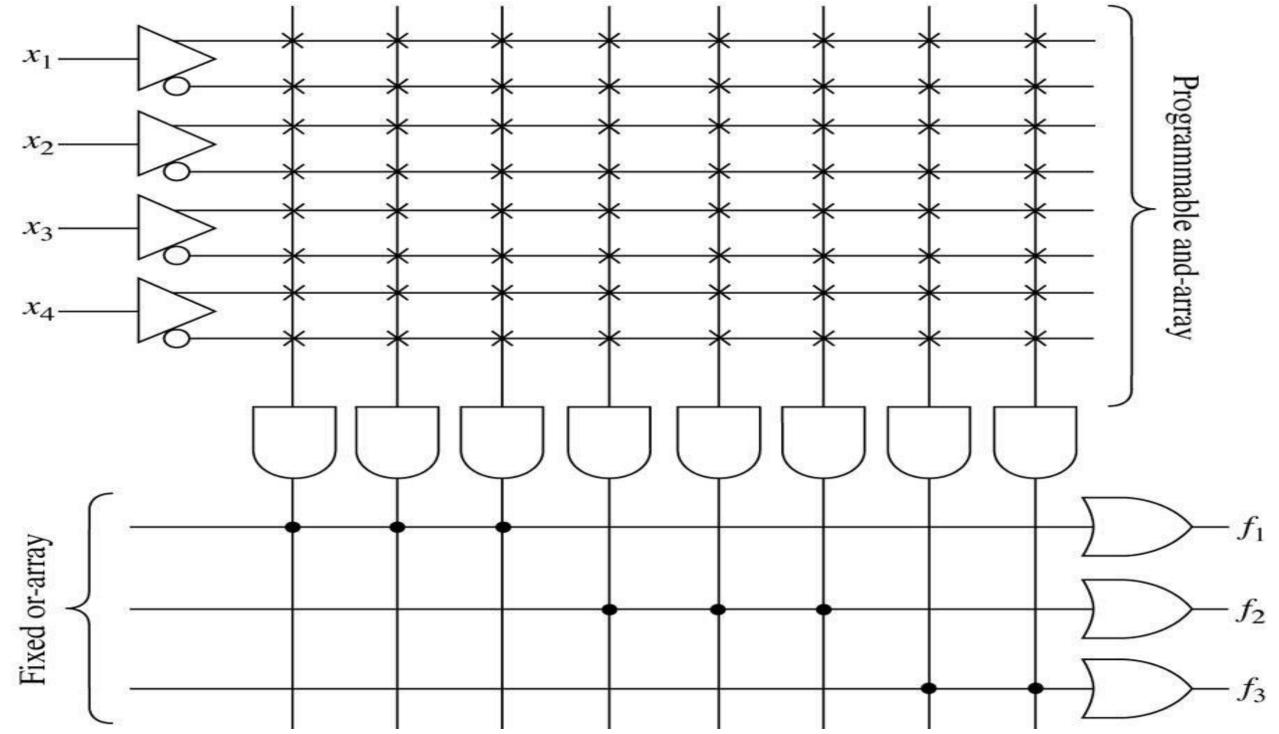

# A simple four-input, three-output PAL device.

# A simple four-input, three-output PAL device.

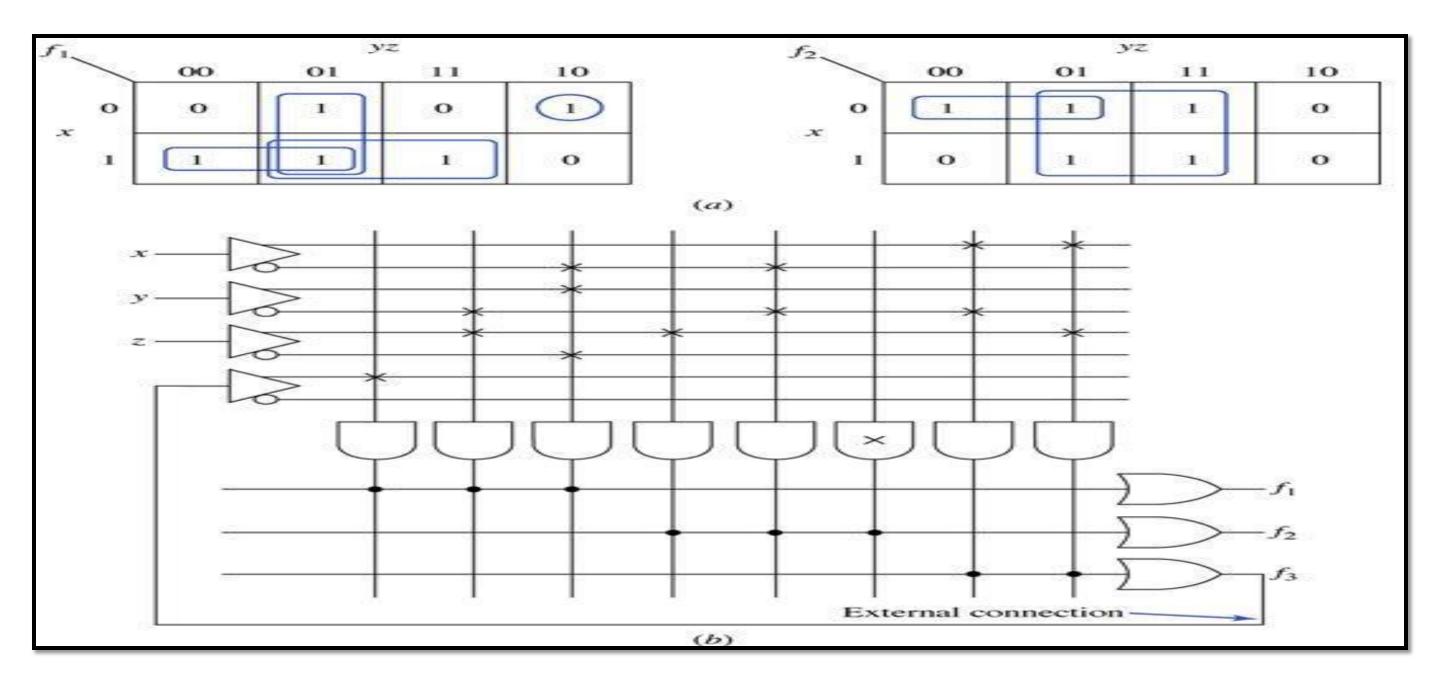

### An example of using a PAL device to realize two Boolean functions.

(a) Karnaugh maps.

(b) Realization.

### **Constructing Digital Circuits**

#### **Hand Wired Circuits**

Cirri 1970-85

- Make 2 to 4 silicon gates in a package.

- Connect with wires.

#### **VLSI** circuits

Start with a silicon wafer and make:

- the gates

- the interconnections on top

both made together.

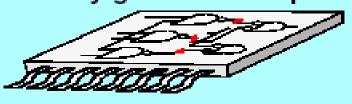

#### Field Programmable circuits

Start with a silicon wafer and make:

- gates with no connections.

- Make connections later using:

- 1) electrical means

- blow fuses, grow anti fuses

- use memory to hold connections

- 2) deposit metal lines on top of silicon.

#### Micro Controllers

### Programmable Logic

#### Different Ways of Connecting Logic

1. Connect Wires Few gates on a chip

2. Electrically Programmable Many gates on a chip

Electrically Controlled Switches

Antifuses; grow to make connections

3. Mask Programmable Many gates on a chip

Metal blobs deposited over ends of wires to be connected

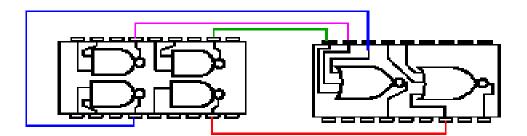

#### Combine the AND and OR logic

$P = A \cdot B \cdot C \cdot D + A \cdot B \cdot C \cdot D + A \cdot B \cdot C \cdot D$

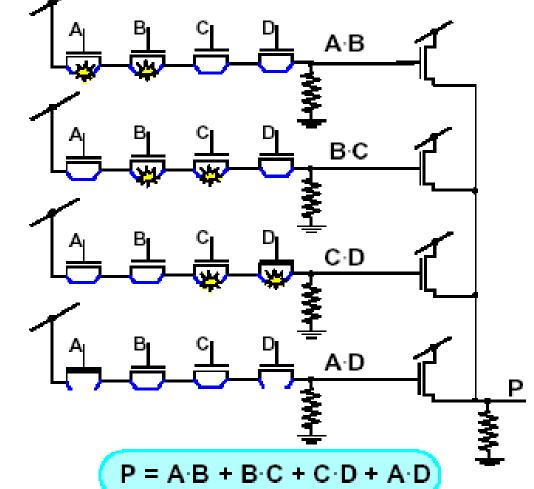

#### A Fuse Programmed Logic Array

Program the logic Short all transistors with fuses. Remove shorts from transistors needed for the AND terms.

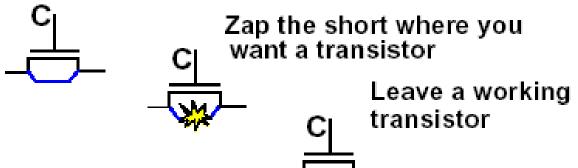

#### Fuse Programming

Start with all transistors shorted.

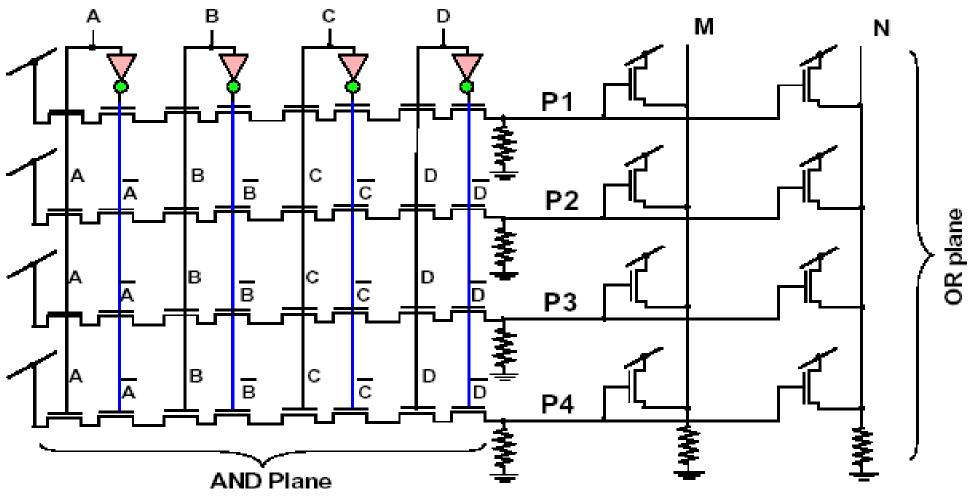

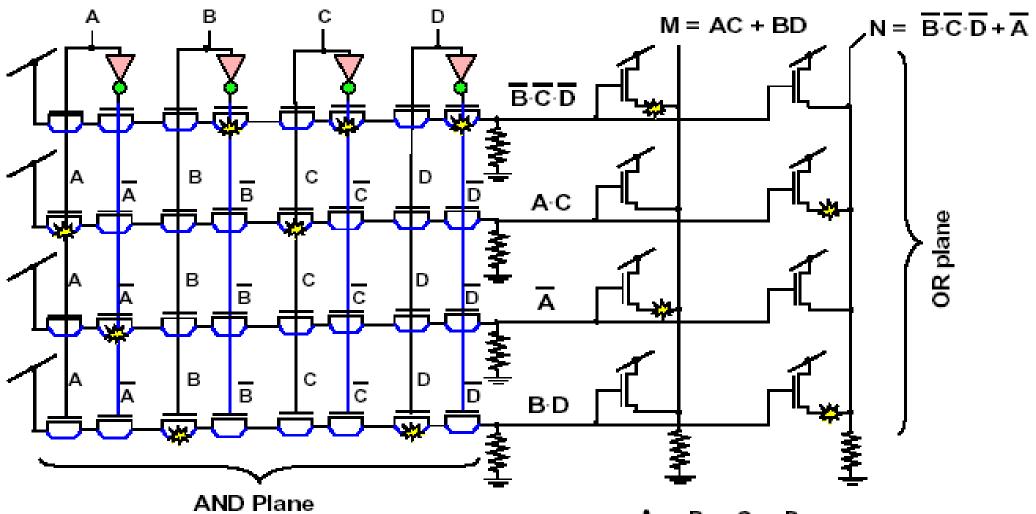

Two outputs M and N Can implement two  $\Sigma$  of  $\Pi$  functions with 4 inputs which includes x and x and with 4 product terms, P1, P2, P3 and P4.

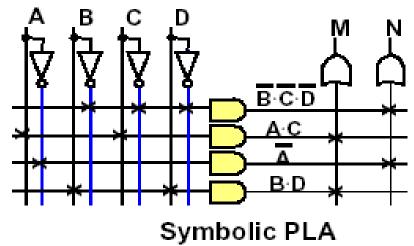

Use the simple symbol for logic design

Symbolic PLA

### Programming the PLA

**AND Plane**

Blow fuses for letters you want in the AND term

OR Plane

Blow fuses to remove unwanted ORs

Symbolic PLA

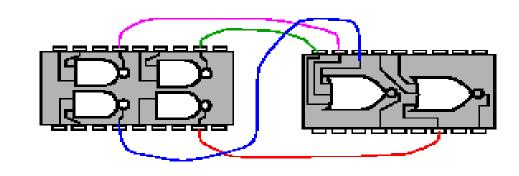

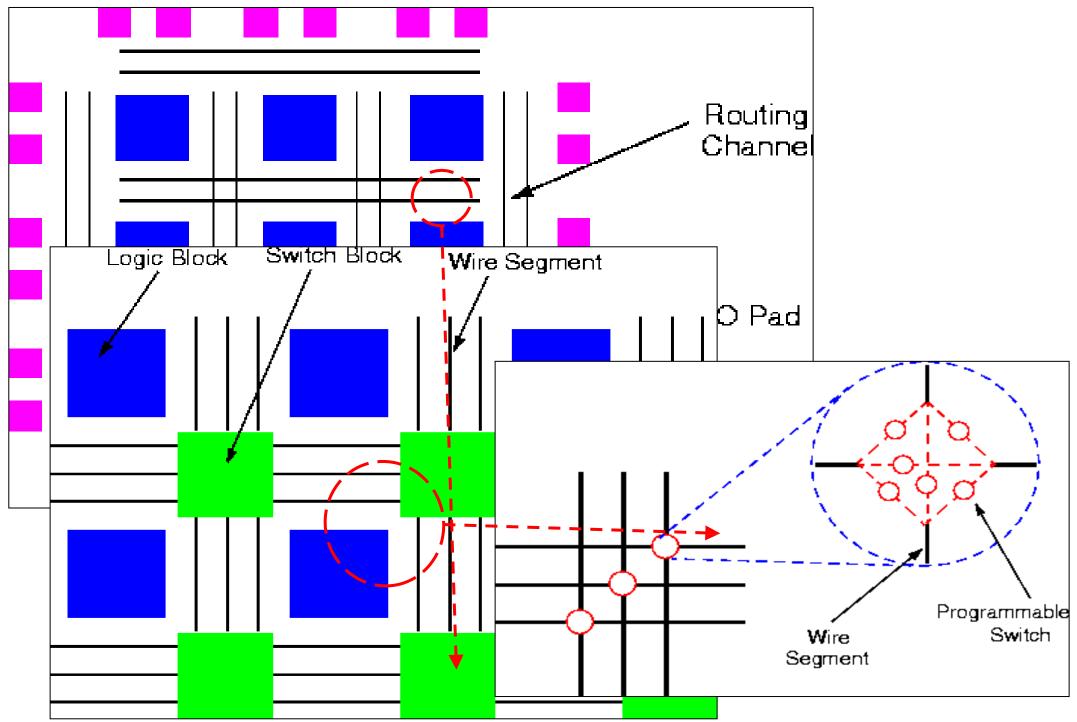

### FPGA AND CPLD

- 1. FPGA Field-Programmable Gate Array.

- 2. CPLD Complex Programmable Logic Device

- 3. FPGA and CPLD is an advance PLD.

- 4. Support thousands of gate where as PLD only support hundreds of gates.

### What is an FPGA?

- Before the advent of programmable logic, custom logic circuits were built at the board level using standard components, or at the gate level in expensive application-specific (custom) integrated circuits.

- FPGA is an integrated circuit that contains many (64 to over 10,000) identical logic cells that can be viewed as standard components. Each logic cell can independently take on any one of a limited set of personalities.

- Individual cells are interconnected by a matrix of wires and programmable switches.

- A user's design is implemented by specifying the simple logic function for each cell and selectively closing the switches in the interconnect matrix.

- Array of logic cells and interconnect form a fabric of basic building blocks for logic circuits. Complex designs are created by combining these basic blocks to create the desired circuit

# What is an FPGA?

# THANK YOU