# **MEALY AND MOORE MODELS**

The most general model of a sequential circuit has inputs, outputs and internal states. It is common to distinguish between two models of sequential circuits:

- Mealy model The output is a function of both the present state and input.

- Moore model The output is a function of the present state only.

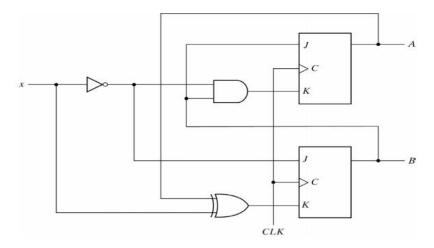

### An example of a Mealy model is:

In a Mealy model, the outputs may change if the inputs change during the clock cycle. To achieve synchronization, the inputs must be synchronized with the clock and the outputs must be sampled only during the clock edge.

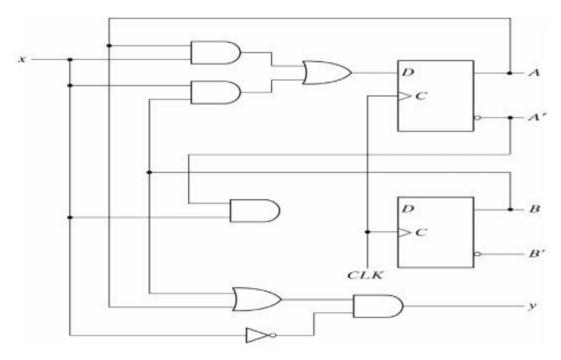

In a Moore model, the outputs of the sequential circuit are synchronized with the clock because they depend on only flip-flop outputs that are synchronized with the clock.

## **STATE REDUCTION & ASSIGNMENT**

Sometimes certain properties of sequential circuits may be used to reduce the number of gates and flip-flops during the design.

The problem of state reduction is to find ways of reducing the number of states in a sequential circuit, while keeping the external input-output relationships unchanged.

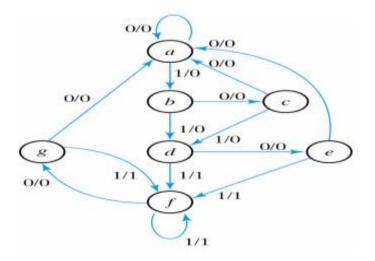

For example, suppose a sequential circuit is specified by the following sevenstate diagram:

There are an infinite number of input sequences that may be applied; each results in a unique output sequence. Consider the input sequence 01010110100 starting from the initial state a:

| state  | а | а | b | С | d | е | f | f | g | f | g | а |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|

| input  | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |   |

| output |   | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | а |

An algorithm for the state reduction quotes that:

"Two states are said to be equivalent if, for each member of the set of inputs, they give exactly the same output and send the circuit either to the same state or to an equivalent state."

|               | Next                              | State        | Output                            |              |  |

|---------------|-----------------------------------|--------------|-----------------------------------|--------------|--|

| Present State | $\boldsymbol{x} = \boldsymbol{0}$ | <i>x</i> = 1 | $\boldsymbol{x} = \boldsymbol{0}$ | <i>x</i> = 1 |  |

| а             | а                                 | b            | 0                                 | 0            |  |

| b             | с                                 | d            | 0                                 | 0            |  |

| с             | a                                 | d            | 0                                 | 0            |  |

| d             | e                                 | f            | 0                                 | 1            |  |

| е             | a                                 | f            | 0                                 | 1            |  |

| f             | g                                 | f            | 0                                 | 1            |  |

| g             | a                                 | f            | 0                                 | 1            |  |

Now apply this algorithm to the state table of the circuit:

States g and e both go to states a and f and have outputs of 0 and 1 for x = 0 and x = 1, respectively.

|               | Next         | State        | Output              |              |  |  |

|---------------|--------------|--------------|---------------------|--------------|--|--|

| Present State | x = <b>0</b> | <i>x</i> = 1 | <i>x</i> = <b>0</b> | <i>x</i> = 1 |  |  |

| а             | а            | b            | 0                   | 0            |  |  |

| b             | с            | d            | 0                   | 0            |  |  |

| с             | а            | d            | 0                   | 0            |  |  |

| d             | е            | f            | 0                   | 1            |  |  |

| е             | а            | f            | 0                   | 1            |  |  |

| f             | e            | f            | 0                   | 1            |  |  |

The procedure for removing a state and replacing it by its equivalent is demonstrated in the following table:

Thus, the row with present state g is removed and stage g is replaced by state e each time it occurs in the next state columns. Present state f now has next states e and f and outputs 0 and 1 for x = 0 and x = 1. The same next states and outputs appear in the row with present state d. Therefore, states f and d are equivalent and can be removed and replaced with d.

| Inc mai i cut                                                                                                   | iccu state ti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| the second se | and the second se |  |

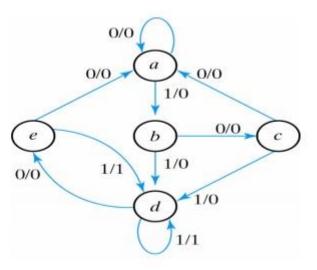

The final reduced state table is

|               | Next                | State        | Output              |                          |  |

|---------------|---------------------|--------------|---------------------|--------------------------|--|

| Present State | <b>x</b> = <b>0</b> | <i>x</i> = 1 | <i>x</i> = <b>0</b> | <b>x</b> = <b>1</b><br>0 |  |

| a             | а                   | b            | 0                   |                          |  |

| b             | С                   | d            | 0                   | 0                        |  |

| С             | a                   | d            | 0                   | 0                        |  |

| d             | е                   | d            | 0                   | 1                        |  |

| е             | a                   | d            | 0                   | 1                        |  |

The state diagram for the above reduced table is:

This state diagram satisfies the original input output specifications.

#### Applying the input sequence previously used, the following list is obtained:

| state  | a | a | b | с | d | е | d | d | е | d | е | а |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|

| input  | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |   |

| output | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |   |

Note that the same output sequence results, although the state sequence is different.

### An example of a Moore model is: