## SNS COLLEGE OF TECHNOLOGY Coimbatore-35 <u>An Autonomous Institution</u>

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

### **DEPARTMENT OF COMPUTER SCIENCE ENGINEERING**

### **19ECB231** – DIGITAL ELECTRONICS

II YEAR/ III SEMESTER

## **UNIT 4 – DESIGN OF SEQUENTIAL CIRCUITS**

**TOPIC – STATE MINIMIZATION & ASSIGNMENT**

25-Dec-23

# State Reduction and Assignmer

• The analysis of sequential circuits starts from a circuit diagram and culminates in a state table or diagram.

• The design of a sequential circuit starts from a set of specifications and culminates discusses certain properties of sequential circuits that may be used to reduce the number of gates and flip-flops during the design.

# State Reduction

- The reduction of the number of flip-flops in a sequential circuit is referred to as the state-reduction problem. State-reduction algorithms are concerned with procedures for reducing the number of states in a state table, while keeping the external input-output requirements unchanged.

- Since m flip-flops produce 2<sup>m</sup> states, a reduction in the number of states may result in a reduction in the number of flip-flops. An unpredictable effect in reducing the number of flip-flops is that sometimes the equivalent circuit may require more combinational gates.

25-Dec-23

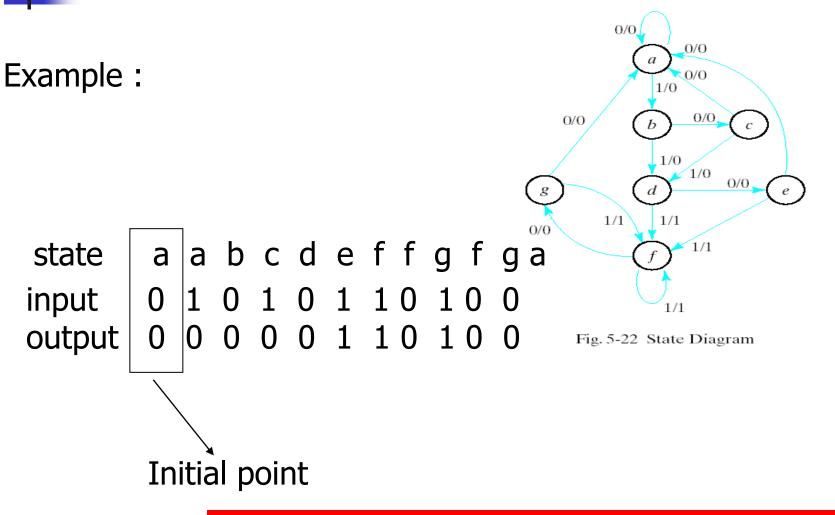

We now proceed to reduce the number of states for this example. First, we need the state table; it is more convenient to apply procedures for state reduction using a table rather than a diagram. The state table of the circuit is listed in Table 5-6 and is obtained directly from the state diagram.

|               | Next                | State        | Out          | put   |

|---------------|---------------------|--------------|--------------|-------|

| Present State | <i>x</i> = <b>0</b> | <i>x</i> = 1 | <i>x</i> = 0 | x = 1 |

| a             | a                   | Ь            | 0            | 0     |

| b             | с                   | d            | 0            | 0     |

| c             | а                   | d            | 0            | 0     |

| d             | е                   | f            | 0            | 1     |

| e             | а                   | f            | 0            | 1     |

| f             | g                   | f            | 0            | 1     |

| g             | a                   | f            | 0            | 1     |

States g and e are two such states: they both go to states a and f and have outputs of 0 and 1 for x=0 and x=1, respectively. Therefore, states g and e are equivalent and one of these states can be removed. The procedure of removing a state and replacing it by its equivalent is demonstrated in Table 5-7. The row

with present g is removed and state g is replaced by state e each time it occurs in the next-state columns.

|               | Next         | State        | Out                 | put   |

|---------------|--------------|--------------|---------------------|-------|

| Present State | <i>x</i> = 0 | <i>x</i> = 1 | <i>x</i> = <b>0</b> | x = 1 |

| а             | а            | b            | 0                   | 0     |

| b             | с            | d            | 0                   | 0     |

| С             | а            | d            | 0                   | 0     |

| d             | е            | f            | 0                   | 1     |

| e             | a            | f            | 0                   | 1     |

| f             | (e)          | f            | 0                   | 1     |

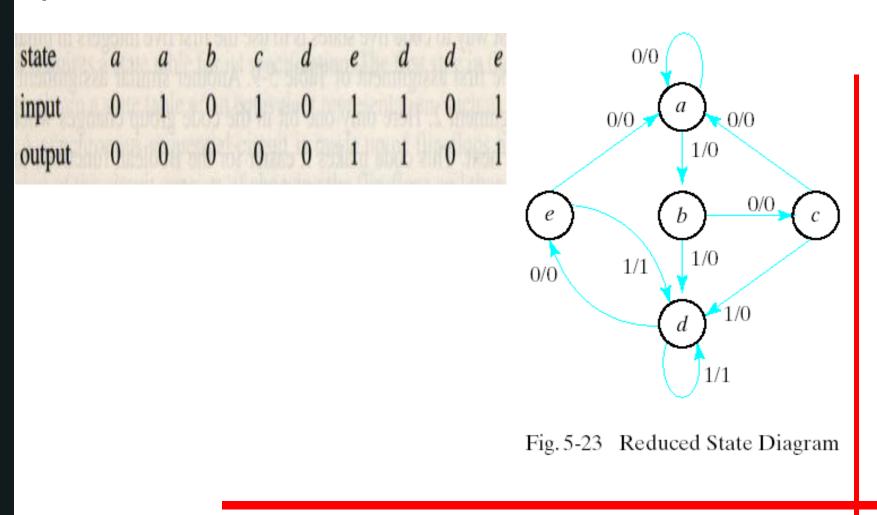

Present state f now has next states e and f and outputs 0 and 1 for x=0 and x=1, respectively. The same next states and outputs appear in the row with present state d. Therefore, states f and d are equivalent and state f can be removed and replaced by d. The final reduced table is shown in Table 5-8. The state diagram for the reduced table consists of only five Table 5-8

states and is shown in Fig. 5-23.

|                    | Next                | State        | Out          | put          |

|--------------------|---------------------|--------------|--------------|--------------|

| Present State      | <i>x</i> = <b>0</b> | <i>x</i> = 1 | <i>x</i> = 0 | <i>x</i> = 1 |

| a                  | а                   | Ь            | 0            | 0            |

| Ь                  | с                   | d            | 0            | 0            |

| nonce coo legizida | a                   | d            | 0            | 0            |

| d d d d            | e                   | d            | 0            | 1            |

| e                  | а                   | d            | 0            | 1            |

## **State Assignment**

#### Table 5-9

Three Possible Binary State Assignments

| State | Assignment 1<br>Binary | Assignment 2<br>Gray code | Assignment 3<br>One-hot |

|-------|------------------------|---------------------------|-------------------------|

| a     | 000                    | 000                       | 00001                   |

| b     | 001                    | 001                       | 00010                   |

| с     | 010                    | 011                       | 00100                   |

| d     | 011                    | 010                       | 01000                   |

| е     | 100                    | 110                       | 10000                   |

#### Table 5-10

**Reduced State Table with Binary Assignment 1**

|               | Next         | State        | Out                 | put |

|---------------|--------------|--------------|---------------------|-----|

| Present State | <i>x</i> = 0 | <i>x</i> = 1 | <i>x</i> = <b>0</b> |     |

| 000           | 000          | 001          | <br>0               | 0   |

| 001           | 010          | 011          | 0                   | 0   |

| 010           | 000          | 011          | 0                   | 0   |

| 011           | 100          | 011          | 0                   | 1   |

| 100           | 000          | 011          | 0                   | 1   |

25-Dec-23

The procedure for designing synchronous sequential circuits can be summarized by a list of recommended steps.

- 1. From the word description and specifications of the desired operation, derive a state diagram for the circuit.

- 2. Reduce the number of states if necessary.

- 3. Assign binary values to the states.

- 4. Obtain the binary-coded state table.

- 5. Choose the type of flip-flops to be used.

- 6. Derive the simplified flip-flop input equations and output equations.

- 7. Draw the logic diagram.

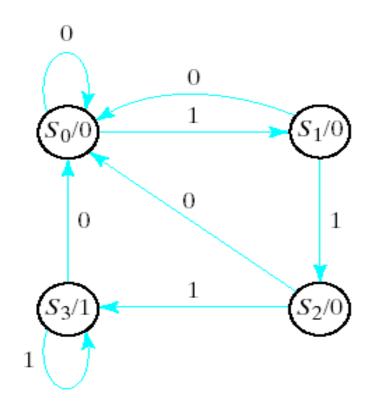

Fig. 5-24 State Diagram for Sequence Detector

25-Dec-23

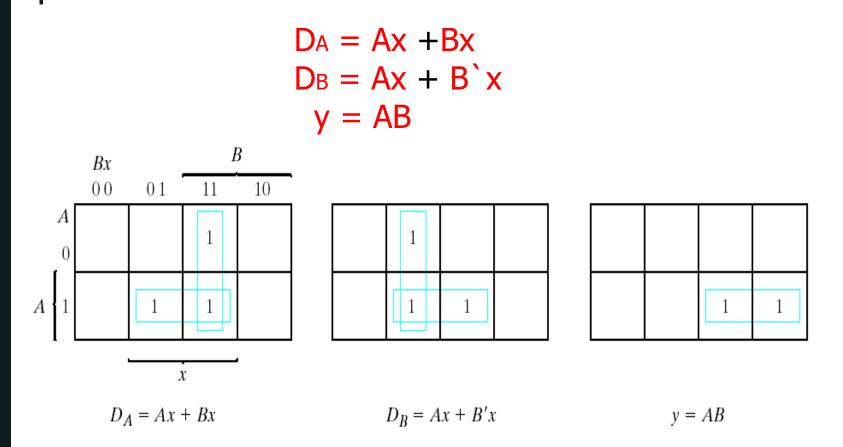

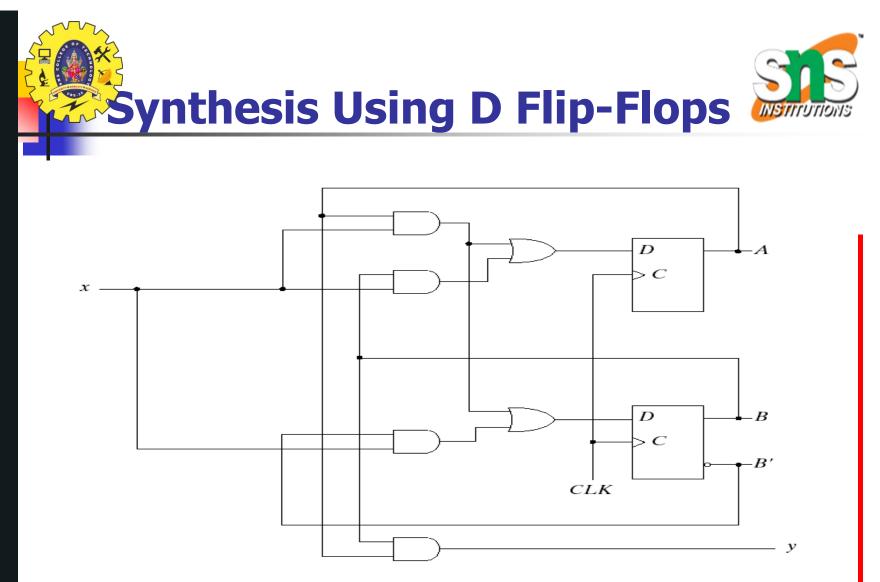

# Synthesis Using D Flip-Flops

| $A(t + 1) = D_A(A, B, x) = \Sigma (3, 5, 7)$ |  |

|----------------------------------------------|--|

| $B(t + 1) = D_B(A, B, x) = \Sigma (1, 5, 7)$ |  |

| $y(A, B, x) = \sum (6, 7)$                   |  |

| Table | 5-11  |         |       |          |

|-------|-------|---------|-------|----------|

| State | Table | for Sec | uence | Detector |

| Pres<br>Stat | ent     | Input           | Ne<br>Sta |   | Output          |

|--------------|---------|-----------------|-----------|---|-----------------|

| A            | В       | ×               | A         | B | y               |

| 0            | 0       | 0               | 0         | 0 | 0               |

| 0            | 0       | 1               | 0         | 1 | 0               |

| 0            | 1.1     | 0               | 0         | 0 | 0               |

| 0            | 1       | 1               | 1         | 0 | 0               |

| 1            | 0       | 0               | 0         | 0 | 0               |

| 1            | 0       | a tran 1 the fi | 1.0       | 1 | 0               |

| 1            | 1 1 1 m | 0               | 0         | 0 | te citta 1 in a |

| 1            | 1       | 1               | 1         | 1 | 1               |

# Synthesis Using D Flip-Flops

Fig. 5-26 Logic Diagram of Sequence Detector

25-Dec-23

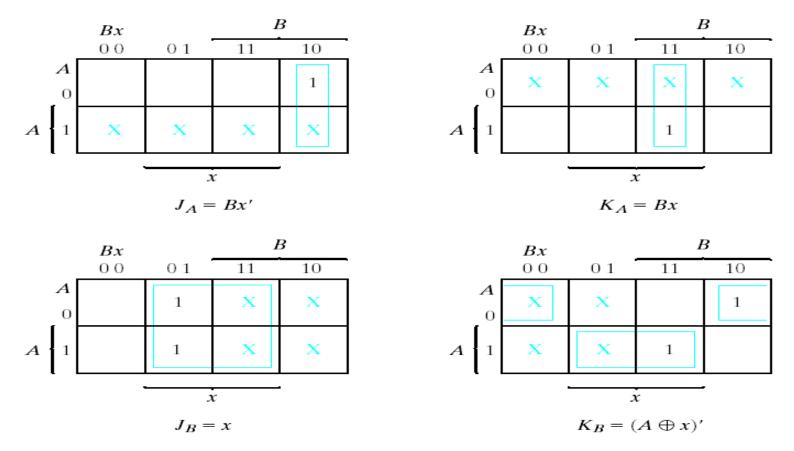

Table 5-13

Table 5-12

Flip-Flop Excitation Tables

| Q(t) | Q(t + 1) | J | K |

|------|----------|---|---|

| 0    | 0        | 0 | X |

| 0    | 1 8      | 1 | X |

| 1    | 0        | X | 1 |

| 1    | 1        | X | 0 |

Ref. Table 5-1

State Table and JK Flip-Flop Inputs Next Present **Flip-Flop Inputs** State Input State В JA KA  $J_B K_B$ B A X 0 X 0 X 0 0 0 0 X X 0 X X 1 0 0 X X 0 0 X 0 X 0 0 Х 0 X en fram des fi-ch 0 X 0 X 0 0 1 X Х

tice Hall, Inc.

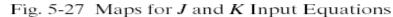

25-Dec-23

Fig. 5-28 Logic Diagram for Sequential Circuit with JK Flip-Flops

# Synthesis Using T Flip-Flops

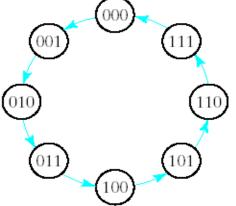

The synthesis using T flip-flops will be demonstrated by designing a binary counter. An n-bit binary counter consists of n flip-flops that can count in binary from 0 to 2<sup>n</sup>-1. The state diagram of a 3-bit counter is shown in Fig. 5-29.

$$\begin{array}{c|c} Q(t) & Q(t+1) & T \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ \hline (b)T \end{array}$$

Fig. 5-29 State Diagram of 3-Bit Binary Counter

# Synthesis Using T Flip-Flops

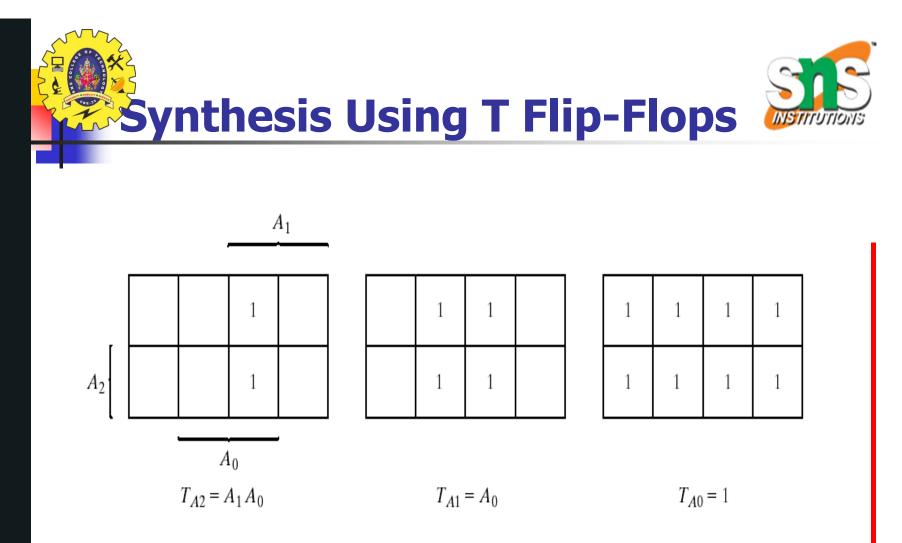

#### **Table 5-14** State Table for 3-Bit Counter **Flip-Flop Inputs Next State Present State** TAZ TA1 TAO Ao Ao Az A A 0 0 0 0 0 0 0 0 0 1 0 0 0 0 n 0 0

25-Dec-23

Fig. 5-30 Maps for 3-Bit Binary Counter

25-Dec-23

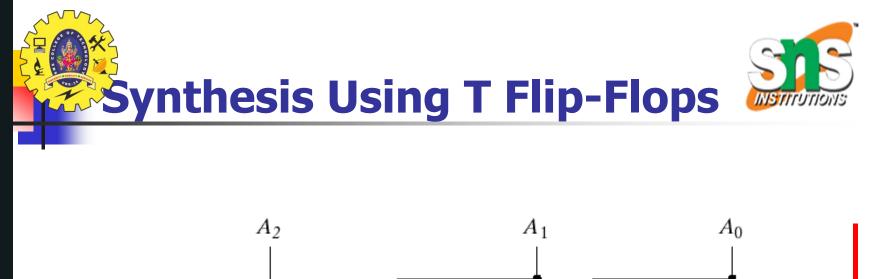

Fig. 5-31 Logic Diagram of 3-Bit Binary Counter

25-Dec-23

### **THANK YOU**

25-Dec-23