### SNS COLLEGE OF TECHNOLOGY

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

### 19ECB231 - DIGITAL ELECTRONICS

MOORE -MEALY/19ECB231/ DIGITAL ELECTRONICS/E.RAMYA/AP/ECE/SNSCT

II YEAR/ III SEMESTER

UNIT 4 -DESIGN OF SEQUENTIAL CIRCUITS

TOPIC -Classification of sequential circuits: Moore and Mealy example

### **Analysis Procedure**

- •Identify type of circuit either Mealy or Moore circuit

- •Derive excitation equation (Boolean expression)

- •Derive next state and output equations

- •Generate state table

- •Generate state diagram

### **Analysis Procedure**

### DESIGN PROCEDURE FOR CLOCKED SEQUENTIAL CIRCUIT

The following steps are followed to design the clocked sequential logic circuit.

- •Obtain the state table from the given circuit information such as a state diagram, a timing diagram or description.

- •The number of states may be reduced by state reduction technique.

- •Assign binary values to each state in the state table.

- •Determine the number of flip flops required and assign a letter symbol to each flip flop.

- •Choose the flip flop type to be used according to the application.

- •Derive the excitation table from the reduced state table.

- •Derive the expression for flip flop inputs and outputs using k-map simplification (The present state and inputs are considered for k-map simplification) and draw logic circuit

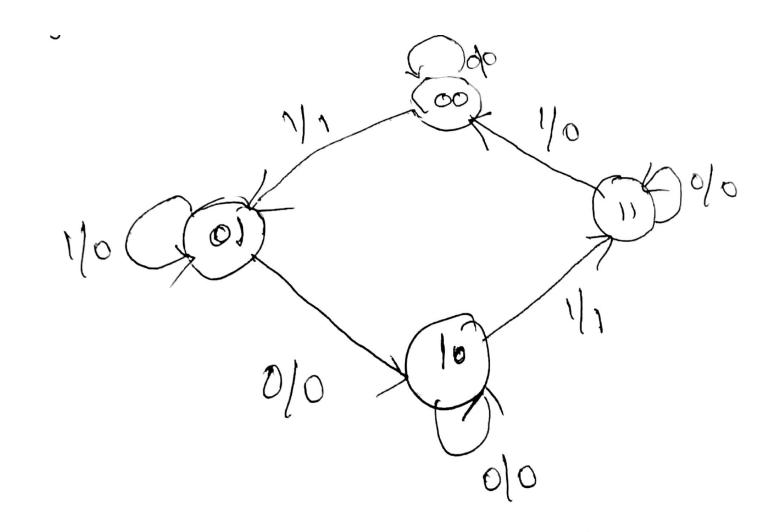

Design the synchronous sequential circuit for mealy diagram using D flip flop

#### **Solution**

#### **Step 1: State Table**

Table 6.15: State Table

|               |       | 6.15. 300     | Out   | put |

|---------------|-------|---------------|-------|-----|

| Present State | Next  | State $x = 1$ | x = 0 | x=1 |

| Present State | x = 0 | A = B         | Y     | y   |

| 4 B           | A $B$ | $\frac{A}{2}$ | Ø     | 1   |

| $\frac{A}{0}$ | 0 0   |               | 0     | 0   |

| 0 0           | 1 0   | 0 1           | o     | 1   |

| 1 0 1         | 1 0   | 1 1           | 0     | o   |

|               | 1 1   | 0 0           |       |     |

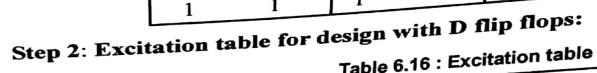

Table 6.16 : Excitation table for D flip flop

| Table 0.10    | Input      |       |

|---------------|------------|-------|

| 4 State       | Next State | Input |

| Present State |            | D     |

| Q(t)          | Q(t+1)     | 0     |

| 20,           | 0          | 0     |

| 1 0           |            | 1     |

| 1 0 1         | 1          |       |

|               | 0          | 0     |

| ] 1 ]         | Ŭ          | 1. 1  |

| 1 1           | 1          | 1     |

| 1 1           |            |       |

Table 6.17: Excitation table for design with D flip flops

| Persont State   Input   Next State   Flip Flop Inputs |          |       |        |        |        | Output    |        |

|-------------------------------------------------------|----------|-------|--------|--------|--------|-----------|--------|

| Presei                                                | nt State | Input | Next S | State  | Flip F | op inputs | Guepus |

| A                                                     | В        | x     | A(t+1) | B(t+1) | DA     | DB        | Y      |

|                                                       | 0        | 0     | 0      | 0      | 0      | 0         | О      |

| 0                                                     | 0        | 1     | o      | 1      | 0      | 1         | 1      |

| lő                                                    | 1        | 0     | 1      | 0      | 1      | 0         | 0      |

| 0                                                     | 1        | 1     | 0      | 1      | 0      | 1         | 0      |

| 1                                                     | 0        | 0     | 1      | 0      | 1      | 0         | 0      |

| 1                                                     | 0        | 1     | 1      | 1      | 1      | 1         | 1      |

| 1                                                     | 1        | 0     | 1      | 1      | 1      | 1 .       | 0      |

| 1                                                     | 1        | 1     | 0      | 0      | 0      | 0         | 0      |

|                                                       | <b>D</b> | 04.11 |        |        |        |           |        |

$$D=Q(t+1)$$

Therefore,

$$DA = A(t+1)$$

$$DB = B(t+1)$$

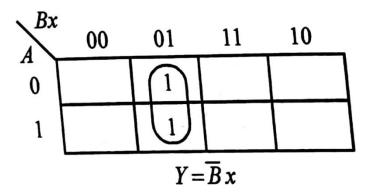

3: K map simplification for flip flop input functions and circuit output function step 3: K pression for DA

### Expression for DB

### Expression for y

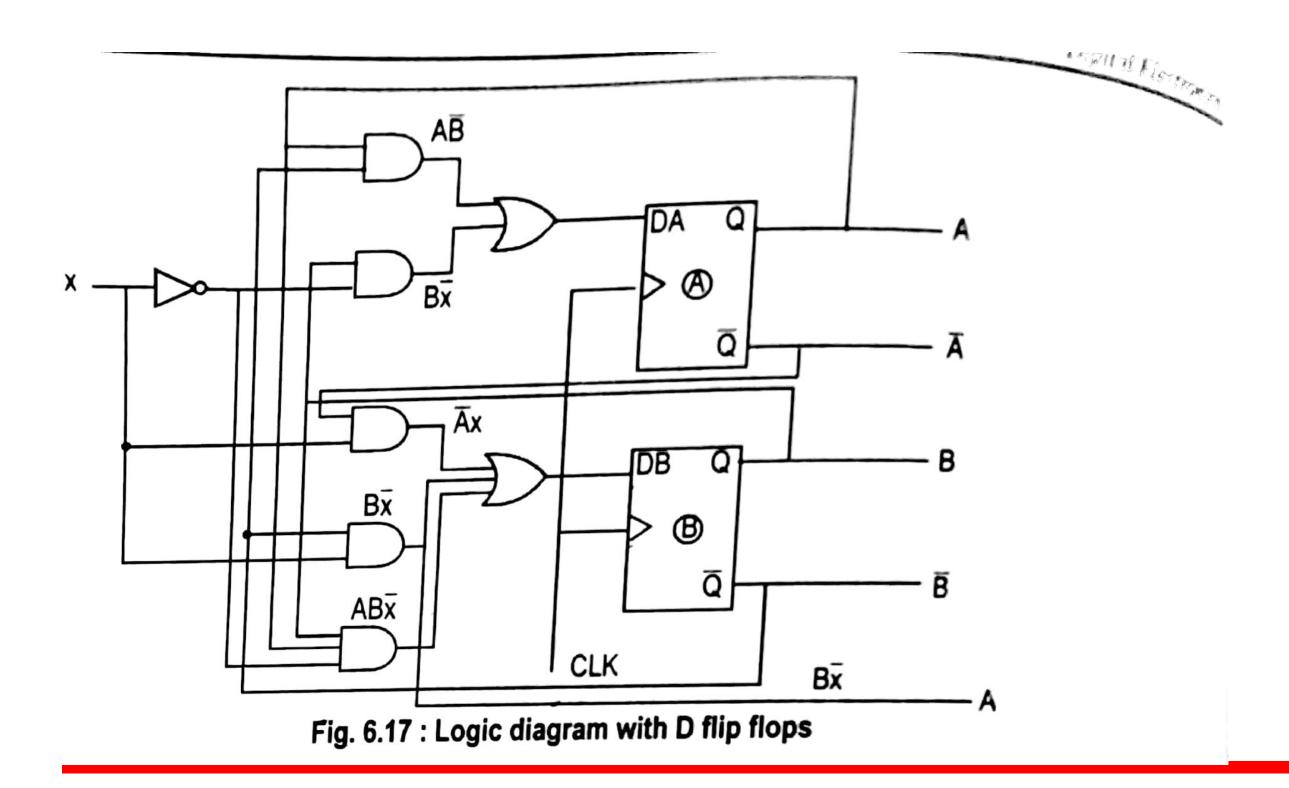

#### Step 4: Logic Diagram

The simplified functions are:

$$DA = A\overline{B} + B\overline{x}$$

$$DB = \overline{A}x + B\overline{x} + AB\overline{x}$$

$$Y = \overline{B}x$$

### **Moore Machine**

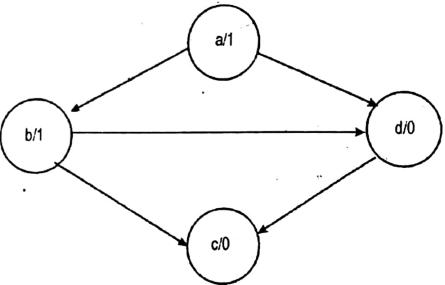

Design the synchronous sequential circuit for the Moore state diagram of Figure 6.18 using

T flip flops.

Fig. 6.18 : Moore state diagram

#### Solution

Step 1: State Table: The state table for the given Moore state diagram is shown in Table 6.18.

**Table 6.18: State Table**

| Present State | Next State | Output |

|---------------|------------|--------|

| а             | b          | 1      |

| b             | С          | 1      |

| С             | d          | 0      |

| d             | a          | 0      |

### 2: Binary Assignment

Assign the binary values 00, 01, 11, 10 to the states a, b, c, d respectively. Table 6.19 shows the state table with binary assignment.

Table 6.19: State Table with Binary assignment

| Table 6.19 : State Table With 5 |   |            |        |        |   |  |

|---------------------------------|---|------------|--------|--------|---|--|

| Present State                   |   | Next State |        | Output |   |  |

| A                               | В | A(t+1)     | B(t+1) | Y      |   |  |

| 0                               | 0 | 0          | 1      | 1      | ٠ |  |

| 0                               | 1 | 1          | 1      | 1      |   |  |

| 1                               | 1 | 1          | 0      | 0      | 1 |  |

| 1                               | 0 | 0          | 0      | 0      |   |  |

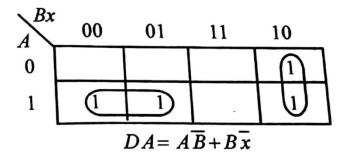

### Step 3: Excitation table for design with T flip flops.

Table 6.20 shows the excitation table for T flip flop and Table 6.21 shows the excitation table for given problem.

Table 6.20: Excitation table for T flip flop

| Table 0.20 . Excitation table for the |      |        |     |  |  |

|---------------------------------------|------|--------|-----|--|--|

|                                       | Q(T) | Q(t+1) | T   |  |  |

| 1                                     | 0    | 0      | 0   |  |  |

| 1                                     | 0    | 1      | 1 1 |  |  |

| 1                                     | 1    | 0      | 1   |  |  |

|                                       | 1    | 1      | 0   |  |  |

Table 6.21: Excitation Table

| Table  |      | : Excitation Table |  |

|--------|------|--------------------|--|

| I ZDIO | 6.21 | ' Evcitation Table |  |

| Presen   | t state | Next State |        | Inp | Output |   |

|----------|---------|------------|--------|-----|--------|---|

| <u>A</u> | В       | A(t+1)     | B(t+1) | TA  | TB     | Y |

| 0        | 0       | 0          | 1      | 0   | 1      | 1 |

| 0        | 1       | 1          | 1      | 1   | 0      | 1 |

| 1        | 1       | 1          | 0      | 0   | 1      | 0 |

| 1        | 0       | 0          | 0      | 1   | 0      | 0 |

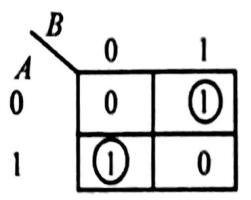

Step 4: K-map simplification for flip flop input functions (TA, TB) and output function (Y).

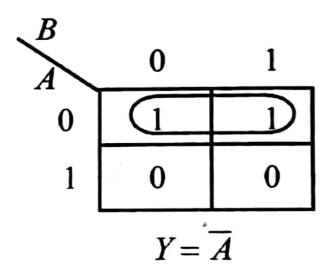

### Expression for TA

$$TA = \overline{A}B + A\overline{B} = A \oplus B$$

### Expression for TB

$$\begin{array}{c|c}

B \\

\hline

A \\

0 \\

\hline

0 \\

\hline

0 \\

\hline

0

\end{array}$$

$$TB = \overline{AB} + AB = \overline{A \oplus B}$$

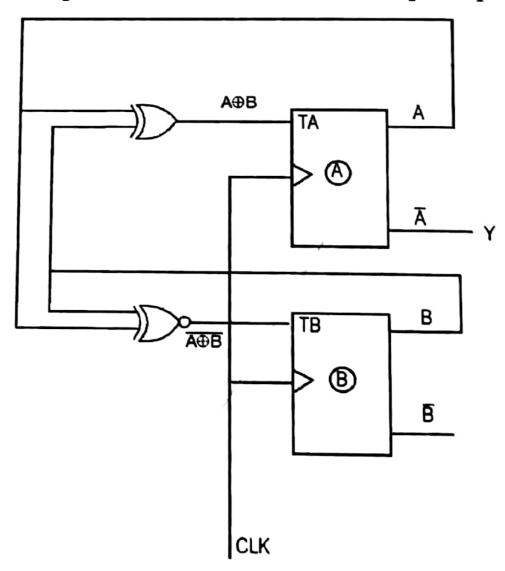

Step 5: Logic diagram of Moore sequential circuit with T flip flops.

Fig. 6.19: Moore sequential circuit with T flip flops

**Input-based or Mealy-type sequential circuit.** The output values are dependent on the input values as well as its present state.

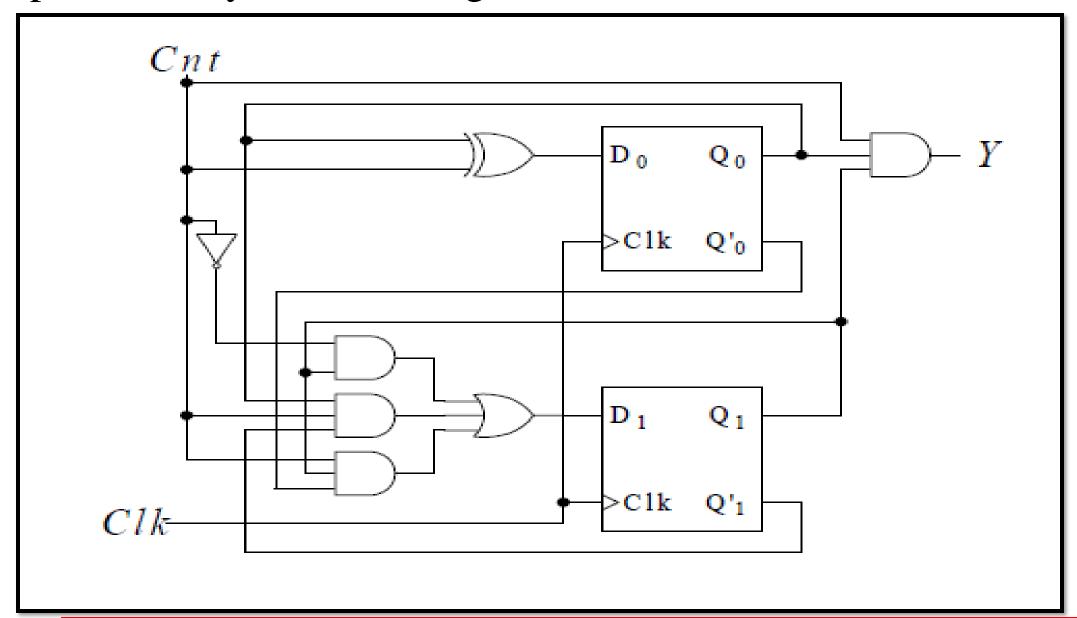

Derive the next state, the output tables, and the state diagram for the (modulo-4 counter) sequential circuit represented by the following schematic.

Step 1 (Mealy): Derive excitation equations.

$$\begin{split} D_0 &= Cnt \oplus Q_0 = Cnt'Q_0 + CntQ_0' \\ D_1 &= Cnt'Q_1 + CntQ_1'Q_0 + CntQ_1Q_0' \end{split}$$

Step 2a (Mealy): Derive the next-state equations.

$$\begin{split} Q_{0next} &= D_0 = Cnt \oplus Q_0 = Cnt'Q_0 + CntQ_0' \\ Q_{1next} &= D_1 = Cnt'Q_1 + CntQ_1'Q_0 + CntQ_1Q_0' \end{split}$$

Step 2b (Mealy): Derive the output equation.

$$Y = CntQ_1Q_0$$

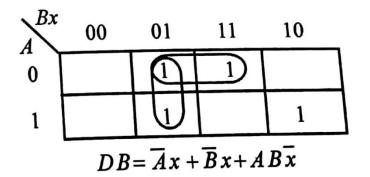

### Step 3a (Mealy):

Derive the next-state/output table. Every entry in the next-state table will represent the next-state and the output value, separated by a slash (/).

| Present State | Next State / Outputs                        |         |  |

|---------------|---------------------------------------------|---------|--|

| $Q_1Q_0$      | $Q_{1 \text{ next}} Q_{0 \text{ next}} / Y$ |         |  |

|               | Cnt = 0                                     | Cnt = 1 |  |

| 00            | 00 / 0                                      | 01 / 0  |  |

| 01            | 01/0                                        | 10 / 0  |  |

| 10            | 10 / 0                                      | 11 / 0  |  |

| 11            | 11 / 0                                      | 00 / 1  |  |

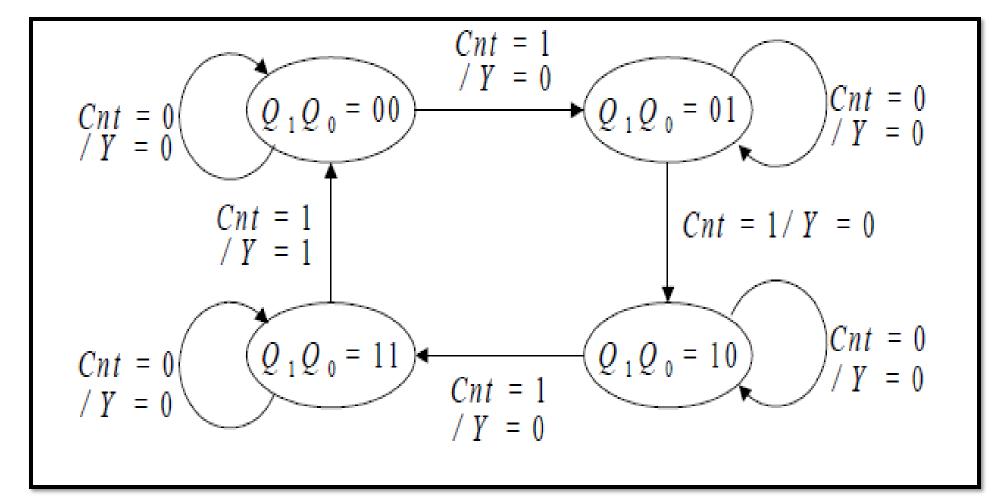

Step 3b (Mealy): Derive the State diagram.

The output is not associated with the state but with the transition arc.

Each arc is labeled with both the input values that move the circuits from the present state to the next state, and the output values, which correspond to the input-signal values in the present state.

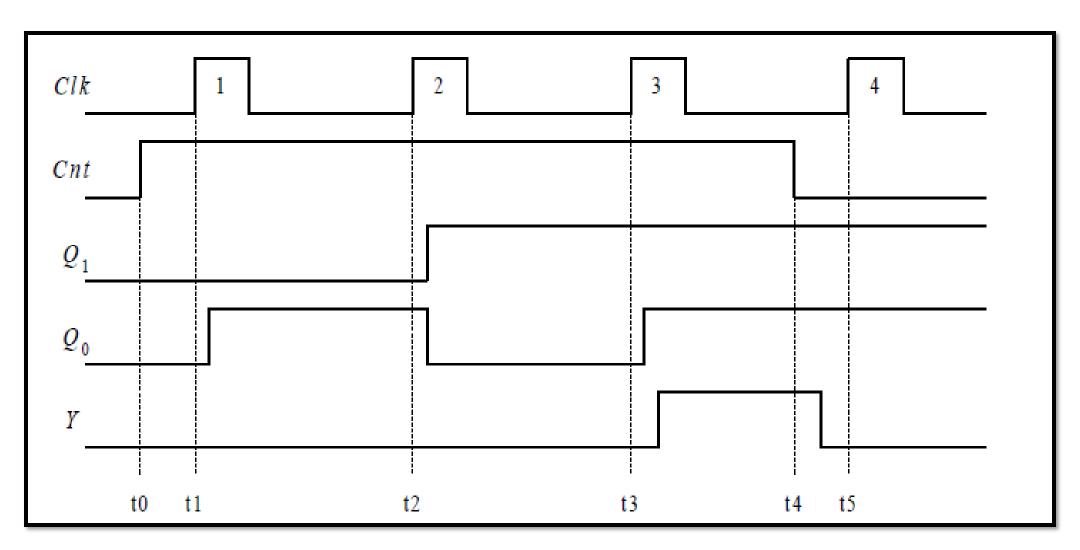

### Step 4 (Mealy): The timing diagram is shown below:

In clock cycle 3, the counter will be in state Q1Q0 = 11 and the output signal Y = 1. At t4, Y = 0 because the input signal Cnt = 0 even though the counter is still in state Q1Q0 = 11.

## THANK YOU