### SNS COLLEGE OF TECHNOLOGY

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

19ECB302-VLSI DESIGN

III YEAR/ V SEMESTER

UNIT 2 -COMBINATIONAL LOGIC CIRCUITS

TOPIC 9 – Design for low power principles

11/24/2023

## **OUTLINE**

- Power and Energy

- Dynamic Power Reduction

- Activity

- Static Power

- Low Power Design Principles

- Assessment

- Summary

## **Power and Energy**

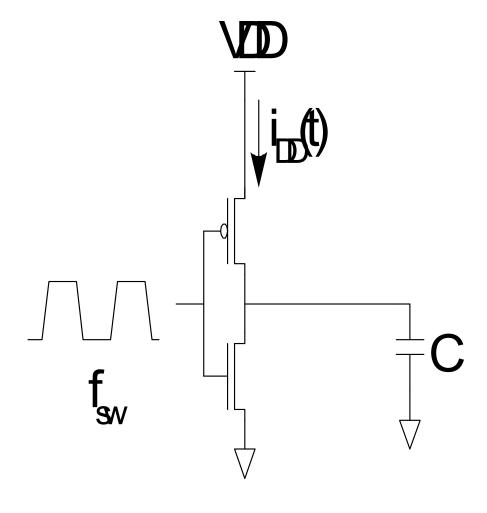

- Power is drawn from a voltage source attached to the V<sub>DD</sub> pin(s) of a chip.

- Instantaneous Power:  $P(t) = i_{DD}(t)V_{DD}$

- Energy:  $E = \int_{0}^{T} P(t)dt = \int_{0}^{T} i_{DD}(t)V_{DD}dt$

- Average Power:  $P_{\text{avg}} = \frac{E}{T} = \frac{1}{T} \int_{0}^{T} i_{DD}(t) V_{DD} dt$

## **Dynamic Power Reduction**

```

Dynamic Power Reduction (Pd)

Pd = \alpha C V_{DD}^{2} f c l k

f c l k \sim 2 C l c k

Frequency

\alpha \sim Activity factor

```

C ---. > Switching Capacitance

## **Dynamic Power Reduction**

- ➤ If the chip is active, dynamic power dissipation is high.

- $\triangleright$  Pd is reduced by reducing  $\alpha$  ,C  $V_{DD}$  or fclk.

- Clock gating is used to stop portions of the IC that are idle.

- ➤ Device switching capacitance can be reduced by using small transistors.

- ➤ Internet switching capacitance can be reduced by proper floor planning.

- ➤ If low power supply is used, then the power consumption is reduced

- ➤ When more transistors are operated in a velocity saturated region. So, the performance will not be reduced due to low power supply.

## **Dynamic Power**

- Dynamic power is required to charge and discharge load capacitances when transistors switch.

- One cycle involves a rising and falling output.

- On rising output, charge Q = CV<sub>DD</sub> is required

- On falling output, charge is dumped to GND

- This repeats Tf<sub>sw</sub> times over an interval of T

# Dynamic Power Cont.

$$P_{\text{dynamic}} = \frac{1}{T} \int_{0}^{T} i_{DD}(t) V_{DD} dt$$

$$= \frac{V_{DD}}{T} \int_{0}^{T} i_{DD}(t) dt$$

$$= \frac{V_{DD}}{T} \left[ T f_{\text{sw}} C V_{DD} \right]$$

$$= C V_{DD}^{2} f_{\text{sw}}$$

## **Activity Factor**

Suppose the system clock frequency = f Let  $f_{sw} = \alpha f$ , where  $\alpha$  = activity factor

- •If the signal is a clock,  $\alpha = 1$

- •If the signal switches once per cycle,  $\alpha = \frac{1}{2}$

- •Dynamic gates:

- •Switch either 0 or 2 times per cycle,  $\alpha = \frac{1}{2}$

- •Static gates:

- •Depends on design, but typically  $\alpha = 0.1$

## **Short Circuit Current**

- •When transistors switch, both nMOS and pMOS networks may be momentarily ON at once

- Leads to a blip of "short circuit" current.

- •< 10% of dynamic power if rise/fall times are comparable for input and output

# Example

•200 Mtransistor chip

20M logic transistors

Average width: 12  $\lambda$

180M memory transistors

Average width:  $4 \lambda$

•1.2 V 100 nm process

$C_g = 2 \text{ fF/}\mu\text{m}$

### **Dynamic Example**

- •Static CMOS logic gates: activity factor = 0.1

- Memory arrays: activity factor = 0.05 (many banks!)

- •Estimate dynamic power consumption per MHz.

Neglect wire capacitance.

$$C_{\text{logic}} = (20 \times 10^{6})(12\lambda)(0.05 \mu m/\lambda)(2 fF/\mu m) = 24 nF$$

$$C_{\text{mem}} = (180 \times 10^{6})(4\lambda)(0.05 \mu m/\lambda)(2 fF/\mu m) = 72 nF$$

$$P_{\text{dynamic}} = \left[0.1C_{\text{logic}} + 0.05C_{\text{mem}}\right](1.2)^{2} f = 8.6 \text{ mW/MHz}$$

# **Activity**

### **Static Power**

- ➤ More static power is consumed by pseudo n MOS gates.

- >Static power is consumed even when chip is quiescent.

- Ratioed circuits burn power in fight between ON

- -TransistorsLeakage draws power from nominally OFF devices.

- >Three parameters

- 1. Supply Voltage

- 2. Level Converter

- 3. Capacitance

# Ratio Example

The chip contains a 32 word x 48 bit ROM

Uses pseudo-nMOS decoder and bitline pullups

one wordline and 24 bitlines are high

Find static power drawn by the ROM

$$\beta = 75 \ \mu A/V^2$$

V<sub>tp</sub> = -0.4V

#### Solution

$$I_{\text{pull-up}} = \beta \frac{\left(V_{DD} - \left|V_{tp}\right|\right)^{2}}{2} = 24 \mu A$$

$$P_{\text{pull-up}} = V_{DD}I_{\text{pull-up}} = 29 \mu W$$

$$P_{\text{static}} = (31 + 24)P_{\text{pull-up}} = 1.6 \text{ mW}$$

# Leakage Example

- The process has two threshold voltages and two oxide thicknesses.

- Subthreshold leakage:

- $-20 \text{ nA/}\mu\text{m}$  for low  $V_t$

- -0.02 nA/ $\mu$ m for high  $V_t$

- Gate leakage:

- -3 nA/ $\mu$ m for thin oxide

- -0.002 nA/ $\mu$ m for thick oxide

- Memories use low-leakage transistors everywhere

- Gates use low-leakage transistors on 80% of logic

## Leakage Example

Estimate static power:

-High leakage:

$$(20 \times 10^6)(0.2)(12\lambda)(0.05\mu n/\lambda) = 24 \times 10^6 \mu n$$

-Low leakage:

$$I_{static} = (2.4 \times 10^{6} \,\mu m) [(20nA/\,\mu m)/2 + (3nA/\,\mu m)] + (45.6 \times 10^{6} \,\mu m) [(0.02nA/\,\mu m)/2 + (0.002nA/\,\mu m)]$$

$$= 32mA$$

$$P_{static} = I_{static} V_{DD} = 38mW$$

$$(20 \times 10^{6})(0.8)(12\lambda)(0.05 \,\mu m/\lambda) + (180 \times 10^{6})(4\lambda)(0.05 \,\mu m/\lambda) = 45.6 \times 10^{6} \,\mu m$$

• if no low leakage devices,  $P_{\text{static}} = 749 \text{ mW}$  (!)

# Low Power Design principles

#### Reduce dynamic power

$\alpha$ : clock gating, sleep mode

C: small transistors (esp. on clock), short

wires

V<sub>DD</sub>: lowest suitable voltage

f: lowest suitable frequency

#### Reduce static power

Selectively use ratioed circuits

Selectively use low V<sub>t</sub> devices

Leakage reduction:

stacked devices, body bias, low

temperature

### Assessment

- Reduce dynamic power---????????

- $-\alpha$ :

- -C

- $-V_{DD}$ :

- -F:

- Reduce static power-Fill up the blanks???

- -Selectively use -----circuits

- -Selectively use low -----devices

- ----- reduction:

- -----devices, ----- bias,-----

- temperature

### **THANK YOU**