11/24/202

## **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## **19ECB302–VLSI DESIGN**

III YEAR/ V SEMESTER

## UNIT 2 – COMBINATIONAL LOGIC CIRCUITS

TOPIC 2 & 3 – Pass transistor Logic, Transmission gates

A Brief History

CMOS Gate Design

Pass Transistors

Transmission Gate logic

Activity

Assessment

➢ Summary

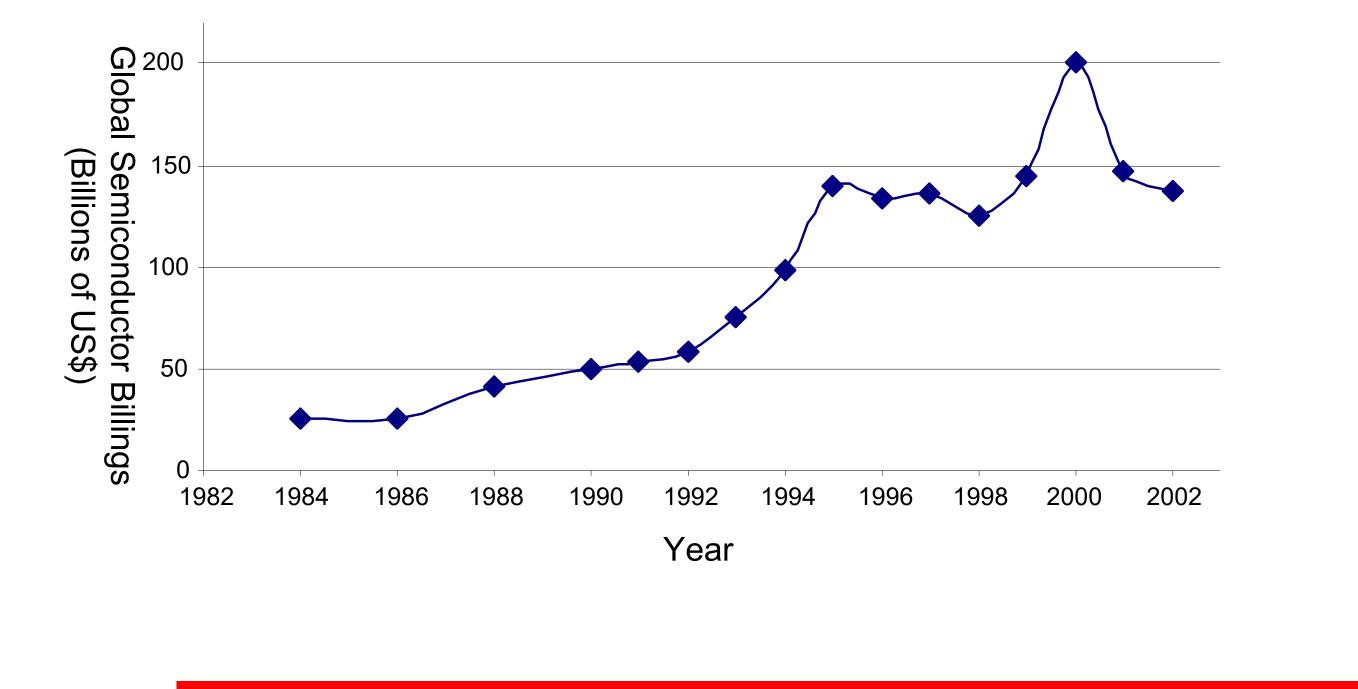

## **A Brief History**

#### **1958**: First integrated circuit

- ► Flip-flop using two transistors

- Built by Jack Kilby at Texas Instruments

#### **2003**-Intel Pentium 4 mprocessor (55 million transistors)

512 Mbit DRAM (> 0.5 billion transistors) miniaturization of transistors Smaller is cheaper, faster, lower mere Revolutionary effects on society

#### **Annual Sales**

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

## **Transistor Types**

#### **Bipolar transistors**

- npn or pnp silicon structure

- Small current into very thin base layer controls large currents between emitter and collector

- Base currents limit integration density

#### > Metal Oxide Semiconductor Field Effect Transistors

- nMOS and pMOS MOSFETS

- Voltage applied to insulated gate controls current between source and drain

- Low power allows very high integration

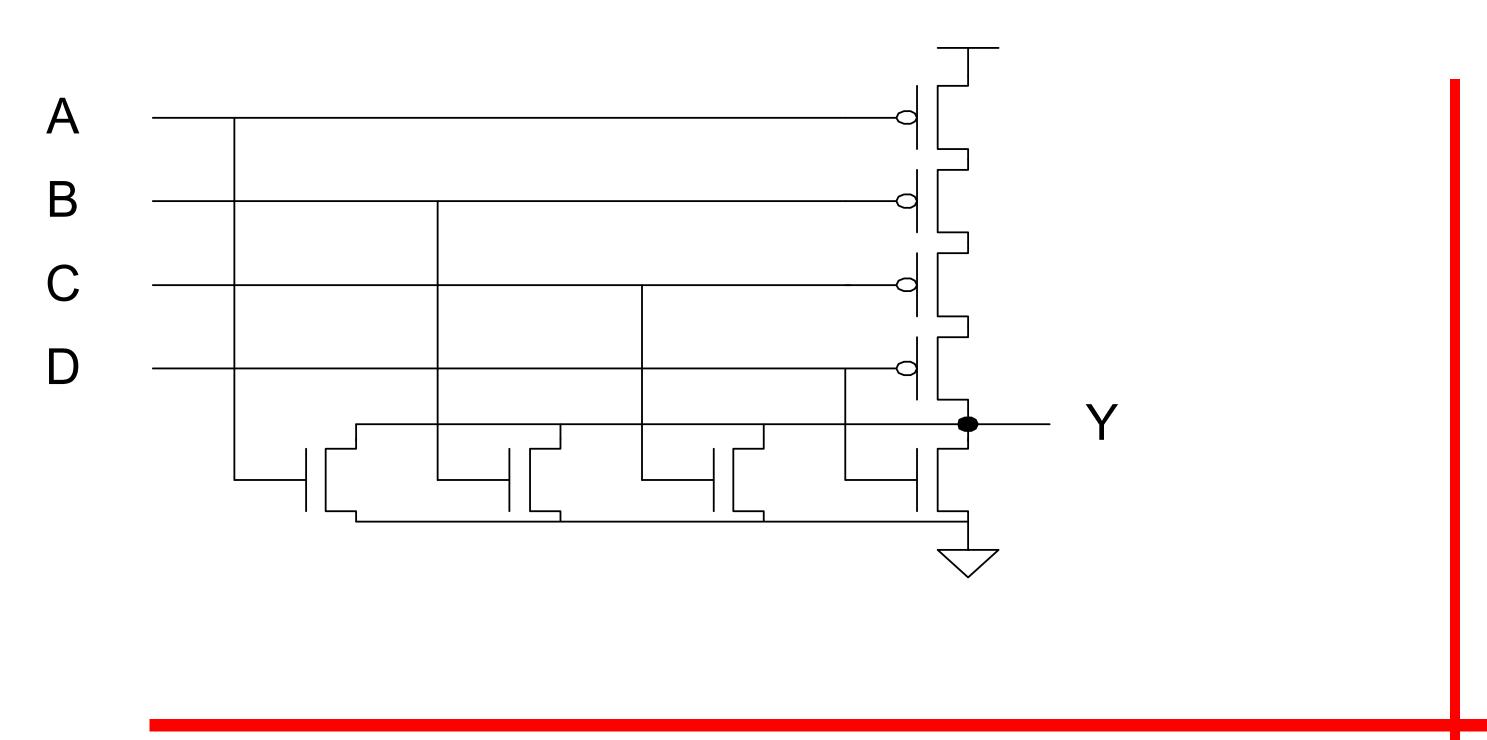

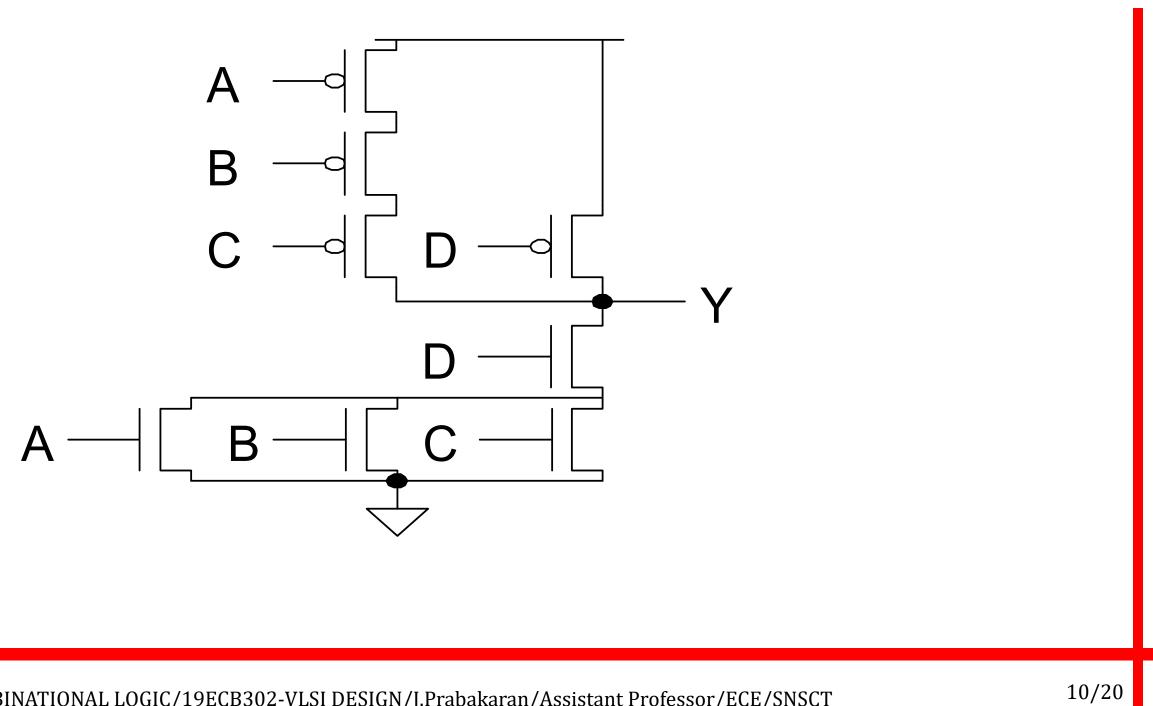

## **CMOS Gate Design-4 input NOR**

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

#### **Series and Parallel Connections**

- nMOS: 1 = ON

- pMOS: 0 = ON

- *Series*: both must be ON

- *Parallel*: either can be ON

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

## **Conduction Complement**

- Complementary CMOS gates always produce 0 or 1

- Ex: NAND gate- .ns—n-MOS Series—pMOS parallel

- Series nMOS: Y=0 when both inputs are 1

- Thus Y=1 when either input is 0

- Requires parallel pMOS

- Rule of Conduction Complements

- Pull-up network is complement of pull-down

- Parallel -> series, series -> parallel

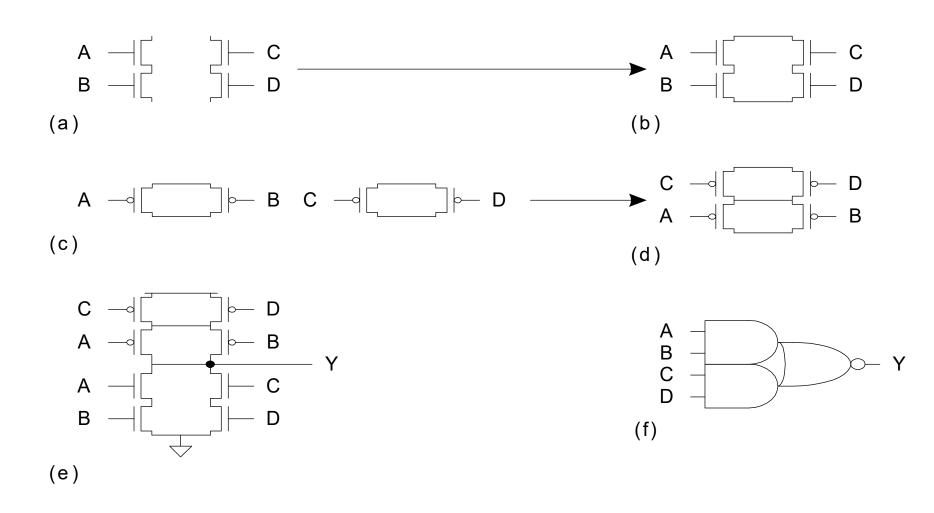

## **Compound Gates**

- Compound gates can do any inverting function

- Ex:  $Y = \overline{A \ B + C \ D}$  (AND-AND-OR-INVERT, AOI22)

### **Example: O3AI**

$Y = \overline{\left(A + B + C\right) D}$

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

11/24/2023

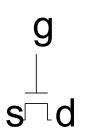

## **Strength of Signal**

How close it approximates ideal voltage source V<sub>DD</sub> and GND rails are strongest 1 and 0 •nMOS pass strong 0 But degraded or weak 1 •pMOS pass strong 1 But degraded or weak 0 Thus nMOS are the state pull-down network

g s⊡d

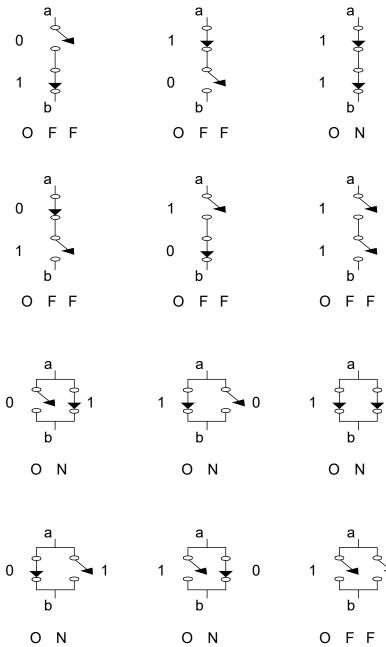

#### **Pass Transistors**

# Transistors can be used as switches

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Asseant Professor/ECE/SNSCT

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

11/24/2023

$$g = 1$$

Output

→ strong 0

$g = 1$

→ degraded 1

$g = 0$  Output

$g = 0$  Output

$g = 0$  degraded 0

$g = 0$

→ degraded 0

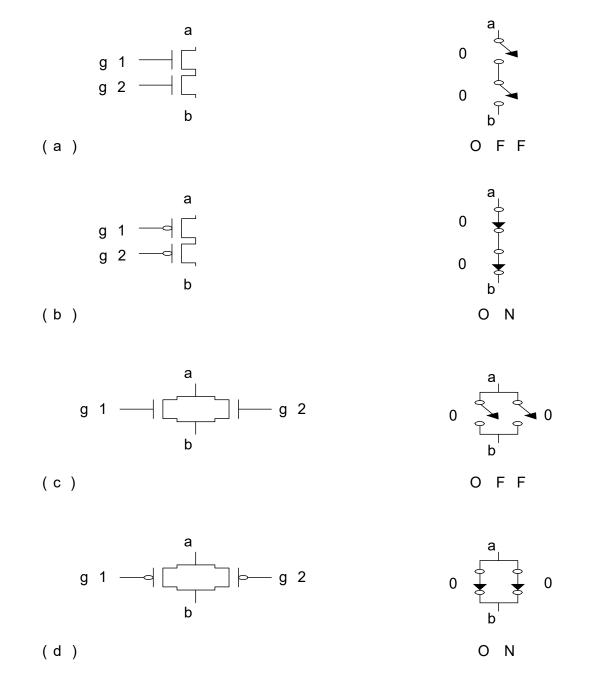

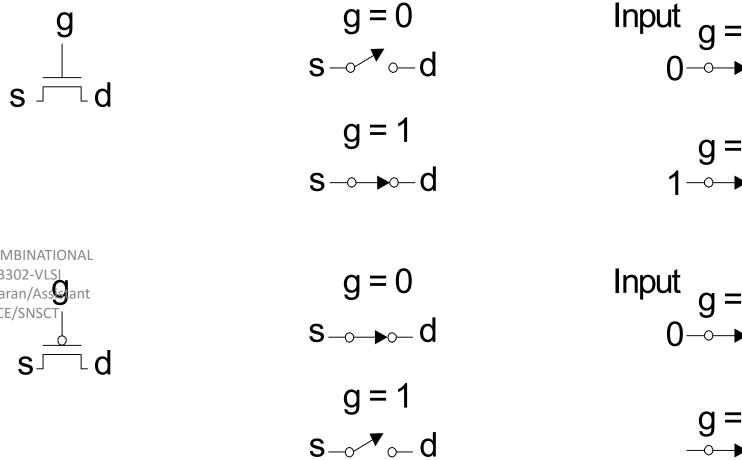

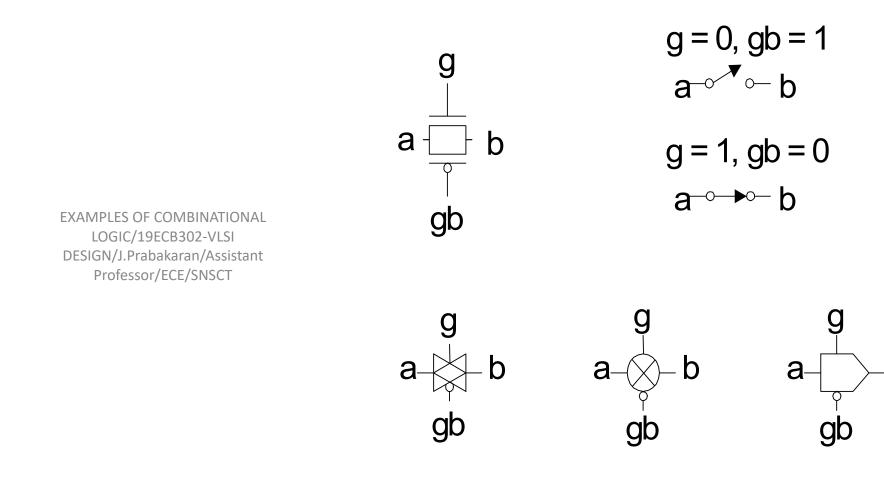

#### **Transmission Gates**

- Pass transistors produce degraded outputs

- *Transmission gates* pass both 0 and 1 well

11/24/2023

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

#### Input Output g = 1, gb = 0 $0 \rightarrow \infty$ strong 0 g = 1, gb = 0 $1 \rightarrow \infty$ strong 1

b

#### **Tristates**

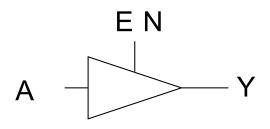

#### Tristate buffer produces Z when not enabled

| А              | Y                                       |

|----------------|-----------------------------------------|

| 0              | Z                                       |

| 1              | Z                                       |

| 0              | 0                                       |

| LSI<br>sistant | 1                                       |

|                | A<br>0<br>1<br>0<br>FIQNAL<br>LSI<br>CT |

11/24/2023

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

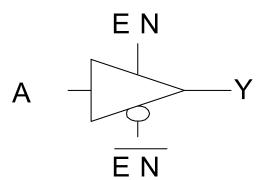

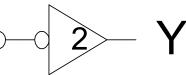

#### Non restoring Tristate

- Transmission gate acts as tristate buffer

- Only two transistors

- But non restoring

- Noise on A is passed on to Y

**EXAMPLES OF COMBINATIONAL** LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

11/24/2023

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

Α

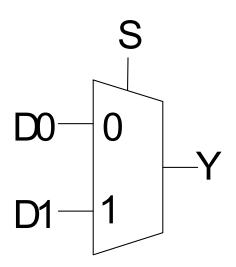

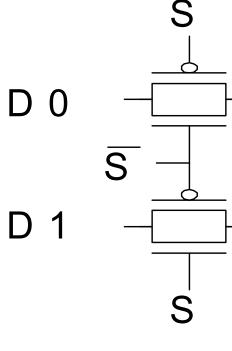

### Multiplexers

#### • 2:1 multiplexer chooses between two inputs

|                                                                                                    | S | D1 | D0 | Y |

|----------------------------------------------------------------------------------------------------|---|----|----|---|

|                                                                                                    | 0 | Х  | 0  | 0 |

|                                                                                                    | 0 | Х  | 1  | 1 |

|                                                                                                    | 1 | 0  | Х  | 0 |

| EXAMPLES OF COMBINATIO<br>LOGIC/19ECB302-VLSI<br>DESIGN/J.Prabakaran/Assist<br>Professor/ECE/SNSCT | 1 | 1  | Х  | 1 |

11/24/2023

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

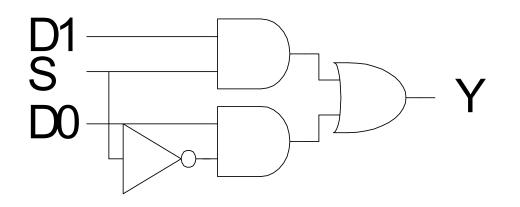

## **Gate-Level Mux Design**

#### $Y = SD_1 + \overline{S}D_0$ (too many transistors)

How many transistors are needed? 20

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

11/24/2023

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

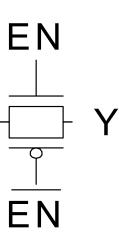

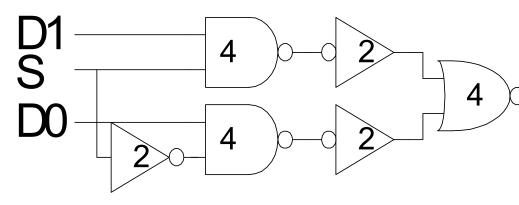

## **Transmission Gate Mux**

- Nonrestoring mux uses two transmission gates

- Only 4 transistors

**EXAMPLES OF COMBINATIONAL** LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

11/24/2023

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

D 1

Y

#### Assessment

How many transistors are needed to

make 2:1 Mux? ----

Draw 2:1 mux using TG

Draw 4:1 mux using TG

nMOS pass strong -----EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran Butthidegraded or weak ------Professor/ECE/SNSCT

pMOS pass strong -----

But degraded or weak ------

Thus nMOS are best for pull-down network

11/24/2023

#### **THANK YOU**

EXAMPLES OF COMBINATIONAL LOGIC/19ECB302-VLSI DESIGN/J.Prabakaran/Assistant Professor/ECE/SNSCT

11/24/2023