# SNS COLLEGE OF TECHNOLOGY, COIMBATORE –35 (An Autonomous Institution)

### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

#### Standard I/O Interfaces

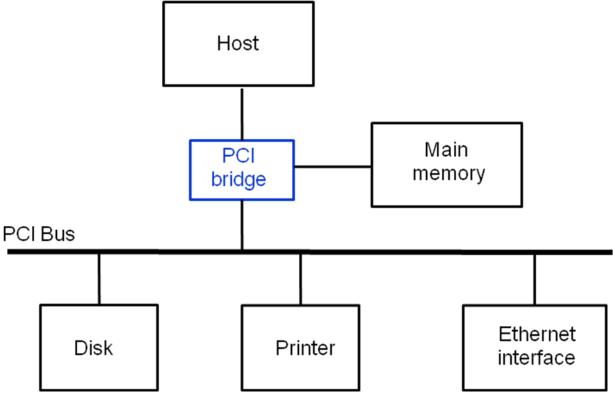

- The processor bus is the bus defined by the signals on the processor chip itself. Devices that require a very high speed connection to the processor, such as themain memory, may be connected directly to this bus

- > The motherboard usually provides another bus that can support more devices.

- The two buses are interconnected by a circuit, which we called a bridge, that translates the signals and protocols of one bus into those of the other

- It is impossible to define a uniform standards for is closely tied to the architecture of the processor

the processor bus. The structure of this bus

- The expansion bus is not subject to these limitations, and therefore it can use a standardized signaling structure

Peripheral Component Interconnect Bus

#### PCI Bus

- > The bus support three independent address spaces: memory, I / O, and configuration.

- > The I / O address space is intended for use with processors, such Pentium, that have a separate I

COMPUTER ORGANIZATION AND ARCHITECTURE / S.VASUKI / CSE / SNSCT

## SNS COLLEGE OF TECHNOLOGY, COIMBATORE –35 (An Autonomous Institution)

DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

/ O address space.

- However, the system designer may choose to use memory-mapped I / O even when a separate I / O address space is available

- > The configuration space is intended to give the PCI its plug-and-play capability.

- ♦ A 4-bit command that accompanies the address identifies which of the three spaces is being used in a given data transfer operation

Universal Serial Bus (USB

- > The USB has been designed to meet several key objectives

- Provide a simple, low-cost, and easy to use interconnection system that overcomes the difficulties due to the limited number of I / O ports available on a computer

- Accommodate a wide range of data transfer characteristics for I / O devices, including telephone and Internet connections

- Enhance user convenience through a "plug-and-play" mode of operation

USB Structure

- The tree structure enables many devices to be connected while using only simple point-to-point serial links

- > Each hub has a number of ports where devices may be connected, including other hubs

- In normal operation, a hub copies a message that it receives from its upstream connection to all its downstream ports

- As a result, a message sent by the host computer is broadcast to all I / O devices, but only the addresse d device will respond to that message

- A message sent from an I / O de vice is sent only upstream towards the root of the tree and is not seen by other devices

- Hence, USB enables the host to communicate with the I / O devices, but it does not enable these devices to communicate with each other

USB Protocols

- All information transferred over the USB is organized in packets, where a packet consists of one or more bytes of information

- The information transferred on the USB can be divided into two broad categories: control and data

- Control packets perform such tasks as addressing a device to initiate data transfer, acknowledging that data have been received correctly, or indicating an error

- Data packets carry information that is delivered to a device. For example, input and output data are transferred inside data packets