# UNIT III PROCESSOR AND PIPELINING

Fundamental concepts – Execution of a complete instruction – Multiple bus organization – Hardwired control – Micro programmed control – **Pipelining: Basic concepts** – Data hazards – Instruction hazards – Influence on Instruction sets – Data path and control consideration.

2/24

# Recap the previous Class

- Widely used in modern processor

- Executing machine instructions concurrently

- Improve System performance in terms of throughput

- Requires sophisticated complication Technique

A.Aruna / AP / IT / SEM 2 / COA

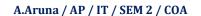

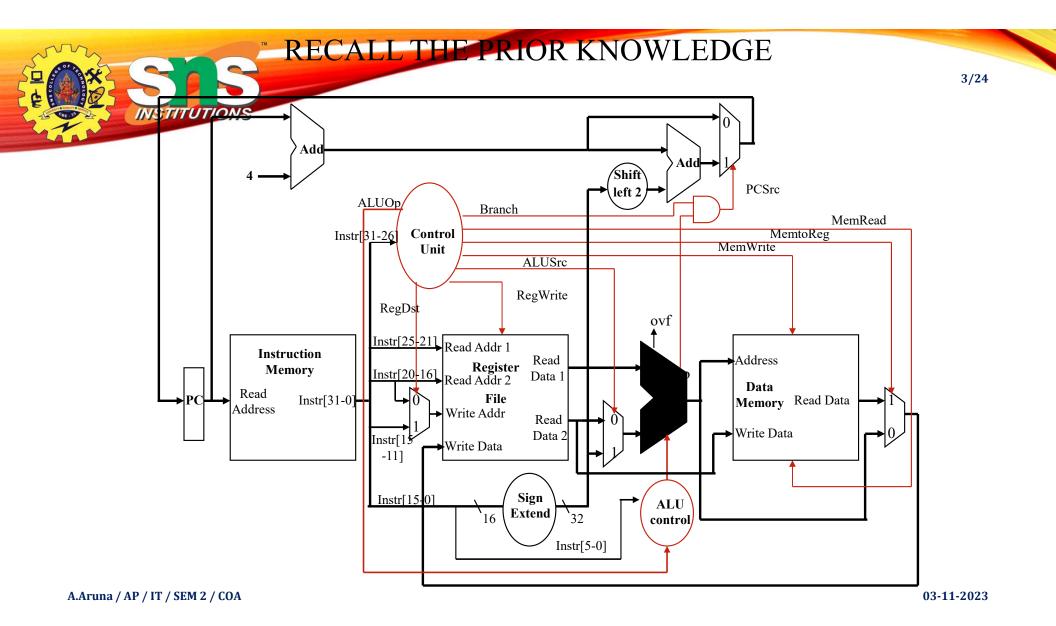

# **INSTRUCTION EXECUTION**

A.Aruna / AP / IT / SEM 2 / COA

INSTITUTIONS

03-11-2023

- Faster circuit technology to build the processor and the main memory

- Arrange the hardware so that more than one operation can be performed at the same time

- Number of operations performed per second is increased

# WHAT IS PIPELINING?

Overlapping of instruction Improve Performance

### REQUIREMENTS

**Three Students – Act as Processor** Resources Ball Calculate the Throughput and Response Time ?

Activity Set 1 : Rules complete the task one by one

Activity Set 2 : Rules complete the task in parallel

A.Aruna / AP / IT / SEM 2 / COA

INSTITUTION

- Effective way of organizing concurrent activity in a computer system.

- Analogy assembly-line operation in car manufacturing Sector.

- welding

- Painting

- Polishing

# What Is Pipelining?

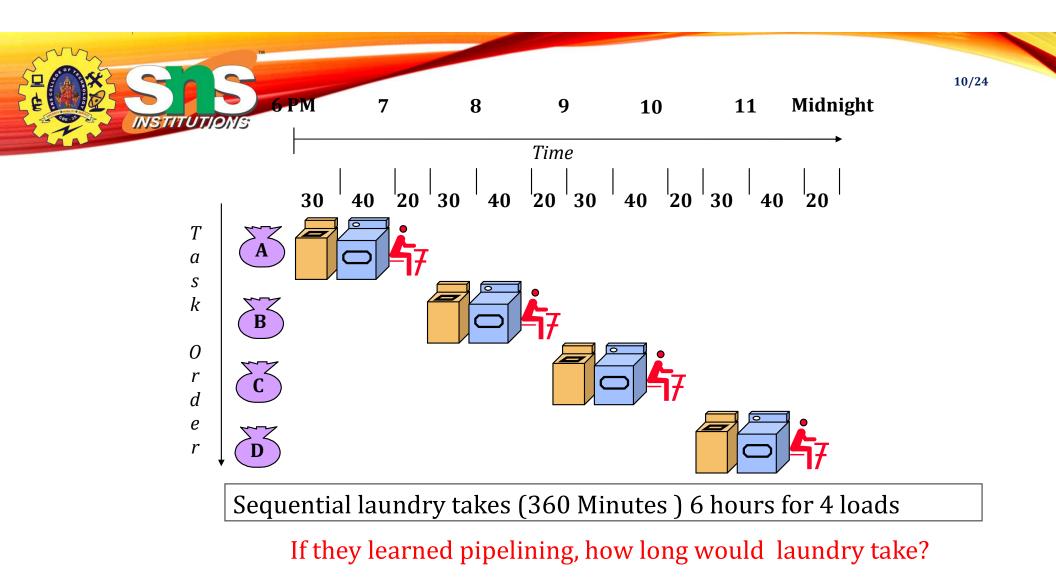

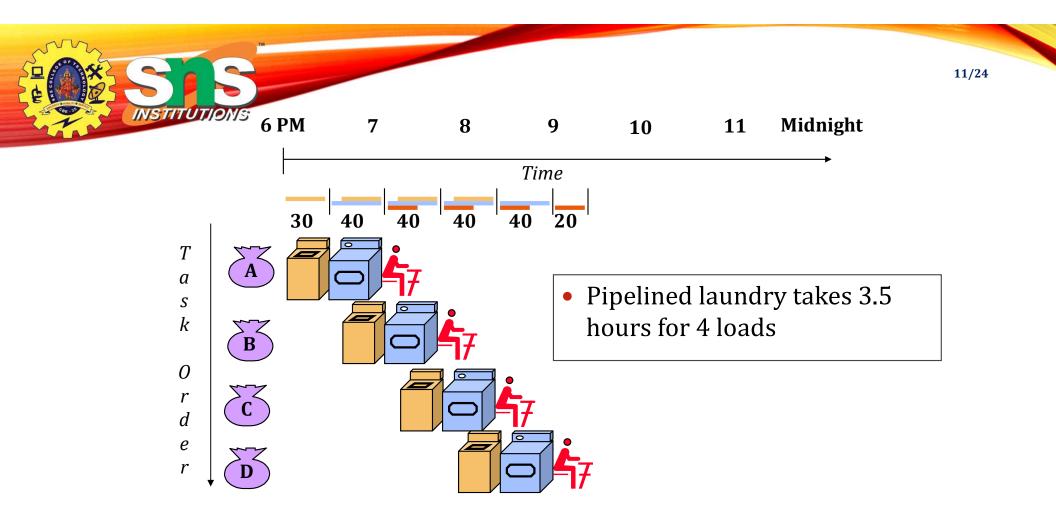

### Laundry Example

- Ann, Brian, Cathy, Dave , each have one load of clothes to wash, dry, and fold

- Washer takes 30 minutes

- Dryer takes 40 minutes

- "Folder" takes 20 minutes

A.Aruna / AP / IT / SEM 2 / COA

03-11-2023

# **PIPELINE Characteristics**

### **Balanced (all take the same time)**

Time between instructions

Time between instructions<sub>nonpipelined</sub> / Number of stages

### Not balanced

Speedup is less

Speedup due to increased throughput Latency (Time for each instruction) does not decrease

A.Aruna / AP / IT / SEM 2 / COA

12/24

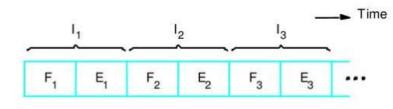

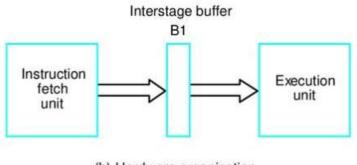

# Idea of pipelining in computer

INSTITUTIONS

(a) Sequential execution

(b) Hardware organization

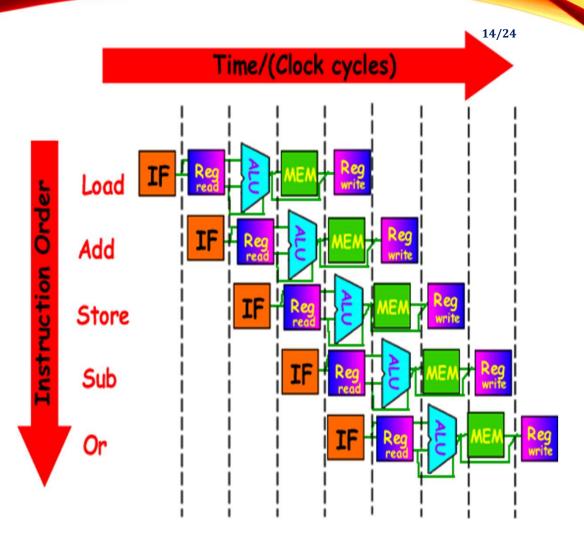

Time 2 Clock cycle 3 1 4 Instruction F<sub>1</sub> E1 4  $F_2$  $E_2$ 1<sub>2</sub> I3  $F_3$ E<sub>3</sub> (c) Pipelined execution

A.Aruna / AP / IT / SEM 2 / COA

03-11-2023

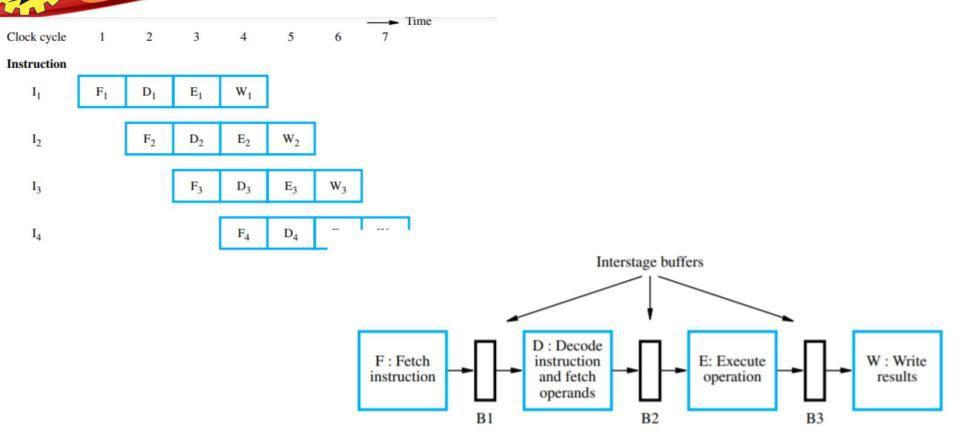

**F Fetch:** read the instruction from the memory.

**D Decode:** decode the instruction and fetch the source operand(s).

**E Execute:** perform the operation

specified by the instruction.

INSTITUT

**W Write:** store the result in the

destination location

A.Aruna / AP / IT / SEM 2 / COA

INSTITUTIONS

03-11-2023

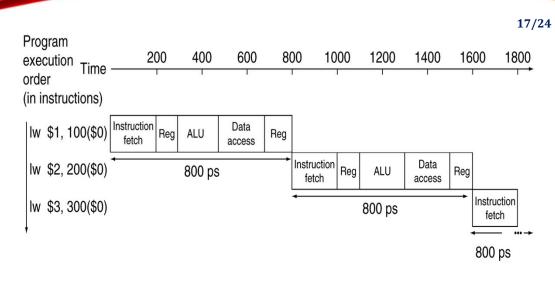

# **Pipeline Performance**

• Assume time for stages is

NSTITUTION

- 100ps for register read or write

- 200ps for other stages

## • Compare pipelined datapath with single-cycle datapath

| Instruction | Instructio<br>n fetch | Register<br>read | ALU op | Memory<br>access | Register<br>write | Total time |

|-------------|-----------------------|------------------|--------|------------------|-------------------|------------|

| Load        | 200ps                 | 100 ps           | 200ps  | 200ps            | 100 ps            | 800ps      |

| Store       | 200ps                 | 100 ps           | 200ps  | 200ps            |                   | 700ps      |

| R-format    | 200ps                 | 100 ps           | 200ps  |                  | 100 ps            | 600ps      |

| Branch      | 200ps                 | 100 ps           | 200ps  |                  |                   | 500ps      |

### Single-cycle (T<sub>c</sub>= 800ps)

### Program 200 400 600 800 1000 1200 1400 execution order Time (in instructions) Instruction Data Iw \$1, 100(\$0) Reg ALU Reg fetch access Instruction lw \$2, 200(\$0) 200 ps Data Reg ALU Reg fetch access Instruction Data lw \$3, 300(\$0) Reg 200 ps ALU Reg fetch access 200 ps 200 ps 200 ps 200 ps 200 ps

Pipelined (T<sub>c</sub>= 200ps)

A.Aruna / AP / IT / SEM 2 / COA

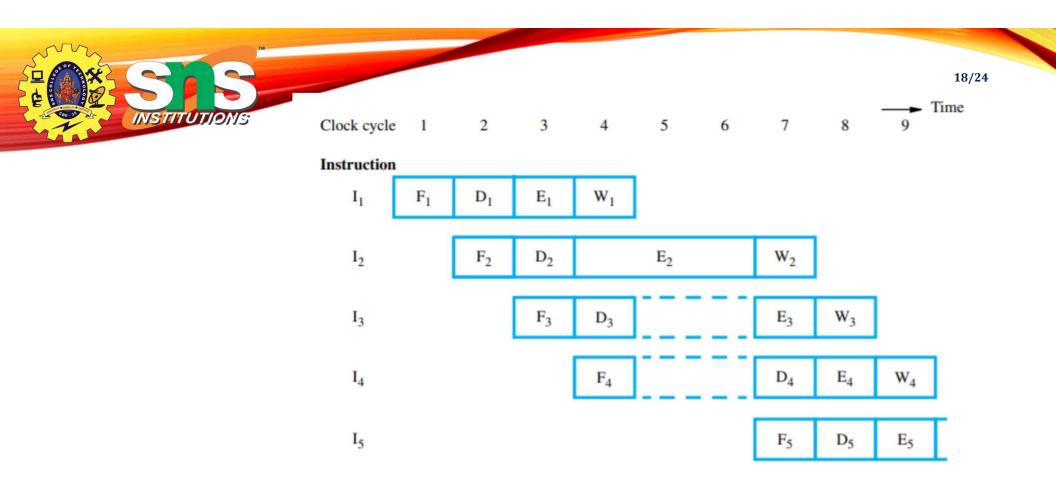

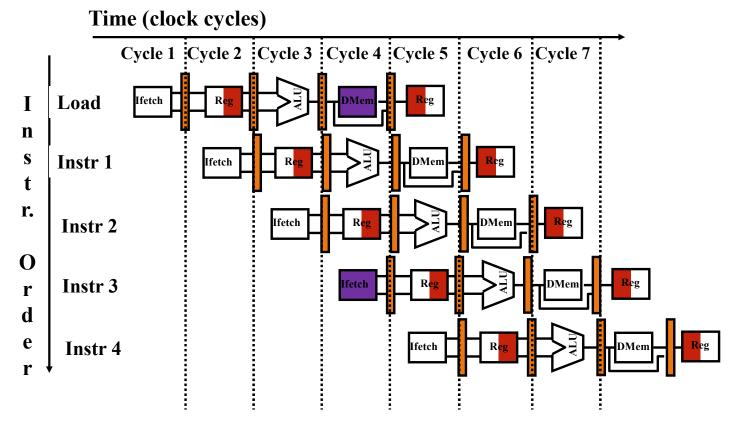

### Effect of an execution operation taking more than one clock cycle

A.Aruna / AP / IT / SEM 2 / COA

|                                             | S     | TM             |                |                |                |                |                |                |                       |   |                       |                |                       | 19/24<br>→ Time       |

|---------------------------------------------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|---|-----------------------|----------------|-----------------------|-----------------------|

| INSTITU                                     | TIONS |                |                |                | Clock cycle    | 1              | 2              | 3              | 4                     | 5 | 6                     | 7              | 8                     | 9                     |

|                                             |       |                |                |                | Instruction    | -              |                | _              |                       |   |                       |                |                       |                       |

|                                             |       |                |                |                | I1             | F <sub>1</sub> | D <sub>1</sub> | E <sub>1</sub> | <b>W</b> <sub>1</sub> |   |                       |                |                       |                       |

| Pipeline stall caused by a cache miss in F2 |       |                |                |                | I <sub>2</sub> |                |                | F              | 2                     |   | D <sub>2</sub>        | E <sub>2</sub> | <b>W</b> <sub>2</sub> |                       |

|                                             |       |                |                |                | I <sub>3</sub> |                |                |                |                       |   | F <sub>3</sub>        | D <sub>3</sub> | E <sub>3</sub>        | <b>W</b> <sub>3</sub> |

|                                             |       |                | 2              |                | -              |                |                | -              |                       |   |                       | me             |                       |                       |

| Clock cycle                                 | 1     | 2              | 3              | 4              | 5              | 6              | )              | 7              | 8                     |   | 9                     |                |                       |                       |

| Stage                                       |       |                |                |                |                |                |                |                |                       |   |                       |                |                       |                       |

| F: Fetch                                    | $F_1$ | $F_2$          | F <sub>2</sub> | $F_2$          | F <sub>2</sub> | F              | 3              |                |                       |   |                       |                |                       |                       |

| D: Decode                                   |       | D <sub>1</sub> | idle           | idle           | idle           | D              | 2              | $D_3$          |                       |   |                       |                |                       |                       |

| E: Execute                                  |       |                | $E_1$          | idle           | idle           | id             | le             | E <sub>2</sub> | E <sub>3</sub>        |   |                       |                |                       |                       |

| W: Write                                    |       |                |                | $\mathbf{W}_1$ | idle           | id             | le             | idle           | W <sub>2</sub>        | 2 | <b>W</b> <sub>3</sub> |                |                       |                       |

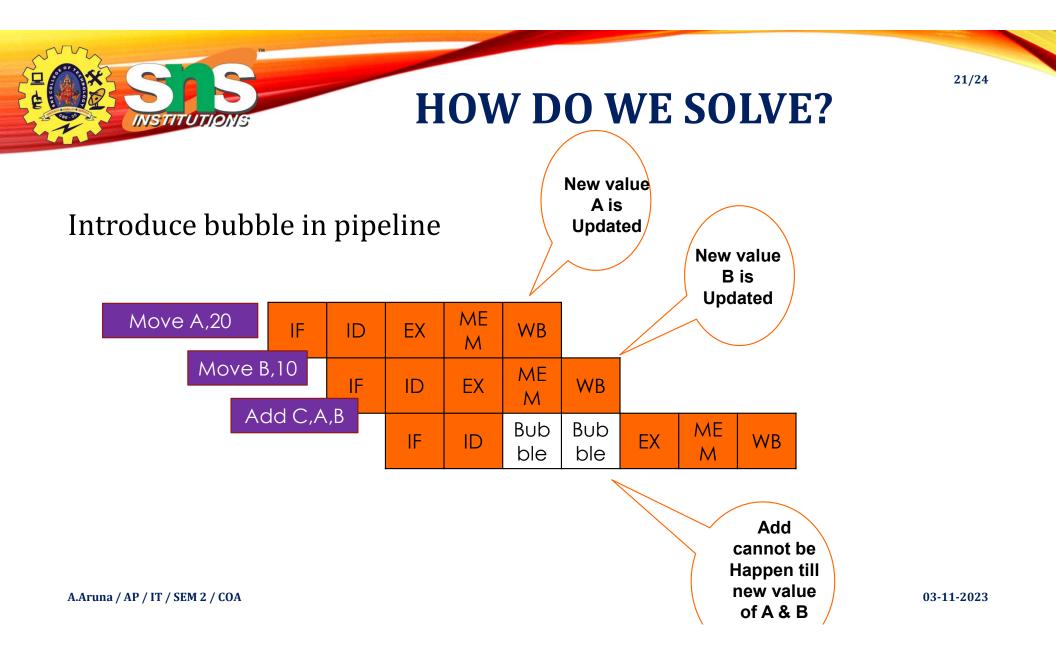

DATA Need to wait for previous instruction HAZARDS

HAZARDS

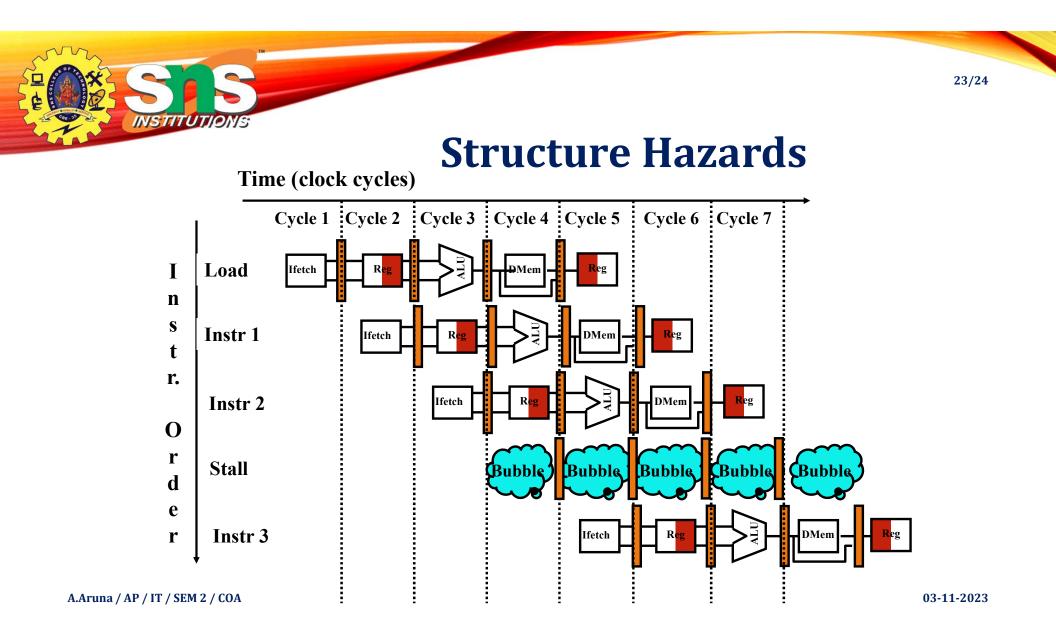

STRUCTURAL HAZARDS

required resource is busy

A.Aruna / AP / IT / SEM 2 / COA

CONTROL HAZARDS

**Deciding on control action**

20/24

A.Aruna / AP / IT / SEM 2 / COA

03-11-2023

A.Aruna / AP / IT / SEM 2 / COA