# **UNIT II ARITHMETIC OPERATIONS**

Addition and subtraction of signed numbers – Design of fast adders – Multiplication of positive numbers - Signed operand multiplication- fast multiplication – Integer division – Floating point numbers and operations

## **Recap the previous Class**

Ms.A.Aruna / AP / IT / SEM 3 / COA

## **Design of Fast Multiplier**

### a)Bit-Pair Recoding of Booth's Multiplication

–A technique that <u>halves the maximum number of summands</u>; derived directly from the Booth's algorithm.

–If we **group the Booth-coded multiplier digits in pairs**, we observe:

(+1, -1): (+1, -1) \* M = 2 \* M - M = M(0, +1): (0, +1) \* M = M

–We need a single addition instead of a pair of addition & subtraction.

•Other similar rules can be framed.

Ms.A.Aruna / AP / IT / SEM 3 / COA

INSTITUTION

| Yi+1 | Yi | Yi-1 | Partial Products |

|------|----|------|------------------|

| 0    | 0  | 0    | 0*Multiplicand   |

| 0    | 0  | 1    | 1*Multiplicand   |

| 0    | 1  | 0    | 1*Multiplicand   |

| 0    | 1  | 1    | 2*Multiplicand   |

| 1    | 0  | 0    | -2*Multiplicand  |

| 1    | 0  | 1    | -1*Multiplicand  |

| 1    | 1  | 0    | -1*Multiplicand  |

| 1    | 1  | 1    | -0*Multiplicand  |

Ms.A.Aruna / AP / IT/ SEM 3 / COA

**Design of Fast Multiplier**

| Original Booth-<br>coded Pair | Equivalent<br>Recoded Pair |

|-------------------------------|----------------------------|

| (+1, 0)                       | (0, +2)                    |

| (-1, +1)                      | (0, -1)                    |

| (0, 0)                        | (0, 0)                     |

| (0, 1)                        | (0, 1)                     |

| (+1, 1)                       |                            |

| (+1, -1)                      | (0, +1)                    |

| (-1, 0)                       | (0, -2)                    |

- Every equivalent recoded pair has at least one 0.

- Worst-case number of additions or subtractions is 50% of the number of multiplier bits.

- Reduces the worst-case time required for multiplication.

| INSTITUTIONS | <b>Example</b> : | (+1: | 3) 2 | X (- | -22) | in | 6-bits. |

|--------------|------------------|------|------|------|------|----|---------|

| Original:    | Multiplier       | 1    | 0    | 1    | 0    | 1  | 0       |

| Booth:       | Multiplier       | -1   | +1   | -1   | +1   | -1 | 0       |

| Recoded:     | Multiplier       | 0    | -1   | 0    | -1   | 0  | -2      |

|       | 0 0 1     | 1 0 1 |

|-------|-----------|-------|

|       |           |       |

| 11111 | L 1 1 0   |       |

|       |           | 0110  |

| 111   | 1 1 1 0 0 | ) 1 1 |

| 111   | 1 0 0 1 1 | -     |

| 110   | 1 1 1 1 0 | 0010  |

M = 001101(+13)-1 \* M = 110011-2 \* M = 100110

Ms.A.Aruna / AP / IT / SEM 3 / COA

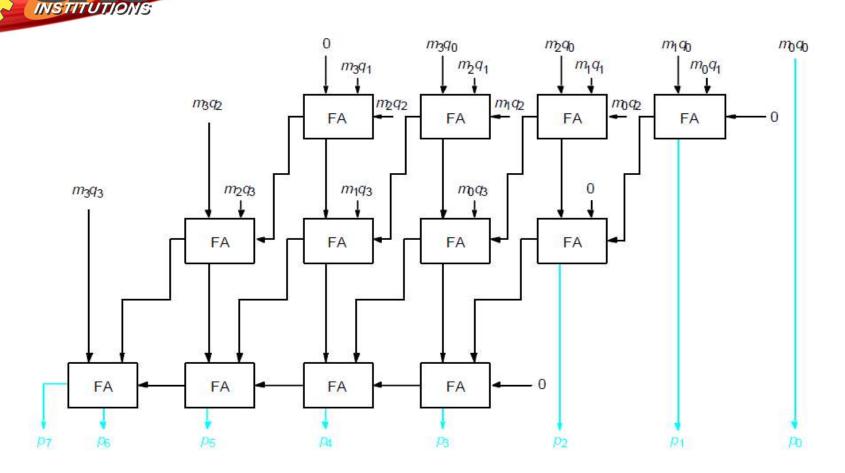

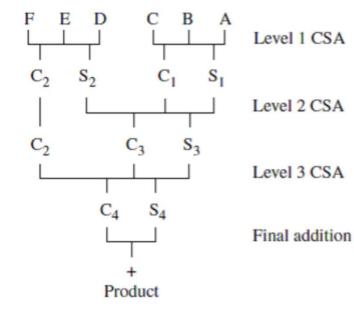

## b) Carry Save Multiplier

- We have seen earlier how carry save adders (CSA) can be used to add several numbers with carry propagation only in the last stage.

- The **partial products** can be generated in **parallel using n<sup>2</sup> AND gates**.

- The n partial products can then be added using a **CSA tree**.

- Instead of letting the carries ripple through during addition, we *save* them and feed it to the next row, at the correct weight positions.

4 x 4 Carry Save Multiplier

Ms.A.Aruna / AP / IT / SEM 3 / COA

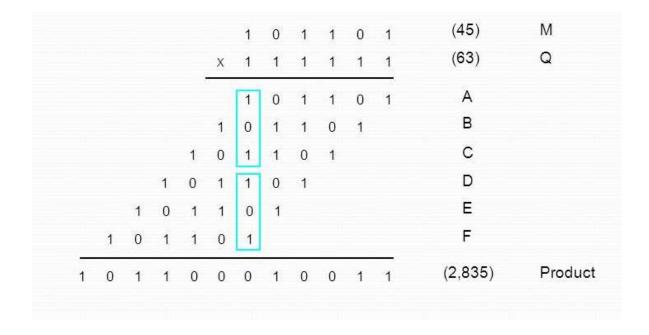

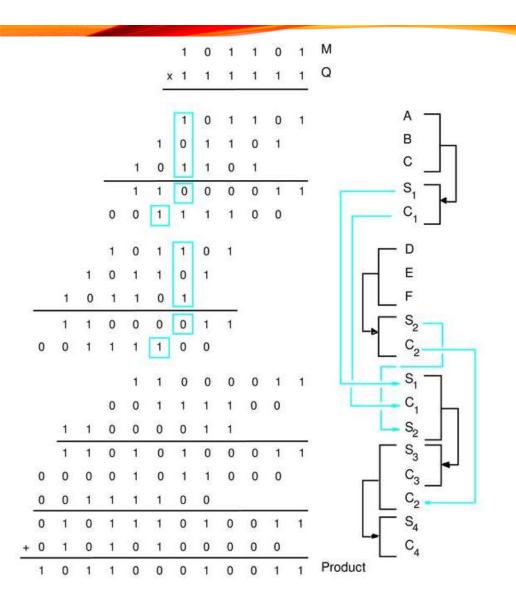

• Consider the number 45 x 63. Perform Carry save addition

Ms.A.Aruna / AP / IT / SEM 3 / COA

Ms.A.Aruna / AP / IT / SEM 3 / COA

)2-11-2023

### Wallace Tree Multiplier

-A Wallace tree is a circuit that reduces the problem of summing n n-bit numbers to the problem of summing two  $\Theta(n)$ -bit numbers.

INSTIT

- -It uses n/3 (floor of) carry-save adders in parallel to convert the sum of n numbers to the sum of 2n/3 (ceiling of) numbers.

- -It then recursively constructs a Wallace tree on the 2n/3 (ceiling of) resulting numbers.

- -The set of numbers is progressively reduced until there are only two numbers left.

-By performing many carry-save additions in parallel, Wallace trees allow two n-Ms.A.Arunabit/numbers to be multiplied in  $\Theta(\log_2 n)$  time using a circuit of size  $\Theta(n_2^2)_{1-2023}$

- $\bullet$  The figure shows a Wallace tree that adds 8 partial products  $m^{(0)},\ m^{(1)},\ ...,\ m^{(7)}.$

- The partial product  $m^{(i)}$  consists of (n+i) bits.

- •Each line represents an entire number the label of an edge indicates the number of bits.

- •The carry-lookahead adder at the bottom adds a (2n-1)-bit number to a 2n-bit number to give the 2n-bit product.

Ms.A.Aruna / AP / IT / SEM 3 / COA

#### **TEXT BOOK**

Carl Hamacher, Zvonko Vranesic and Safwat Zaky, "Computer Organization", McGraw-Hill, 6th Edition 2012.

#### REFERENCES

- 1. David A. Patterson and John L. Hennessey, "Computer organization and design", MorganKauffman ,Elsevier, 5th edition, 2014.

- 2. William Stallings, "Computer Organization and Architecture designing for Performance", Pearson Education 8th Edition, 2010

- 3. John P.Hayes, "Computer Architecture and Organization", McGraw Hill, 3rd Edition, 2002

- 4. M. Morris R. Mano "Computer System Architecture" 3rd Edition 2007

- 5. David A. Patterson "Computer Architecture: A Quantitative Approach", Morgan Kaufmann; 5th edition 2011

#### **THANK YOU**

Ms.A.Aruna / AP / IT/ SEM 3 / COA