## SNS COLLEGE OF TECHNOLOGY

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

19ECB202 – LINEAR AND DIGITAL CIRCUITS

II YEAR/ III SEMESTER

1

UNIT 5 - SEQUENTIAL CIRCUITS and PLC

TOPIC 1 – FLIP FLOP FUNDAMENTALS and SR Flipflop

# Sequential Circuits

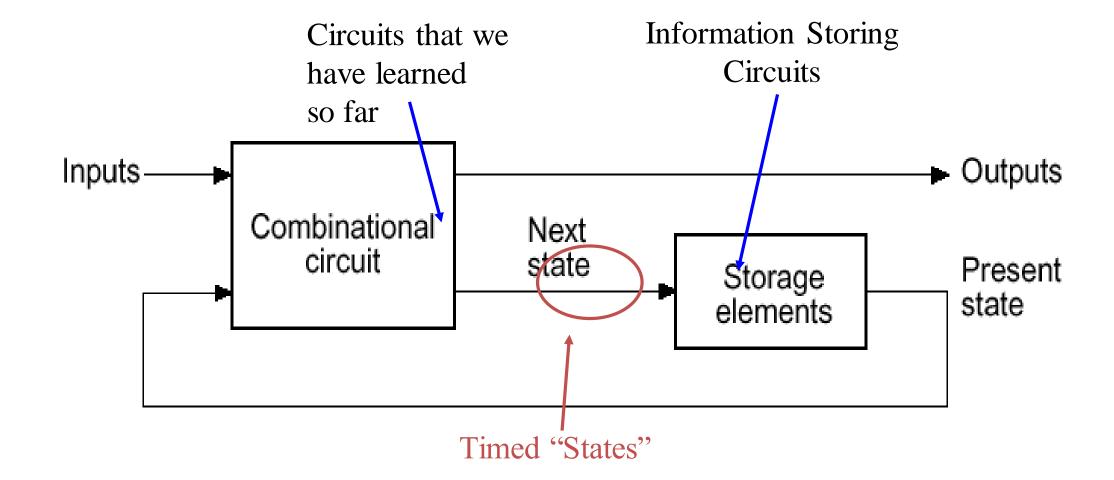

- Sequential Logic:

- -Output depends not only on current input but also on past input values, e.g., design a counter

- -Need some type of memory to remember the past input values

# Sequential Circuits

INSTITUTIONS

- Sequential Logic circuits remember past inputs and past circuit state.

- Outputs from the system are "fed back" as new inputs

- -With gate delay and wire delay

- The storage elements are circuits that are capable of storing binary information: memory.

# Combinational Logic Gates Memory Elements (Flip-Flops)

#### There are two types of sequential circuits:

- Synchronous sequential circuit: circuit output changes only at some discrete instants of time. This type of circuits achieves synchronization by using a timing signal called the clock.

- Asynchronous sequential circuit: circuit output can change at any time (clockless).

## Flip Flops

- ➤ In electronics a flip-flop or latch is a circuit that has two stable states and can be used to store state information —a bistable multivibrator.

- The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs.

- Flip-flops and latches are fundamental building blocks of digital electronics systems used in computers, communications, and many other types of systems.

- >Flip-flops and latches are used as data storage elements.

- A flip-flop is a device which stores a single bit(binary digit) of data; one of its two states represents a "one" and the other represents a "zero".

# Flip Flops

- >Flip flop is a sequential circuit

- ➤It samples its inputs and changes its outputs only at particular instants of time and not continuously.

- ➤ Flip flop is said to be edge sensitive or edge triggered rather than being level triggered like latches

#### **TYPES**

- SR Flip-Flop

- D Flip-Flop

- JK Flip-Flop

- T Flip-Flop

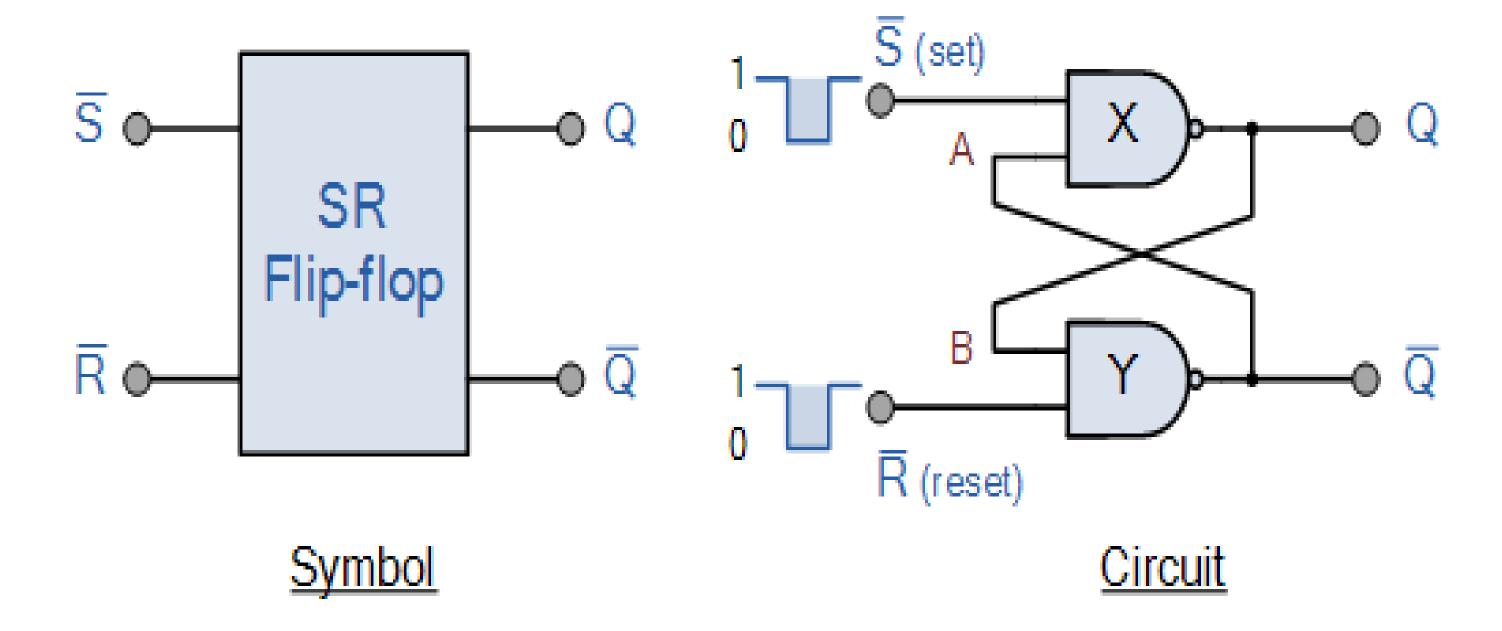

# **SR Flip Flop**

# **SR Flip Flop**

#### The Set State

- If the input R is at logic level "0" (R = 0) & S is at logic level "1" (S = 1) Its output Q must be at a logic level "1".

- $\triangleright$  Output  $\overline{Q}$  is also fed back to input "A"

- ➤ Both inputs to NAND gate X are at logic level "1"

- ➤ Its output Q must be at logic level "0".

- ➤ If the reset input R changes state, and goes HIGH to logic "1" with S remaining HIGH also at logic level "1"

- NAND gate Y inputs are now R = "1" and B = "0".

- ➤ Since one of its inputs is still at logic level "0" the output at Q still remains HIGH at logic level "1" and there is no change of state.

- Therefore, the flip-flop circuit is said to be "Latched" or "Set" with Q = "1" and Q = "0".

# **SR Flip Flop**

#### **Reset State**

- $\triangleright \overline{Q}$  is at logic level "0", its inverse output at Q is at logic level "1" Given by R = "1" and S = "0".

- As gate  $\overline{X}$  has one of its inputs at logic "0" its output  $\overline{Q}$  must equal logic level "1" Output  $\overline{Q}$  is fed back to input "B", so both inputs to NAND gate Y are at logic "1", therefore,  $\overline{\overline{Q}}$  = "0".

- ➤ If the set input, S now changes state to logic "1" with input R remaining at logic "1" ➤ output Q still remains LOW at logic level "0" and there is no change of state.

- Therefore, the flip-flop circuits "Reset" state has also been latched

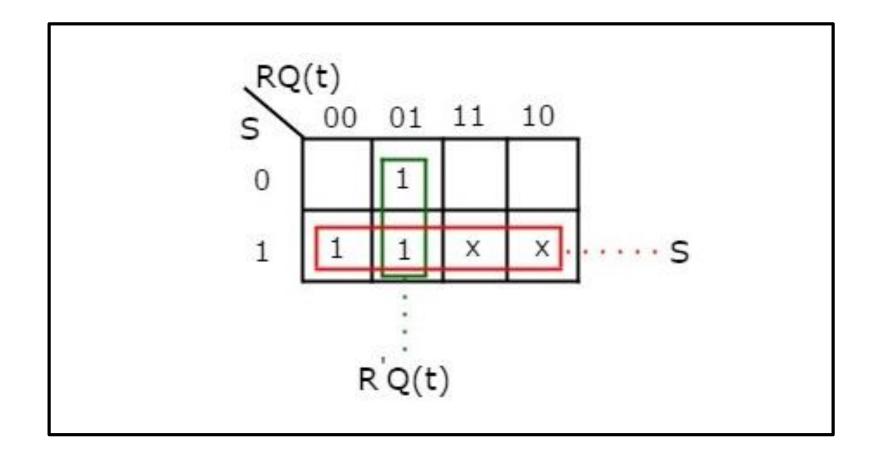

# **SR Flip Flop Truth Table**

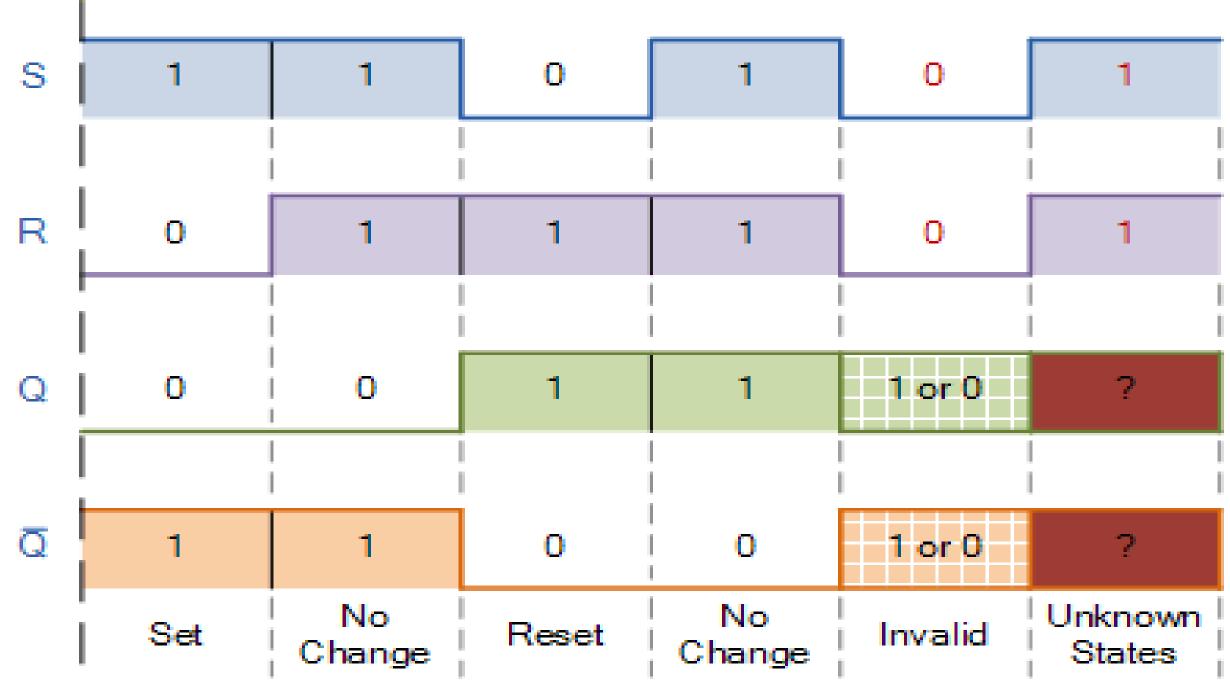

S-R flip flop behavior

Present state

The state of Q output at the time the input signals are applied.

Next state

The state of Q output after the flipflop has reacted to the input signals.

| State   | S | R | Q | Q | Description       |

|---------|---|---|---|---|-------------------|

| Set     | 1 | 0 | 0 | 1 | Set Q » 1         |

|         | 1 | 1 | 0 | 1 | no change         |

| Reset   | 0 | 1 | 1 | 0 | Reset Q » 0       |

|         | 1 | 1 | 1 | 0 | no change         |

| Invalid | 0 | 0 | 1 | 1 | Invalid Condition |

# **SR Flip Flop Truth Table**

- When both inputs S = "1" and R = "1" the outputs Q and Q can be at either logic level "1" or "0", depending upon the state of the inputs S or R BEFORE this input condition existed.

- Therefore the condition of S = R = "1" does not change the state of the outputs Q and Q.

- The input state of S = "0" and R = "0" is an undesirable or invalid condition

- The condition of S = R = "0" causes both outputs Q and Q to be HIGH together at logic level "1"

- The result is that the flip-flop looses control of Q and Q

- The flip-flop becomes unstable and switches to an unknown data state based upon the unbalance

$$Q(t+1) = S + R'Q(t)$$