#### SNS COLLEGE OF TECHNOLOGY

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

19ECB231 - DIGITAL ELECTRONICS

II YEAR/ III SEMESTER

UNIT 3 –SEQUENTIAL CIRCUITS

TOPIC - Design of Synchronous Sequential circuits: Up/Down counter

#### What is a Counter?

- >A digital circuit which is used for a counting pulses is known as counter.

- > Counter is the widest application of flip-flops.

- > It is a group of flip-flops with a clock signal applied.

## **Types of counters**

### Two Types

- Asynchronous Counter or Ripple Counter.

- 2. Synchronous Counter

### **Synchronous Counter**

- ➤ In synchronous counter, the clock input across all the flip-flops use the same source and create the same clock signal at the same time.

- A counter which is using the same clock signal from the same source at the same time is called **Synchronous counter**.

## **Asynchronous Counter**

- Depending upon the manner in which the fllp-flop are triggered, counters can be divided into two major categories.

- 1) Asynchronous counter (RIPPle/series counter).

- ii) synchronous counter (parallel counter).

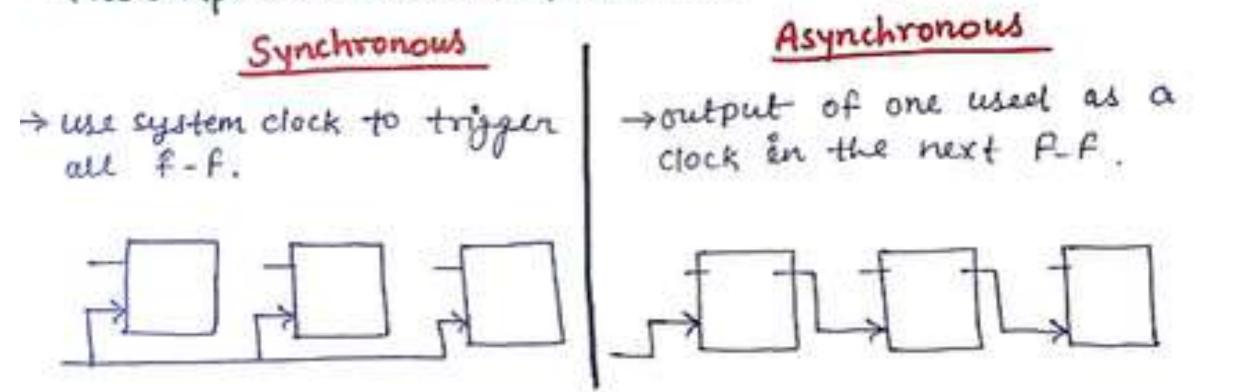

The comparison between synchronous and Asynchronous counter.

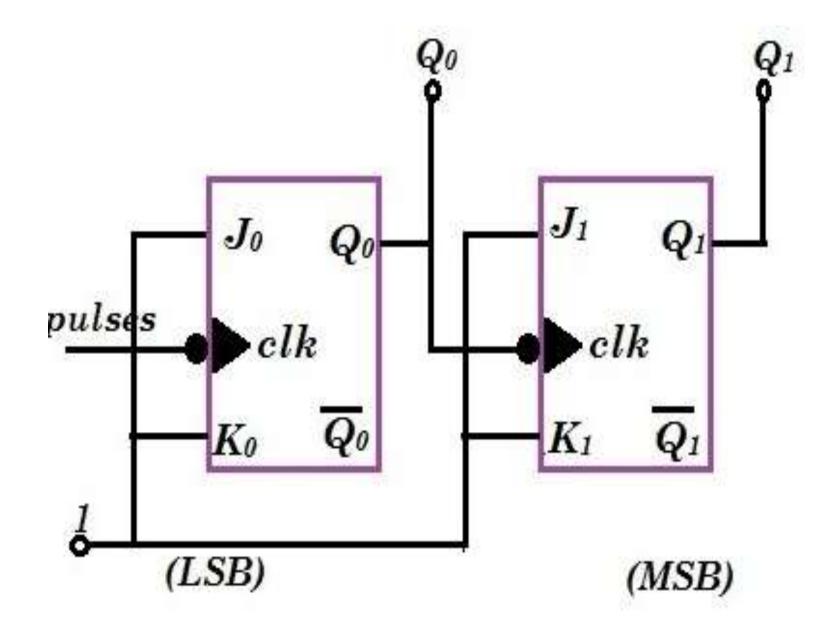

# **2-bit Asynchronous Counter**

| Synchronous Counter          | Asynchronous Counter                |  |

|------------------------------|-------------------------------------|--|

| All flip flops are triggered | Different clock is applied to       |  |

| with same clock.             | different flip flops.               |  |

| It is faster.                | It is lower                         |  |

| Design is complex.           | I Design <u>is</u> relatively easy. |  |

| Decoding errors not present. | Decoding errors present.            |  |

| Any required sequence can    | Only fixed sequence can be          |  |

| be designed                  | designed.                           |  |

## Up/Down Counters

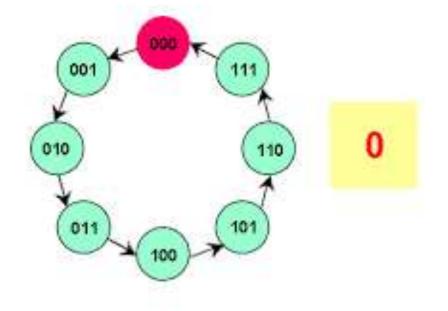

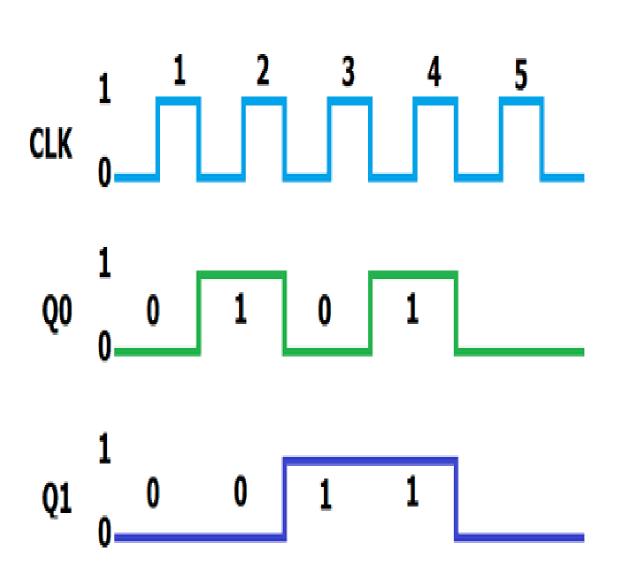

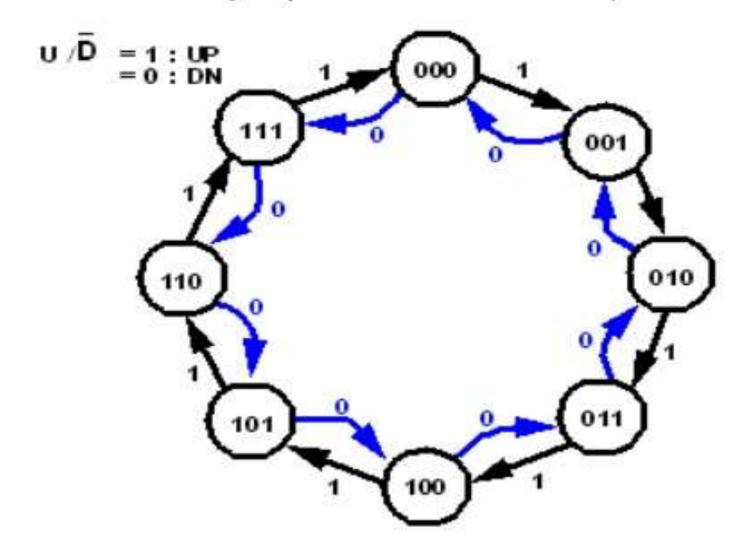

A 3-bit binary up/down counter (State diagram)

26

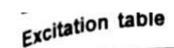

### State Table

| СР | UP | Qc | Q <sub>E</sub> | QA | DOWN               |

|----|----|----|----------------|----|--------------------|

| 0  | 6  | 0  | 0              | 0  | 5                  |

| 1  | >  | 0  | 0              | 1  | $  \prec  $        |

| 2  | >  | 0  | 1              | 0  | $  \prec  $        |

| 3  | >  | 0  | 1              | 1  | $ \langle    $     |

| 4  | >  | 1  | 0              | 0  | $ \langle \   \  $ |

| 5  | >  | 1  | 0              | 1  | $ \downarrow $     |

| 6  |    | 1  | 1              | 0  |                    |

| 7  |    | 1  | 1              | 1  | 2)                 |

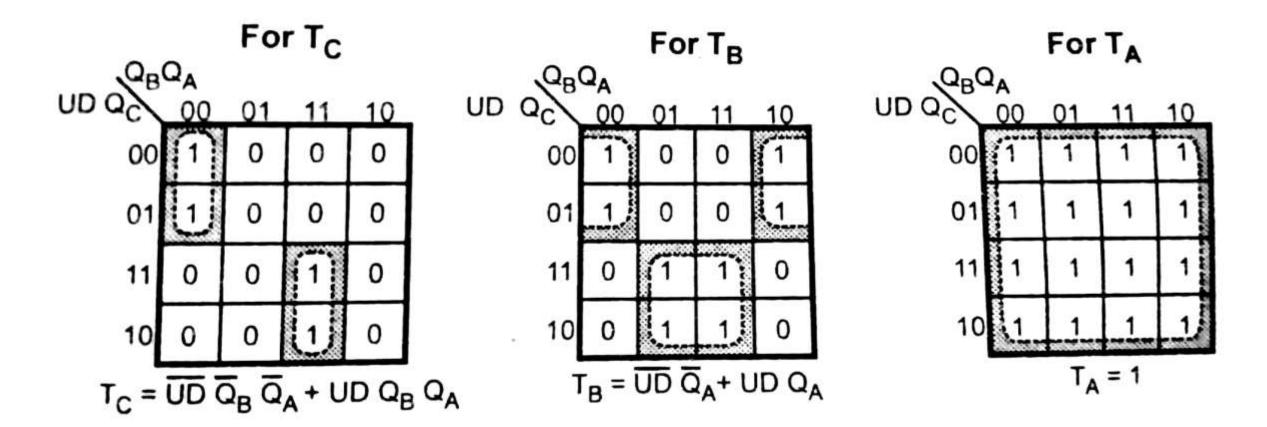

## K-map simplification

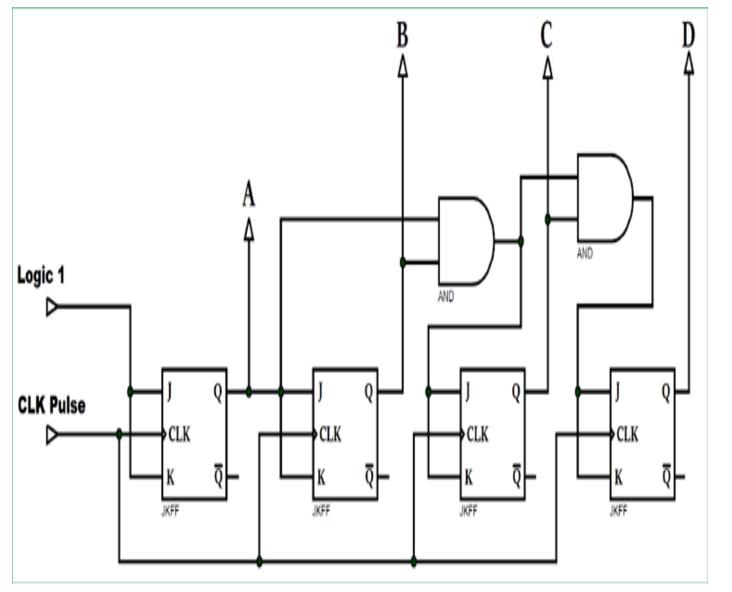

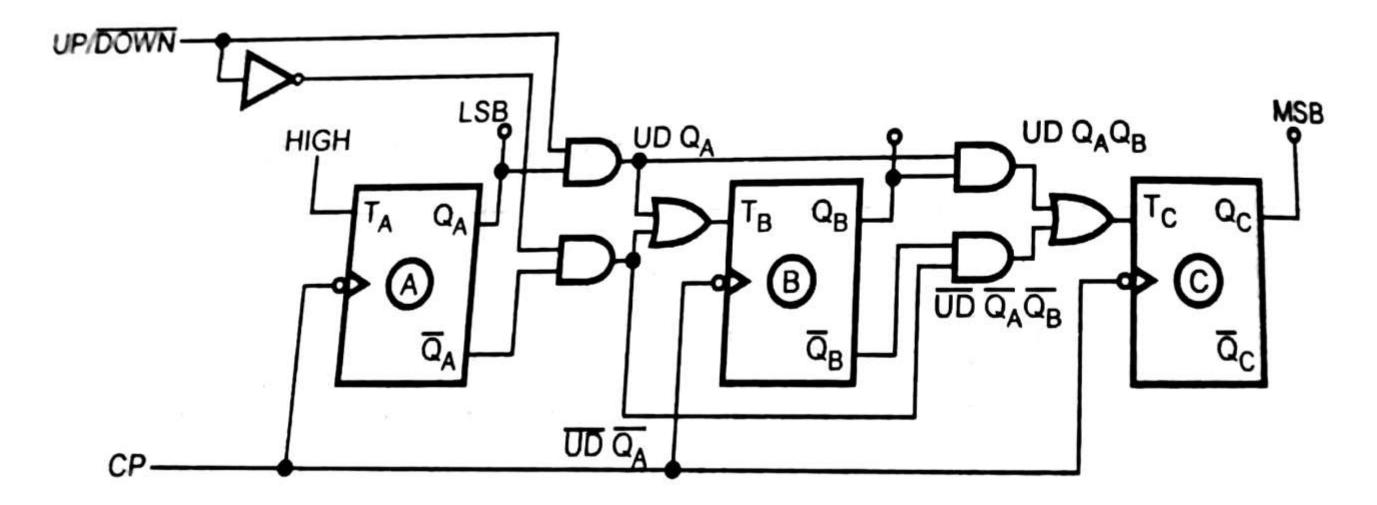

#### Logic Diagram

## **Applications of Counters**

Frequency counters

Digital clocks

# **Application for counter**

- Frequency counters

- Digital clock

- Time measurement

- A to D converter

- Frequency divider circuits

13

10/26/2023

#### **ASSESSMENTS**

- 1. How many natural states will there be in a 4-bit ripple counter?

- a) 4

- b) 8

- c) **16**

- d) 32

- 2. A ripple counter's speed is limited by the propagation delay of

- a) Each flip-flop

- b) All flip-flops and gates

- c) The flip-flops only with gates

- d) Only circuit gates.

- 3. Internal propagation delay of asynchronous counter is removed by

- a) Ripple counter

- b) Ring counter

- c) Modulus counter

- d) Synchronous counter

#### **ASSESSMENTS**

- 4. An asynchronous 4-bit binary down counter changes from count 2 to count 3. How many transitional states are required?

- a) 1

- b) 2

- c) 8

- d) **15**

- 5. A ripple counter's speed is limited by the propagation delay of

- a) Each flip-flop

- b) All flip-flops and gates

- c) The flip-flops only with gates

- d) Only circuit gates

### **THANK YOU**