### **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

**16EC231 – DIGITAL ELECTRONICS**

II YEAR/ III SEMESTER

UNIT 2 – COMBINATIONAL CIRCUITS

**TOPIC** - Multiplexer

#### What is a Multiplexer?

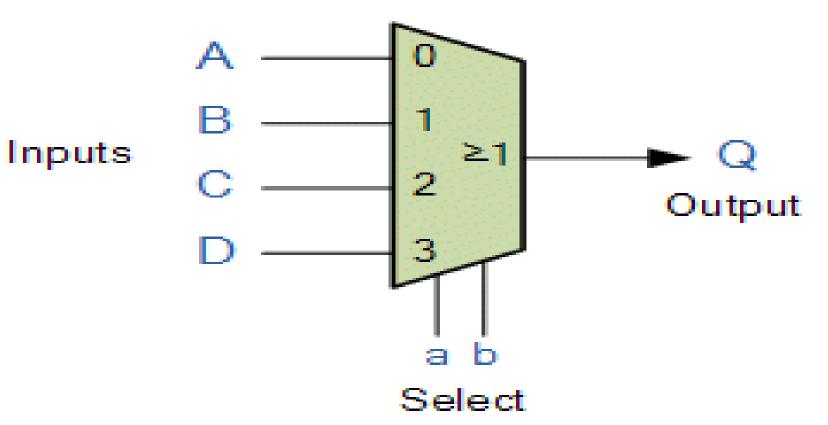

- Multiplexer is a combinational circuit that has maximum of 2n data inputs, 'n' selection lines and single output line.

- ➤One of these data inputs will be connected to the output based on the values of selection lines..

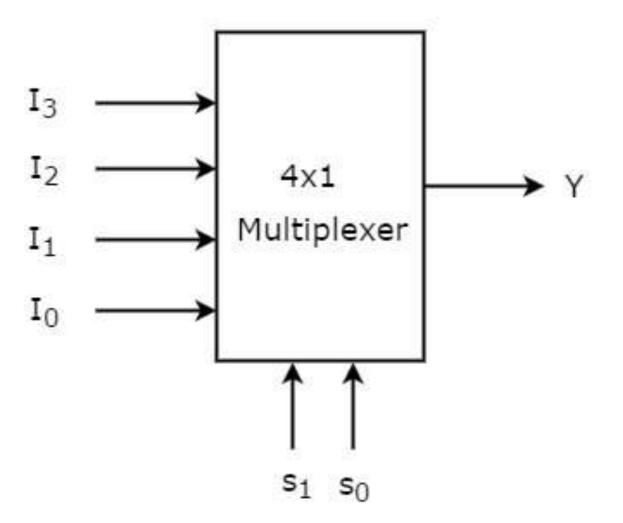

➤ 4x1 Multiplexer has four data inputs I3, I2, I1 & I0, two selection lines s1 & s0 and one output Y.

➤ One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines.

| Selection      | Output         |                |

|----------------|----------------|----------------|

| S <sub>1</sub> | S <sub>0</sub> | Υ              |

| 0              | 0              | I <sub>0</sub> |

| 0              | 1              | I <sub>1</sub> |

| 1              | 0              | I <sub>2</sub> |

| 1              | 1              | l <sub>3</sub> |

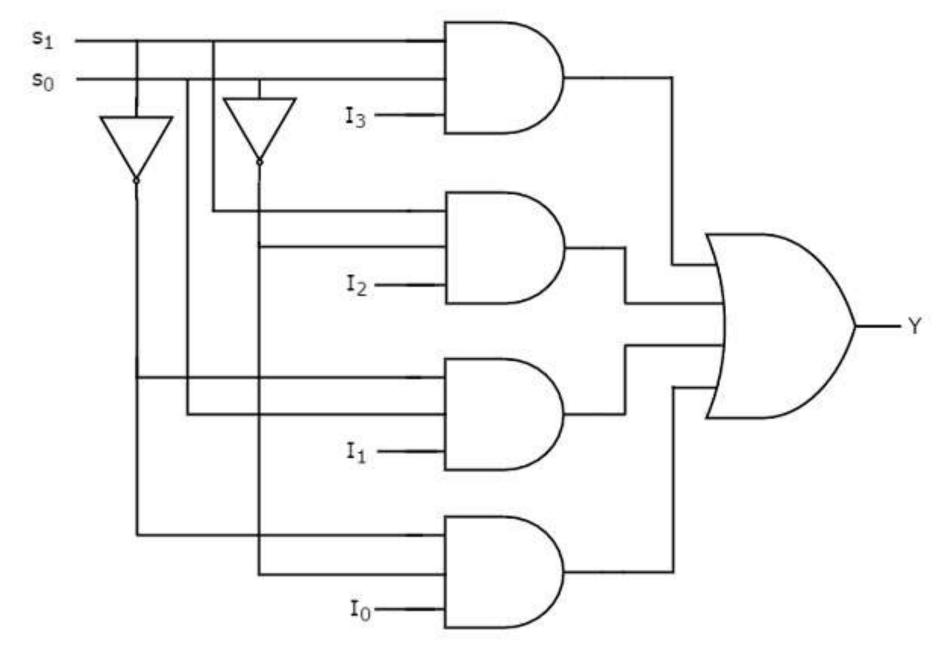

➤ We can implement this Boolean function using Inverters, AND gates & OR gate.

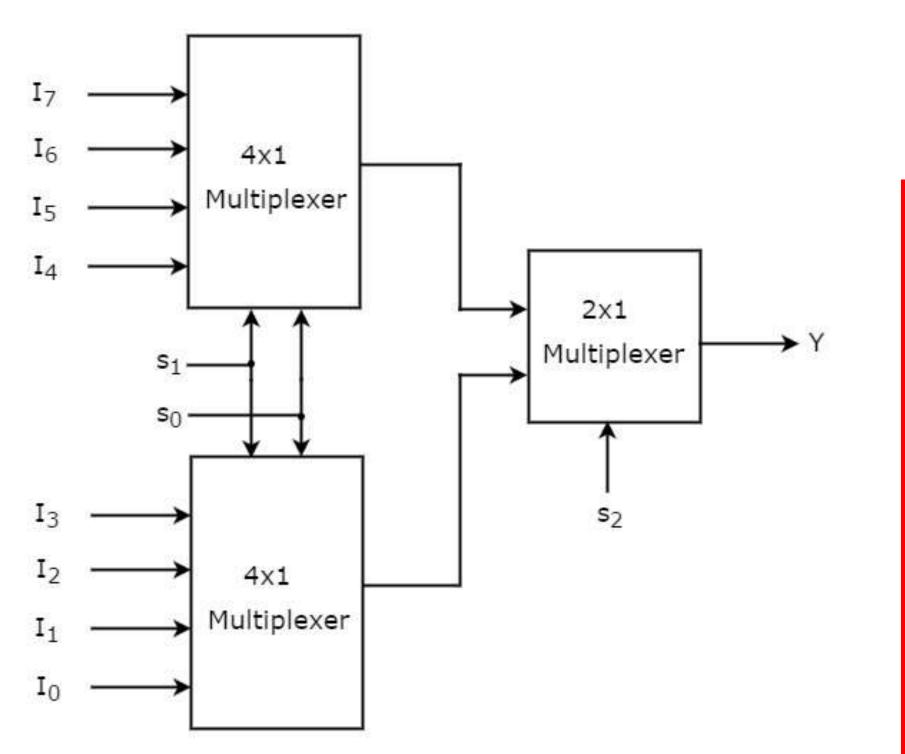

We require two 4x1

Multiplexers in first

stage in order to get

the 8 data inputs.

➤ Let the 8x1 Multiplexer has eight data inputs I7 to I0, three selection lines s2, s1 & s0 and one output Y

| Selection Inputs |                | Output         |                |

|------------------|----------------|----------------|----------------|

| S <sub>2</sub>   | S <sub>1</sub> | S <sub>0</sub> | Υ              |

| 0                | 0              | 0              | I <sub>0</sub> |

| 0                | 0              | 1              | I <sub>1</sub> |

| 0                | 1              | 0              | l <sub>2</sub> |

| 0                | 1              | 1              | l <sub>3</sub> |

| 1                | 0              | 0              | I <sub>4</sub> |

| 1                | 0              | 1              | l <sub>5</sub> |

| 1                | 1              | 0              | l <sub>6</sub> |

| 1                | 1              | 1              | I <sub>7</sub> |

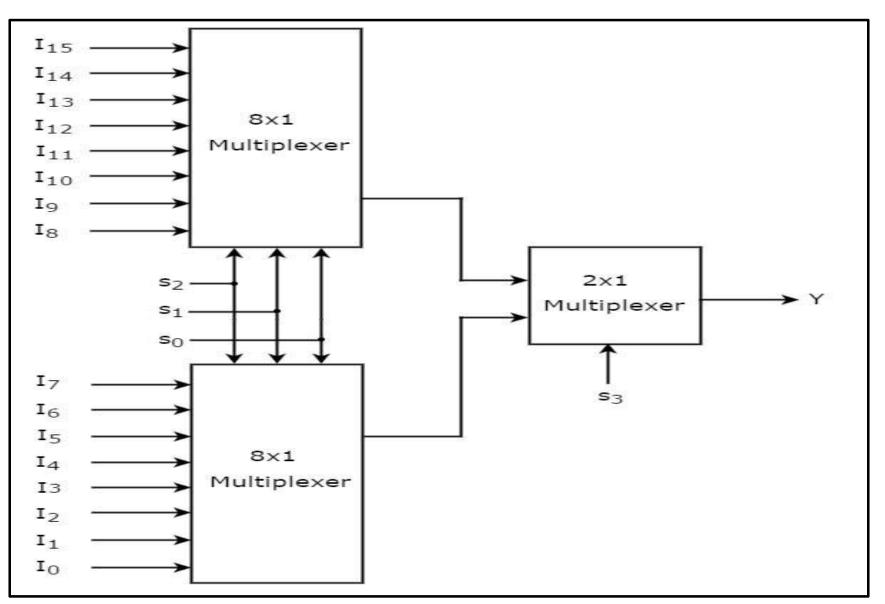

➤ We require two 8x1 Multiplexers in first stage in order to get the 16 data inputs.

| Selection Inputs      |                |                |                | Output         |

|-----------------------|----------------|----------------|----------------|----------------|

| <b>S</b> <sub>3</sub> | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Y              |

| 0                     | 0              | 0              | 0              | I <sub>0</sub> |

| 0                     | 0              | 0              | 1              | I <sub>1</sub> |

| 0                     | 0              | 1              | 0              | l <sub>2</sub> |

| 0                     | 0              | 1              | 1              | l <sub>3</sub> |

| 0                     | 1              | 0              | 0              | I <sub>4</sub> |

| 0                     | 1              | 0              | 1              | I <sub>5</sub> |

| 0                     | 1              | 1              | 0              | I <sub>6</sub> |

| 0                     | 1              | 1              | 1              | I <sub>7</sub> |

| 1                     | 0              | 0              | 0              | I <sub>8</sub> |

| 1 | 0 | 0 | 1 | lg              |

|---|---|---|---|-----------------|

| 1 | 0 | 1 | 0 | I <sub>10</sub> |

| 1 | 0 | 1 | 1 | I <sub>11</sub> |

| 1 | 1 | 0 | 0 | I <sub>12</sub> |

| 1 | 1 | 0 | 1 | I <sub>13</sub> |

| 1 | 1 | 1 | 0 | I <sub>14</sub> |

| 1 | 1 | 1 | 1 | l <sub>15</sub> |

#### **Advantages**

#### Advantages:

- 1) It reduces number of wires.

- 2) It reduces circuit complexity and cost.

- 3) We can implement many combination circuits using MUX.

- 4) It does not need K maps and simplification.

#### **Disadvantages**

#### Disadvantages:

- 1) Added delays in switching ports.

- 2) Limitations on which ports can be used simultaneously.

- 3) Added firmware complexity to handle switching ports.

- 4) Added delays in I/O signals propagating through the multiplexer.

- 5) Extra I/O ports required to control the multiplexer.

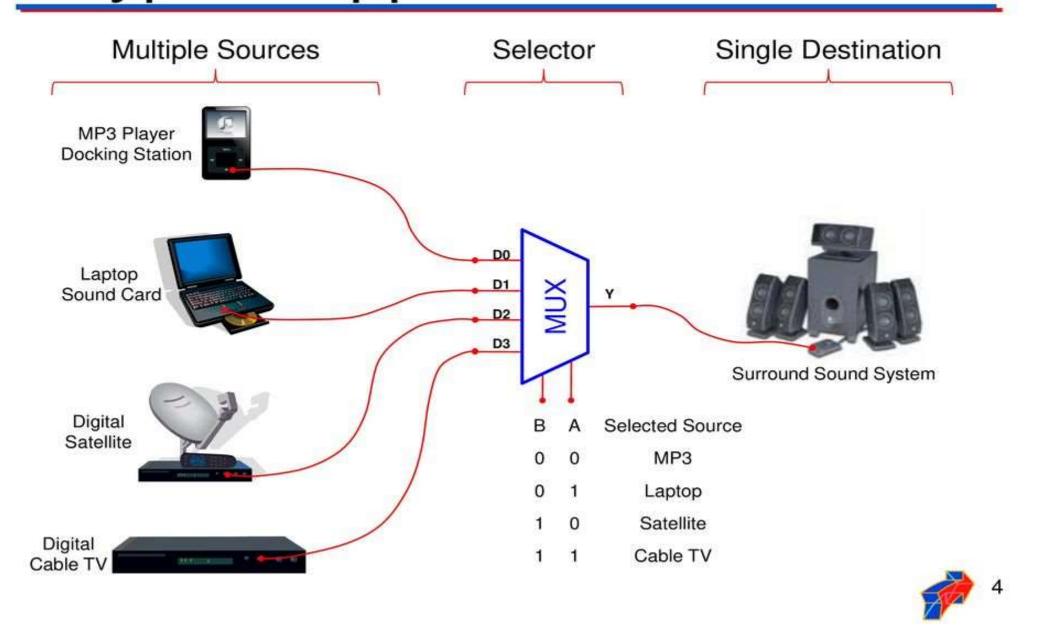

# Typical Application of a MUX

#### **ASSESSMENTS**

- 1.What is Multiplexer?

- 2.Design 8:1 Multiplexer.

- 3.List the applications of multiplexer.

## **THANK YOU**