GATE ECE 2016 Set 1

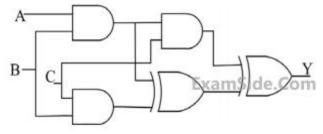

1. The output of the combinational circuit given below is

| А      | - |  |  |

|--------|---|--|--|

| A+B+C  |   |  |  |

| В      |   |  |  |

| A(B+C) |   |  |  |

| С      |   |  |  |

| B(C+A) |   |  |  |

| D      |   |  |  |

| C(A+B) |   |  |  |

#### GATE ECE 2015 Set 3

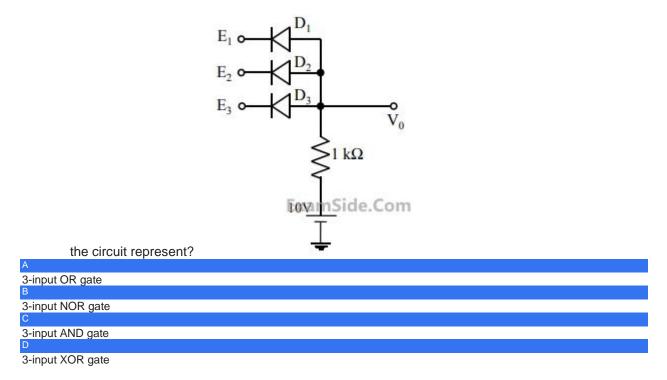

In the circuit shown, diodes D1D1 ,D2D2 and D3D3 are ideal, and the inputs E1E1 , E2E2 and E3E3 are "0 V" for logic '0' and "10 V" for logic '1'. What logic gate does

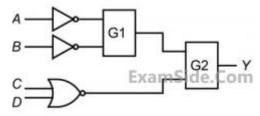

## 3. GATE ECE 2015 Set 2

In the figure shown, the output  $_{\odot}$  is required to be  $_{\odot}$  Y=AB+  $^{--}CC^{--}DD^{-}$ . The gates G1 and G2 must be,

respectively,

| А         |  |  |  |

|-----------|--|--|--|

| NOR, OR   |  |  |  |

| В         |  |  |  |

| OR, NAND  |  |  |  |

| С         |  |  |  |

| NAND, OR  |  |  |  |

| D         |  |  |  |

| AND, NAND |  |  |  |

# GATE ECE 2013

4. A bulb in a staircase has two switches, one switch being at the ground floor and the other one at the first floor. The bulb can be turned ON and also can be turned OFF by any one of the switches irrespective of the state of the other switch. The logic of switching of the bulb resembles.

| an AND gate |  |  |  |

|-------------|--|--|--|

| В           |  |  |  |

| an OR gate  |  |  |  |

| С           |  |  |  |

| an XOR gate |  |  |  |

| D           |  |  |  |

| a NAND gate |  |  |  |

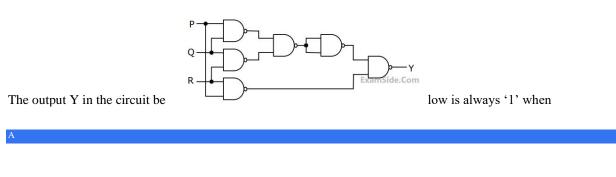

## 5. GATE ECE 2011

two or more of the inputs P, Q, R are '0'

two or more of the inputs P, Q, R are '1

any odd number of the inputs P, Q, R is '0'

any odd number of the inputs P, Q, R is '1'

## 6. GATE ECE 2010

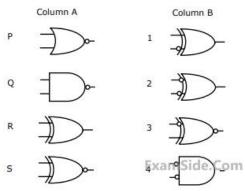

Match the logic gates in column A with their equivalents in column B.

|                    | A |  |

|--------------------|---|--|

| P-2, Q-4, R-1, S-3 |   |  |

|                    | В |  |

| P-4, Q-2, R-1, S-3 |   |  |

|                    | С |  |

| P-2, Q-4, R-3, S-1 |   |  |

|                    | D |  |

| P-4, Q-2, R-3, S-1 |   |  |

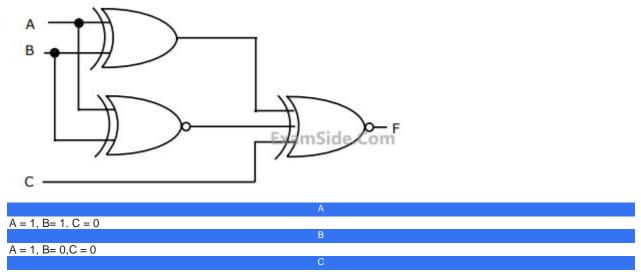

7. For the output F to be 1 in the logic circuit shown, the input combination should be

**GATE QUESTION PAPER**

A = 0, B= 1. C = 0 A = 0, B= 0, C = 1

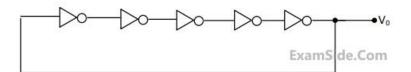

#### 8. GATE ECE 2001

For the ring oscillator shown in the figure, the propagation delay of each inverter is 100 pico sec. What is the fundamental frequency of the oscillator output?

# 9. GATE ECE 2017 Set 1

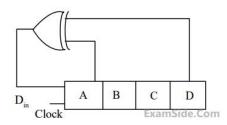

A 4-bit shift register circuit configured for right-shift operation

is  $D_{in} \rightarrow A, A \rightarrow B, B \rightarrow C, C \rightarrow D, Din \rightarrow A, A \rightarrow B, B \rightarrow C, C \rightarrow D$ , is shown. If the present state of the shift register is ABCD = 1101, the number of clock cycles required to reach the state ABCD = 1111 is

#### GATE QUESTION PAPER

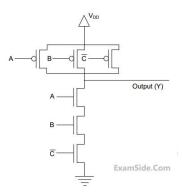

# 10. GATE ECE 2014 Set 4

The output (Y) of the circuit shown in the figure is

--A+--B+--CA-+B-+C-

A+--B--.C+A.--CA+B-.C-+A.C-

<sup>--</sup>A+B+--CA<sup>-</sup>+B+C<sup>-</sup> D

A.B.--CA.B.C<sup>-</sup>