## SNS COLLEGE OF TECHNOLOGY

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

## DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

19ECB302-VLSI DESIGN

III YEAR/ V SEMESTER

UNIT 2 -COMBINATIONAL LOGIC CIRCUITS

TOPIC 4 & 5 - Pseudo nMOS logic & Domino Logic

8/4/2023

- Pseudo NMOS logic

- Comparison of 3 Gates

- Pseudo nMOS Design & power calculation

- Dynamic Logic

- The Foot, Logical Effort, Monotonocity problem

- Activity

- Domino Gates

- -Optimization ,Dual Rail

- Assessment

- Summary

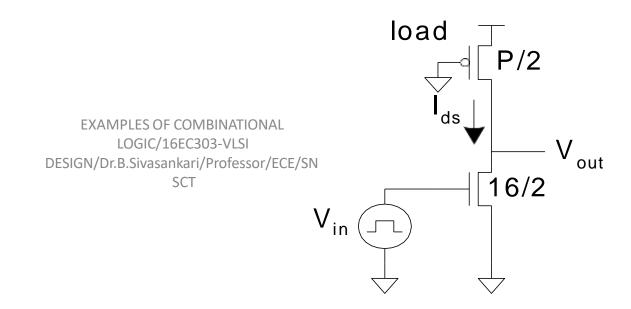

## Pseudo NMOS logic

- The inverter that uses a p-device pull-up or load that has its gate permanently ground.

- An n-device pull-down or driver is driven with the input signal. This roughly equivalent to use of a depletion load is **Nmos** technology and is thus called '**Pseudo-NMOS**'.

- This circuit is used in a variety of CMOS **logic** circuits

# Pseudo NMOS logic – Advantage and Disadvantage

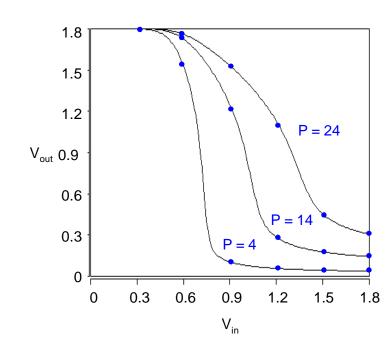

- The **advantage** of pseudo-NMOS logic are its high **speed** (especially, in large-fanin NOR gates) and low transistor count.

- The **Disadvantage** On the negative side is the static **power** consumption of the pull-up transistor as well as the reduced output voltage swing and gain, which makes the gate more susceptible to noise.

- Pseudo NMOS logic

- Comparison of 3 Gates

- Pseudo nMOS Design & power calculation

- Dynamic Logic

- The Foot, Logical Effort, Monotonocity problem

- Activity

- Domino Gates

- -Optimization ,Dual Rail

- Assessment

- Summary

- Pseudo NMOS logic

- Comparison of 3 Gates

- Pseudo nMOS Design & power calculation

- Dynamic Logic

- The Foot, Logical Effort, Monotonocity problem

- Activity

- Domino Gates

- -Optimization ,Dual Rail

- Assessment

- Summary

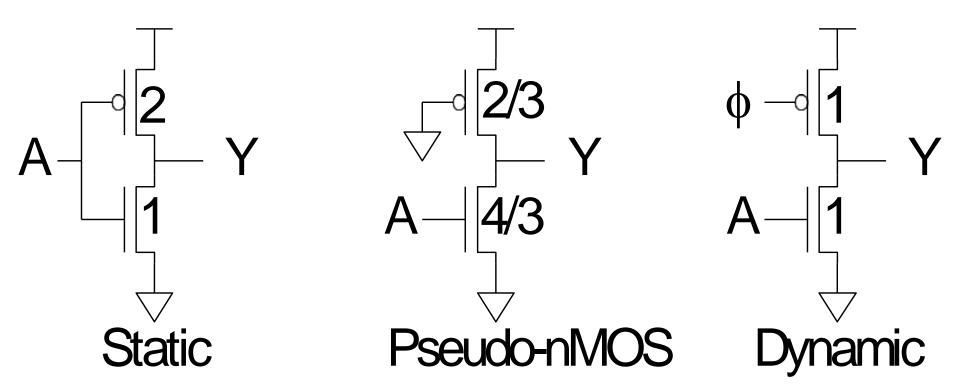

#### Pseudo-nMOS

In the old days, nMOS processes had no pMOS

Instead, use pull-up transistor that is always ON

In CMOS, use a pMOS that is always ON

Ratio issue

Make pMOS about ¼ effective strength of pull

down network

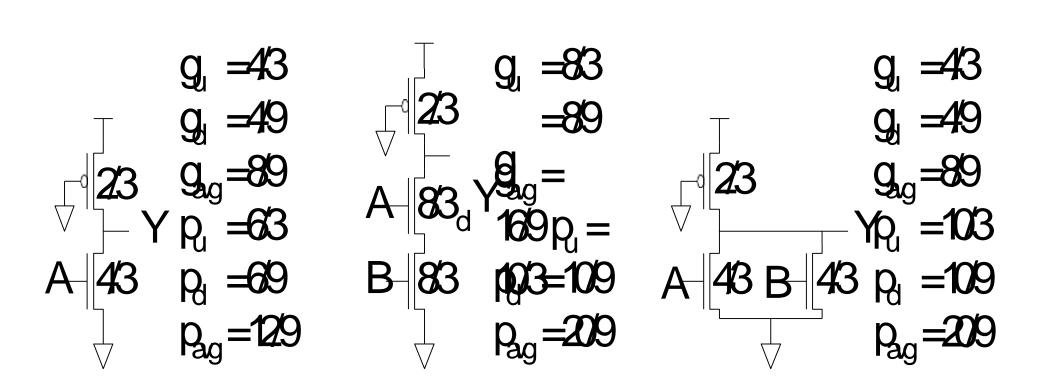

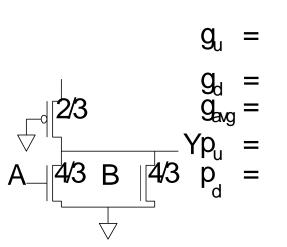

## **Pseudo-nMOS Gates**

- Design for unit current on output to compare with unit inverter.

- pMOS fights nMOS

Inverter

$$g_{u} = g_{d} = g_{avg} = g_{avg} = g_{d} =$$

NAND2

NOR2

# Comparison

heter MND2 NDR

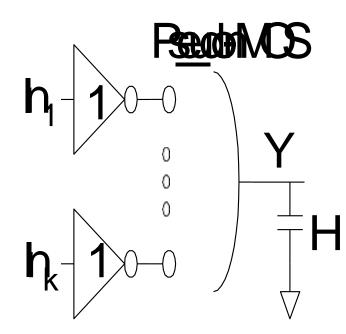

## Pseudo-nMOS Design

• Ex: Design a k-input AND gate using pseudonMOS. Estimate the delay driving a fanout of H

•

$$G = 1 * 8/9 = 8/9$$

•

$$P = 1 + (4+8k)/9 = (8k+13)/9$$

•

$$N = 2$$

$$\frac{4\sqrt{2H}}{3} + \frac{8k+13}{9}$$

•

$$D = NF^{1/N} + P =$$

#### Pseudo-nMOS Power

Pseudo-nMOS draws power whenever Y = 0Called static power  $P = I \cdot V_{DD}$ A few mA/gate \* 1M gates would be a problem This is why nMOS went extinct! Use pseudo-nMOS sparingly for wide NORs Turn off pMOS when not in use

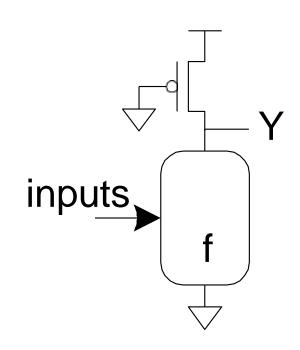

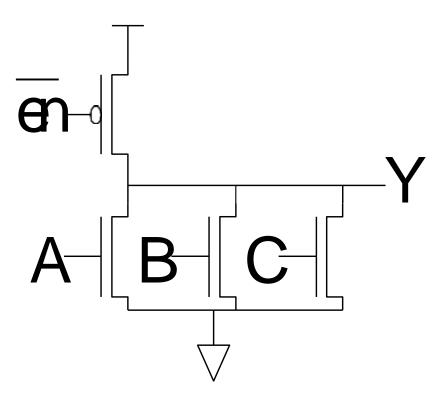

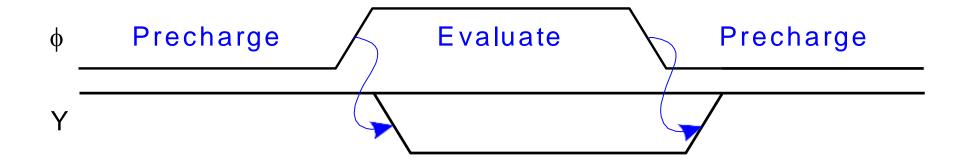

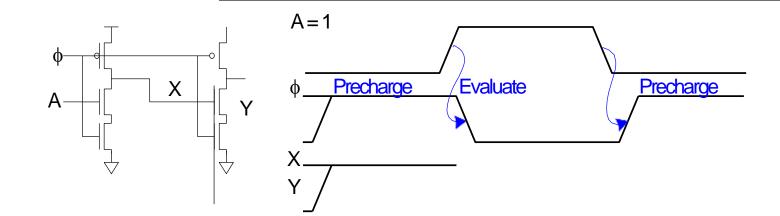

# **Dynamic Logic**

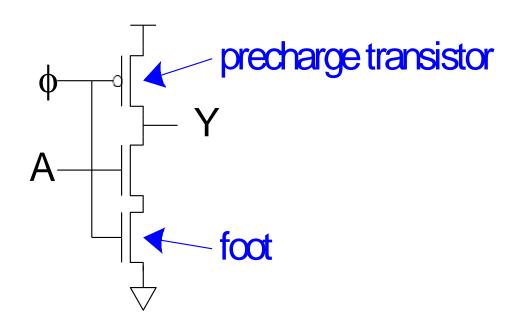

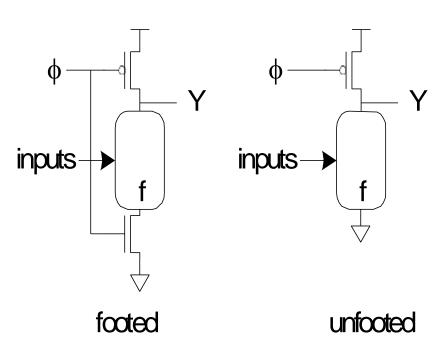

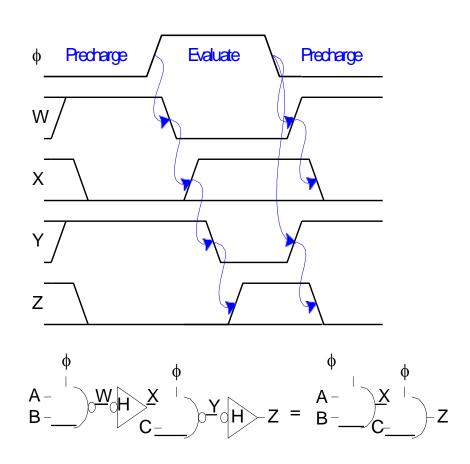

Dynamic gates uses a clocked pMOS pullup

Two modes: precharge and evaluate

## **The Foot**

What if pull down network is ON during precharge?

Use series evaluation transistor to prevent fight.

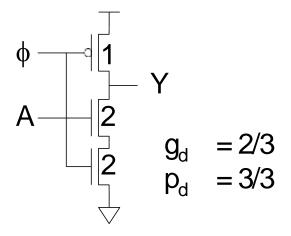

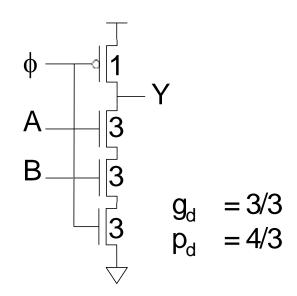

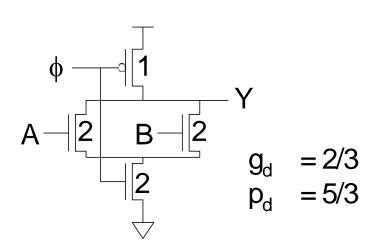

# **Logical Effort**

Inverter

NAND2

NOR2

unfooted

$$\begin{array}{ccc}

& & \downarrow \\

& \downarrow$$

$$\phi \rightarrow \boxed{1}$$

$$A. \rightarrow \boxed{2}$$

$$B. \rightarrow \boxed{2}$$

$$g_d = 2/3$$

$$p_d = 3/3$$

footed

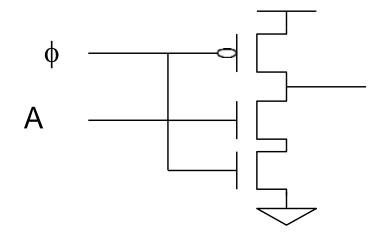

# **Monotonicity Problems**

Dynamic gates require monotonically rising inputs during evaluation

0 -> 0

0 -> 1

1 -> 1

But not 1 -> 0

## **Monotonicity Woes**

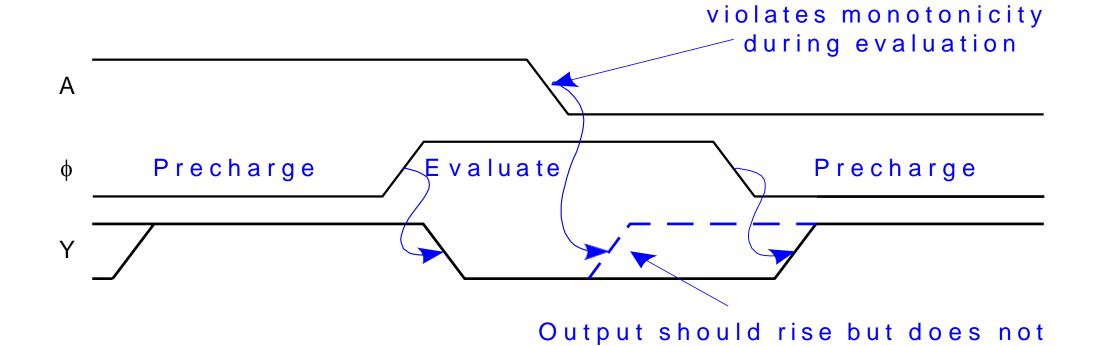

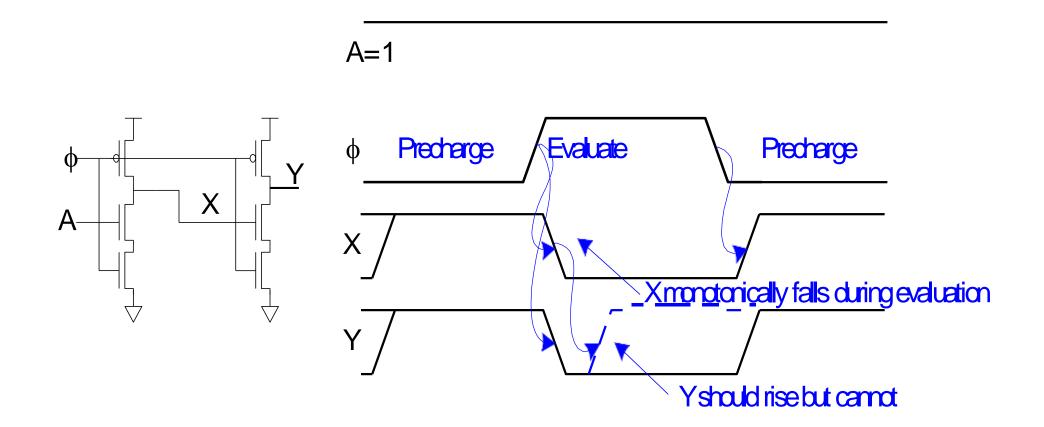

But dynamic gates produce monotonically falling outputs during evaluation Illegal for one dynamic gate to drive another!

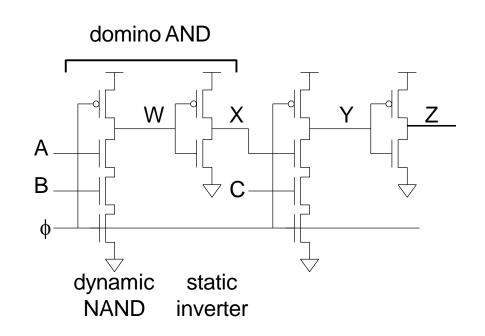

#### **Domino Gates**

Follow dynamic stage with inverting static gate Dynamic / static pair is called domino gate Produces monotonic outputs

## **Domino Optimizations**

- •Each domino gate triggers next one, like a string of dominos toppling over

- •Gates evaluate sequentially but precharge in parallel

- •Thus evaluation is more critical than precharge

- •HI-skewed static stages can perform logic

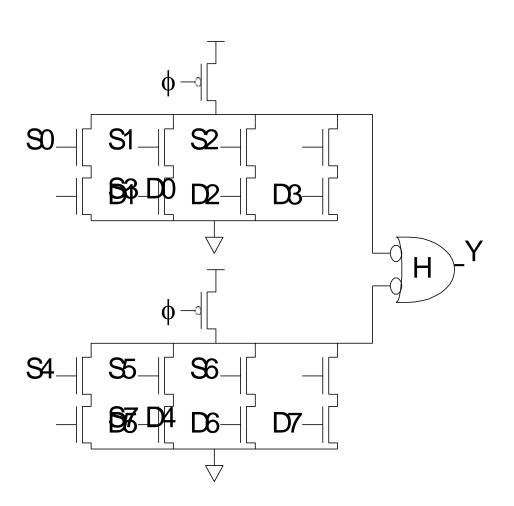

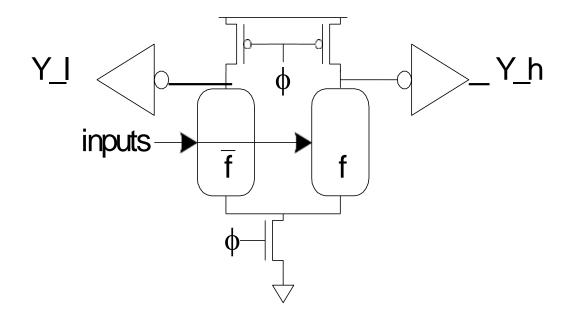

#### **Dual-Rail Domino**

- •Domino only performs no inverting functions: AND, OR but not NAND, NOR, or XOR

- Dual-rail domino solves this problem

Takes true and complementary inputs

Produces true and complementary outputs

| sig_h | sig_l | Meaning    |

|-------|-------|------------|

| 0     | 0     | Precharged |

| 0     | 1     | '0'        |

| 1     | 0     | <b>'1'</b> |

| 1     | 1     | invalid    |

## Assessment-Fill up the blanks

Inverter

NOR2

$$g_{u} = g_{d} = g_{d} = g_{d} = g_{avg} = g_{avg} = g_{d} =$$

$$g_{u} = \frac{2/3}{2/3} \quad g_{d} = \frac{2/3}{3} \quad g_{d} = \frac{8/3}{3} \quad p_{u} = \frac{8/3}{3} \quad p_{d} = \frac{8/3}{3} \quad p_$$

$$p_{avg} =$$

| sig_<br>h | sig_l | Meaning | • |  |

|-----------|-------|---------|---|--|

|           |       |         |   |  |

|           |       |         |   |  |

|           |       |         |   |  |

|           | 0     |         |   |  |

| 0         |       |         |   |  |

| 0         | 1     |         |   |  |

| 1         | 0     |         |   |  |

|           |       |         |   |  |

| l 1       | 1 1   |         |   |  |

## **THANK YOU**