# **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (Po), Coimbatore – 641 107

#### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### **DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING**

#### COURSE NAME :19IT301 COMPUTER ORGANIZATION AND ARCHITECTURE II YEAR /III SEMESTER

#### Unit 1- BASIC STRUCTURE OF COMPUTERS

Topic 7 : Instruction and Instruction sequencing

# Instruction and Instruction sequencing

A computer must have instructions capable of performing four types of operations:

- 1. Data transfers between the memory and the processor registers

- 2. Arithmetic and logic operations on data

- Program sequencing and control 3.

- I/O transfers 4.

# Instruction and Instruction sequencing-**Register Transfer Notation (RTN)**

✓ Identify a location by a symbolic name standing for its hardware binary address (LOC, RO,...) Contents of a location are denoted by placing square brackets around the name of the location  $R1 \leftarrow [LOC]$  $R3 \leftarrow [R1]+[R2])$

Instructions and instruction sequencing/Computer organization and architecture/Dr.K.Periyakaruppan/CSE/SNSCE

# Instruction and Instruction sequencing-Assembly language notation

Represent machine instructions and programs. Move LOC,  $R1 = R1 \leftarrow [LOC]$ Add R1, R2, R3 = R3  $\leftarrow$  [R1]+[R2]

Instructions and instruction sequencing/Computer organization and architecture/Dr.K.Periyakaruppan/CSE/SNSCE

# Instruction and Instruction sequencing-Basic Instruction types

| Three-Add                 | ress Instru | ictions                          |  |  |

|---------------------------|-------------|----------------------------------|--|--|

| Add                       | A,B,C       | C ←[A]+[B]                       |  |  |

| Two-Address Instructions  |             |                                  |  |  |

| Add                       | B,D         | $D \leftarrow [B]+[D]$           |  |  |

| One-Address Instructions  |             |                                  |  |  |

| Add                       | В           | $AC \leftarrow [AC] + [B]$       |  |  |

| Load                      | A           |                                  |  |  |

| Store                     | С           |                                  |  |  |

| Zero-Address Instructions |             |                                  |  |  |

| Add                       |             | $TOS \leftarrow TOS + (TOS - 1)$ |  |  |

# Instruction and Instruction sequencing-**Basic instruction types**

Example: Evaluate C= A+ B Both the operands are in registers Move A,R0 Move B,R1 Add RO,R1 Move R1,C

Example: One operand in the memory and another one in the register

- 1. Move A, R1

- 2. Add B,R1

- 3. Move R1,C

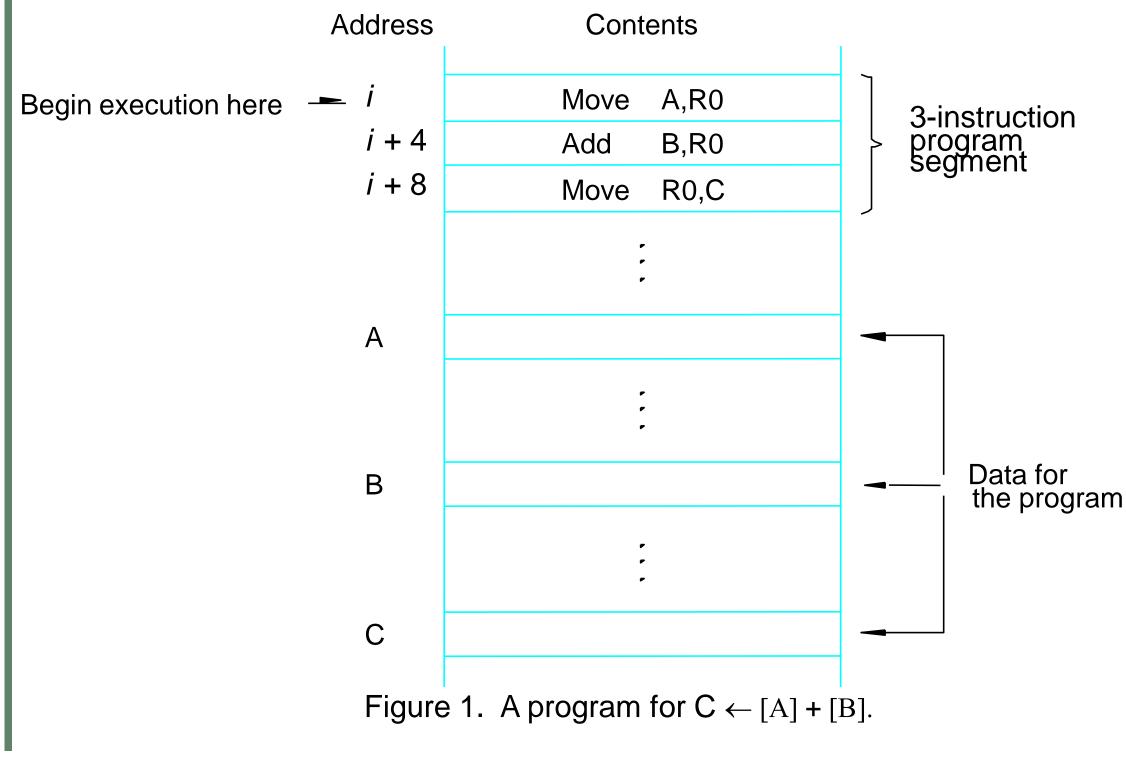

# Instruction Execution and Straight-Line Sequencing

Instructions and instruction sequencing/Computer organization and architecture/Dr.K.Periyakaruppan/CSE/SNSCE

Assumptions:

- One memory operand per instruction

- 32-bit word length

- Memory is byte addressable

- Full memory address can be directly specified in a single-word instruction

Two-phase procedure -Instruction fetch -Instruction execute

Page 43

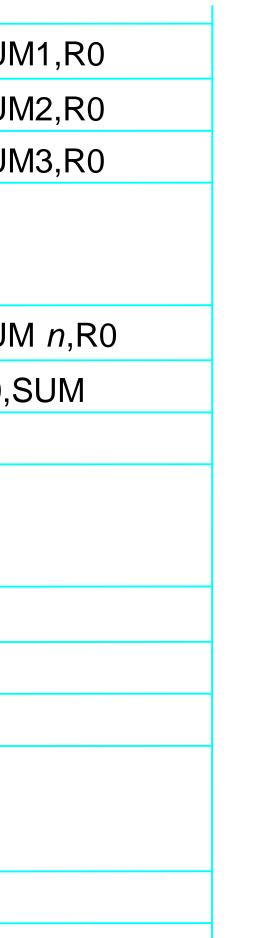

| i                 | Move          | NUN    |

|-------------------|---------------|--------|

| <i>i</i> + 4      | Add           | NUN    |

| <i>i</i> + 8      | Add           | NUN    |

|                   |               | •<br>• |

| i + 4n- 4         | Add           | NUN    |

| i + 4n            | Move          | R0,\$  |

|                   |               |        |

|                   |               | •      |

|                   |               | •      |

| SUM               |               | •      |

| NUM1              |               |        |

| NUM2              |               |        |

|                   |               | •      |

|                   |               | •      |

| NUM <i>n</i>      |               | -      |

| Figure 2. A strai | ight-line pro | ogram  |

|                   |               |        |

Instructions and instruction sequencing/Computer organization and architecture/Dr.K.Periyakaruppan/CSE/SNSCE

n for adding *n* numbers.

architecture/Dr.K.Periyakaruppan/CSE/SNSCE

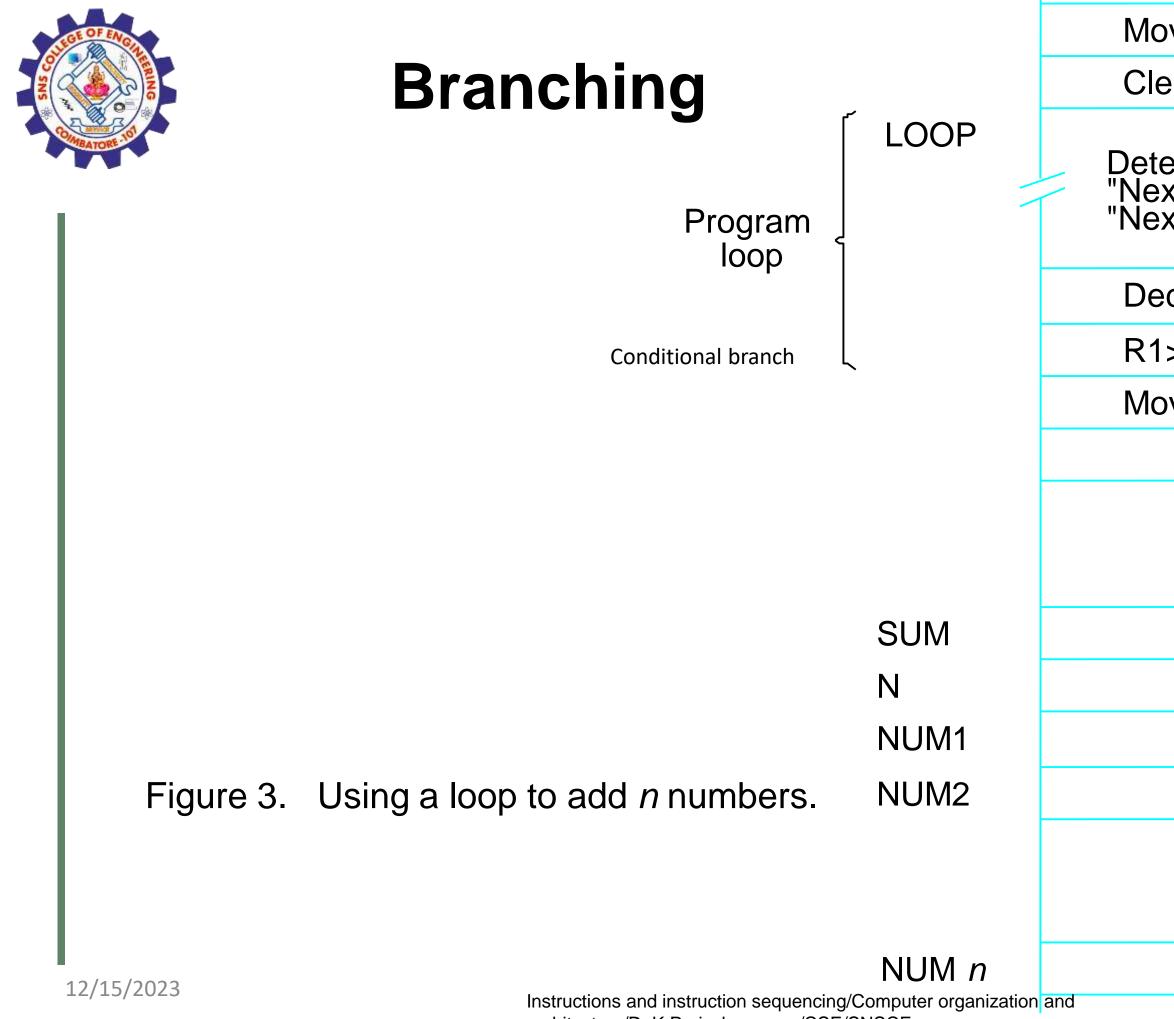

|                                        | 1                           |  |

|----------------------------------------|-----------------------------|--|

| ove                                    | N,R1                        |  |

| ear                                    | R0                          |  |

| ermine add<br>xt" number<br>xt" number | ress of<br>and add<br>to R0 |  |

| ecrement                               | R1                          |  |

| >0                                     | LOOP                        |  |

| ove                                    | R0,SUM                      |  |

|                                        |                             |  |

| •                                      |                             |  |

| n                                      |                             |  |

|                                        |                             |  |

| •<br>•                                 |                             |  |

|                                        |                             |  |

|                                        |                             |  |

## Instruction and Instruction sequencing

#### **Condition code flags**

Condition code register / status register N (negative) Z (zero) V (overflow) C (carry) Different instructions affect different flags

#### Assessment

a). What are the 4 types of operations?

b) Give the purpose of the following:

- 1.Register transfer notation\_\_\_\_\_

- 2. Assembly language notation \_\_\_\_\_

- 3.Condition code flags \_\_\_\_\_

### Reference

1. Carl Hamacher, Zvonko Vranesic and Safwat Zaky, "Computer Organization", McGraw-Hill, 6<sup>th</sup> Edition 2012.

Instructions and instruction sequencing/Computer organization and architecture/Dr.K.Periyakaruppan/CSE/SNSCE