# **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (Po), Coimbatore – 641 107

### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

### **DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING**

### **COURSE NAME : 19IT301 COMPUTER ORGANIZATION AND** ARCHITECTURE II YEAR /III SEMESTER

### Unit 1- BASIC STRUCTURE OF COMPUTERS

Topic 3 : Bus structures **Topic 4: Performance**

### Bus structures

>A group of lines that serves as a connecting path for several devices is called a *bus*.

- >Address bus

- ➢ Data bus

- ➢Control bus

### **Bus structures**

- 1. Since the bus can be used for only one transfer at a time, only two units can actively use the bus at any given time.

- 2. Bus control lines are used to arbitrate multiple requests for use of one bus.

- 3. Single bus structure is

- Low cost

- Very flexible for attaching peripheral devices  $\checkmark$

- 4. Multiple bus structure certainly increases the performance but also increases the cost significantly.

### bus structures

✓ Different devices have different transfer/operate speed.  $\checkmark$  If the speed of bus is bounded by the slowest device connected to it, the efficiency will be very low. How to solve this?

- $\checkmark$  A common approach use buffers.

- The instructions from the processor at once are loaded into these buffers and then the complete transfer of data to the slow speed device.

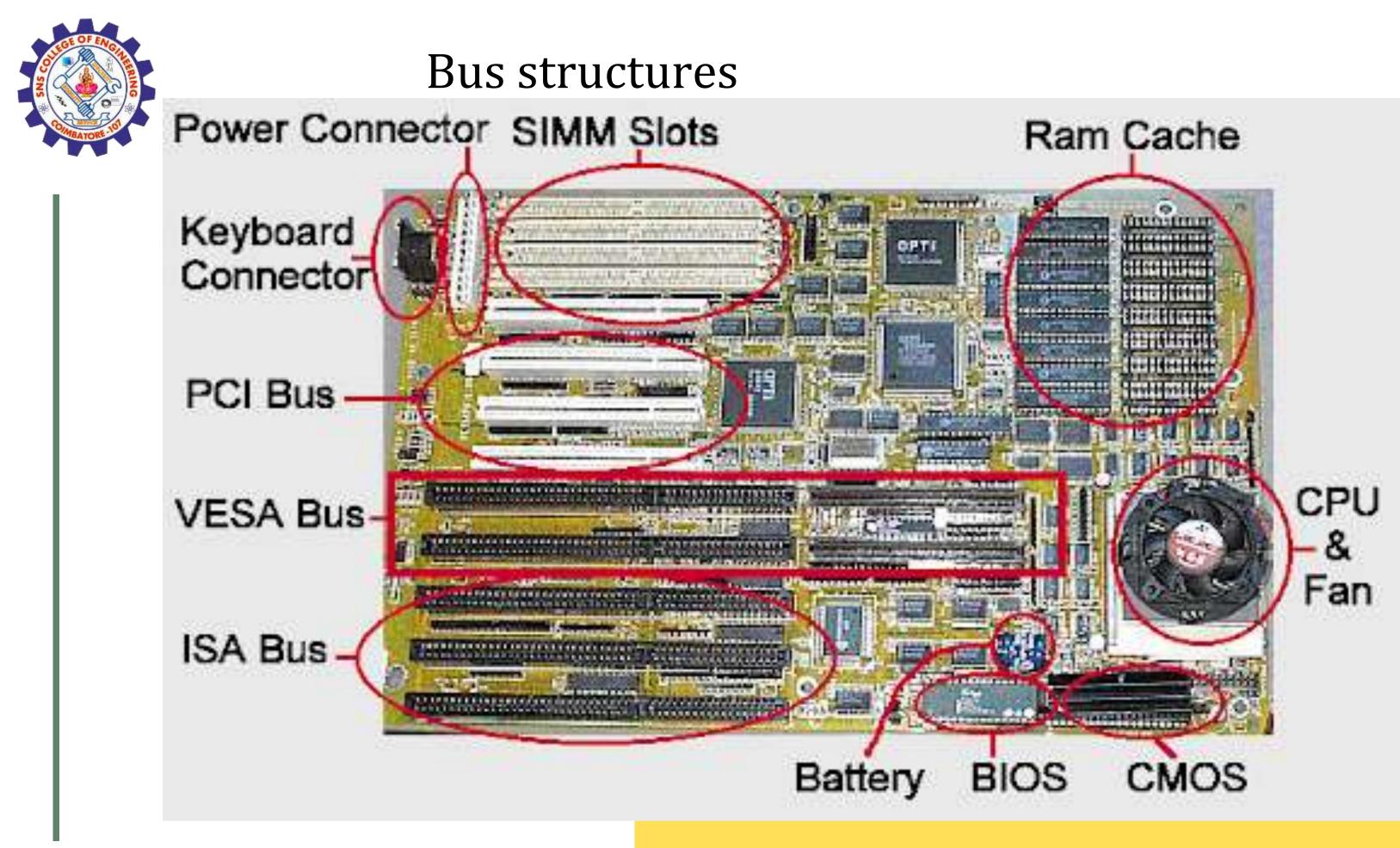

- Buses in PC

- ✓ PCI- Peripheral component Interconnect

- ✓ VESA-Video Electronics Standards Association

- ✓ ISA- Industry standard architecture

- ✓ AGP- Accelerated graphics port

12/15/2023

### Assessment

a). What is Multi Bus?

b) Mention the purpose

- 1.Address bus\_\_\_\_\_

- 2. Data bus \_\_\_\_\_

- 3.Control bus

- 4.buffers \_\_\_\_\_

- 5. Single bus \_\_\_\_

### Performance

The most important measure of a computer is how quickly it can execute programs with high accuracy and efficiency.

Three factors affect performance:

➢ Hardware design

➢ Instruction set

➢ Compiler

### Performance

Processor time to execute a program depends on the hardware involved in the execution of individual machine instructions.

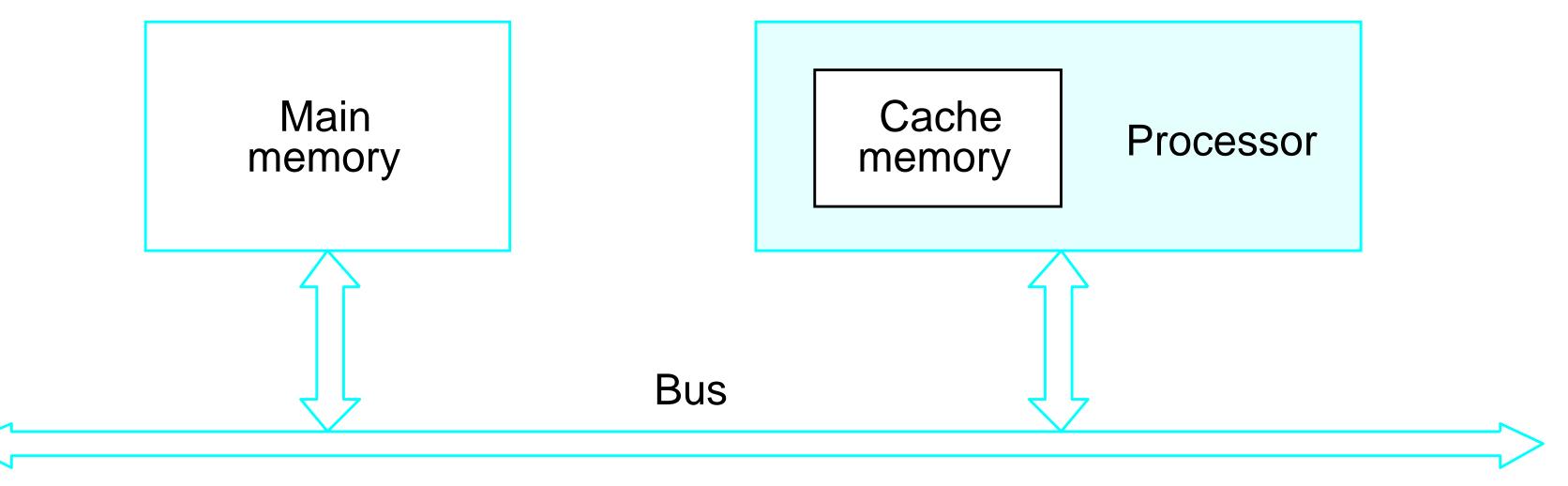

### Figure 1

### Performance

The processor and a relatively small cache memory can be fabricated on a single integrated circuit chip.

- ✓ Speed

- ✓ Cost

- ✓ Memory management

### Performance - Processor Clock

Clock, clock cycle, and clock rate

The execution of each instruction is divided into several steps, each of which completes in one clock cycle.

> The CPU places the address on the address bus during this time period

Bus structures and performance/Computer organization and architecture/Dr.K.Periyakaruppan/CSE/SNSCE

The CPU reads the data from the data bus during this time period The memory system must decode the address and place the data on the data bus during this time period

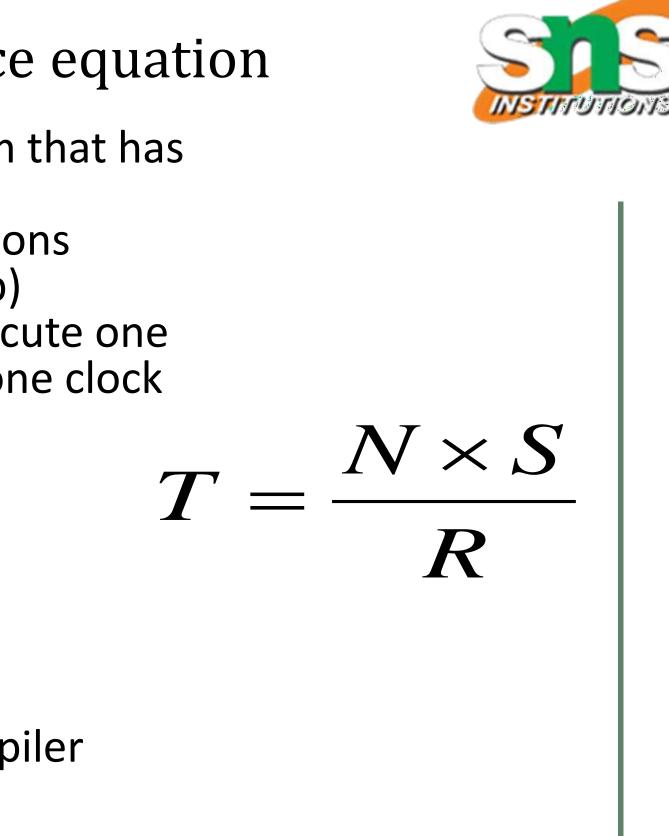

### Performance –Basic performance equation

- ✓T processor time required to execute a program that has been prepared in high-level language

- ✓ N number of actual machine language instructions needed to complete the execution (note: loop)

- S average number of basic steps needed to execute one machine instruction. Each step completes in one clock cycle

- ✓ R− Clock rate

## How to improve T?

R – Increase R by IC technology

N– Reduce N by ISA, micro architecture and compiler

S– Reduce S by ISA and compiler

## Performance – Basic performance equation

- ✓ High level language

- ≻C=A+B

- ✓Assembly language

- ≻Add R4, R5, R6

- ➢ basic steps needed to execute Add R4, R5, R6

| Step |                                 | Action             |                   |       |

|------|---------------------------------|--------------------|-------------------|-------|

| 1    | PC <sub>out</sub>               | R=B,               | MAR <sub>in</sub> | Read, |

| 2    | WMFC                            |                    |                   |       |

| 3    | MDR <sub>outB</sub> ,           | R=B,               | <sup>IR</sup> in  |       |

| 4    | <sup>R4</sup> outA <sup>,</sup> | <sup>R5</sup> outB | , SelectA,        | Add,  |

Control sequence for the instruction. Add R4,R5,R6, for the three-bus organization

IncPC

<sup>R6</sup> in End ,

### Performance - Pipeline and Superscalar Operation

$\checkmark$  Instructions are not necessarily executed one after another. ✓ Pipelining – overlapping the execution of successive instructions.

✓ Superscalar operation – multiple instruction pipelines are implemented in the processor.  $\checkmark$  Goal – reduce S

12/15/2023

Bus structures and performance/Computer organization and architecture/Dr.K.Periyakaruppan/CSE/SNSCE

# $= \frac{N \times S}{R}$

# **Performance - compiler**

✓ A compiler translates a high-level language program into a sequence of machine instructions.

✓ To reduce N, we need a suitable machine instruction set and a compiler that makes good use of it.

$\checkmark$  Goal – reduce N×S

✓ A compiler may not be designed for a specific processor; however, a highquality compiler is usually designed for, and with, a specific processor.

### **Performance Measurement**

$\checkmark$  T is difficult to compute.

$\checkmark$  Measure computer performance using benchmark programs.

✓ System Performance Evaluation Corporation (SPEC) selects and publishes representative application programs for different application domains, together with test results for many commercially available computers.

Compile and run (no simulation)

$SPEC rating = \frac{\text{Running}}{\text{Running}} \text{ time on the reference computer}$ SPEC rating =  $(\prod_{i=1}^{n} SPEC_{i})^{\frac{1}{n}}$

n= number of programs

### **Performance Measurement**

If the SPEC rating = 50 means that computer under test is 50 times as fast as the reference computer

### Assessment

a). What is Basic performance equation?

b) What are the three factors affect performance:

1..\_\_\_\_

2. \_\_\_\_\_

3. \_\_\_\_\_

### Reference

1. Carl Hamacher, Zvonko Vranesic and Safwat Zaky, "Computer Organization", McGraw-Hill, 6<sup>th</sup> Edition 2012.