#### SNS COLLEGE OF ENGINEERING

Kurumbapalayam (Po), Coimbatore – 641 107

#### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF COMPUTER SCIENCE AND TECHNOLOGY

# COURSE CODE & NAME : 19IT301 COMPUTER ORGANIZATION AND ARCHITECTURE

II YEAR / III SEMESTER

Unit 2: ARITHMETIC OPERATIONS

Topic: Addition and subtraction of signed numbers

#### **Signed Numbers**

| $X_i$ | Yi | Carry-in c <sub>i</sub> | Sums, | Carry-out ci+ |

|-------|----|-------------------------|-------|---------------|

| 0     | 0  | 0                       | 0     | 0             |

| 0     | 0  | 1                       | 1     | 0             |

| 0     | 1  | 0                       | 1     | 0             |

| 0     | 1  | 1                       | 0     | 1             |

| 1     | 0  | 0                       | 1     | 0             |

| 1     | 0  | 1                       | 0     | 1             |

| 1     | 1  | 0                       | 0     | 1             |

| 1     | 1  | 1                       | 1     | 1             |

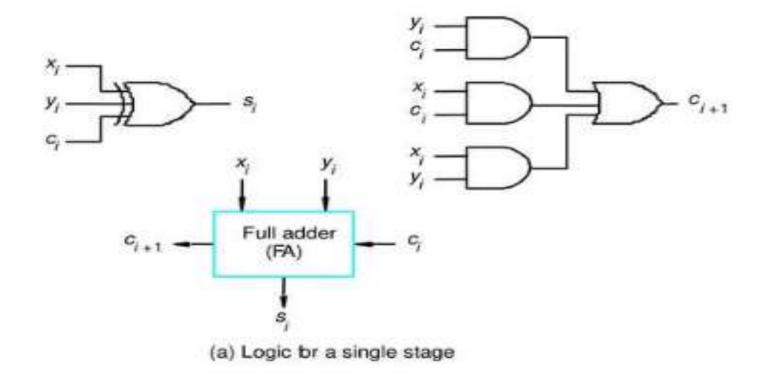

$$\begin{array}{lll} S_i &=& \overline{X_i} \overline{Y_i} C_i + \overline{X_i} \overline{Y_i} \overline{C_i} + \overline{X_i} \overline{Y_i} \overline{C_i} + \overline{X_i} \overline{Y_i} C_i = x_i \oplus y_i \oplus c_i \\ C_{i+1} &=& y_i C_i + \overline{X_i} C_i + \overline{X_i} \overline{Y_i} \end{array}$$

#### Example:

$$\frac{X}{Z} = \frac{7}{13} = \frac{0}{1} \cdot \frac{1}{1} \cdot \frac{1}{1} \cdot \frac{1}{0} \cdot \frac{0}{0} \cdot \frac{0}{0}$$

Carry-out

$$C_{i+1} = \frac{X_i}{y_i} = \frac{C_{arry-in}}{c_i}$$

Legend for stage

Logic specification for a stage of binary addition.

### Logic for single stage

# A full adder (FA)

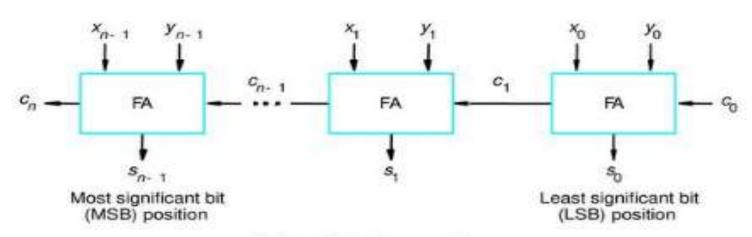

#### An n-bit ripple carry adder

## n-bit ripple-carry adder

(b) An n-bit ripple-carry adder

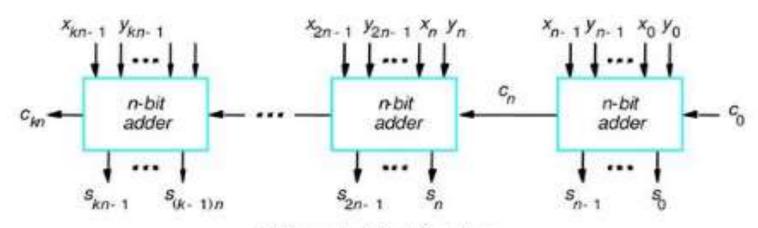

#### Cascade of K n-bit adders

# kn-bit ripple-carry adder

(c) Cascade of k n-bit adders

Logic for addition of binary vectors.

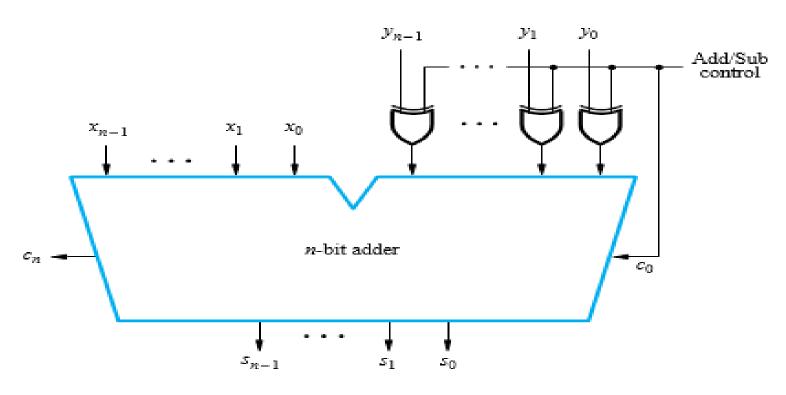

#### Binary addition and subtraction logic circuit

Binary addition/subtraction logic circuit.

**SNS INSTITUTIONS**

# ASSESSMENT

What is Full adder?

#### Reference

1. Carl Hamacher, Zvonko Vranesic and Safwat Zaky, "Computer Organization", McGraw-Hill, 6th Edition 2012.

# Thank you!