### **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (PO), Coimbatore - 641 107 Accredited by NAAC-UGC with 'A' Grade Approved by AICTE, Recognized by UGC & Affiliated to Anna University, Chennai

### **DEPARTMENT OF INFORMATION TECHNOLOGY COURSE NAME: 19IT301 COMPUTER ORGANIZATION AND ARCHITECTURE**

**II YEAR/ III SEM**

**Unit 3 : Processor and Pipeling**

**Topic 1: Fundamental Concepts**

SNSCE / IT / III Sem / V. Vaishnavee AP-IT

# **Overview**

- Instruction Set Processor (ISP) or Processor Executes machine instructions and coordinates other units

- Central Processing Unit (CPU)  $\bullet$

- High performance processors • Pipelining

- Superscalar processing

- A typical computing task consists of a series of steps specified by a sequence of machine instructions that constitute a program.

- An instruction is executed by carrying out a sequence of more  $\bullet$ rudimentary operations.

SNSCE / IT / V Sem / V. Vaishnavee AP-IT

- Processor fetches one instruction at a time and perform the operation specified.

- Instructions are fetched from successive memory locations until a branch or a jump instruction is encountered.

- Processor keeps track of the address of the memory location containing the next instruction to be fetched using Program Counter (PC).

- Instruction Register (IR)

11/18/2023

SNSCE / IT / V Sem / V.Vaishnavee AP-IT

# 3 steps to execute an Instruction

1. Fetch the contents of the memory location pointed to by the PC. The contents of this location are loaded into the IR (fetch phase).

IR ← [[PC]]

- 2. Assuming that the memory is byte addressable, increment the contents of the PC by 4 (fetch phase).  $PC \leftarrow [PC] + 4$

- 3. Carry out the actions specified by the instruction in the IR (execution phase).

SNSCE / IT / V Sem / V.Vaishnavee AP-IT

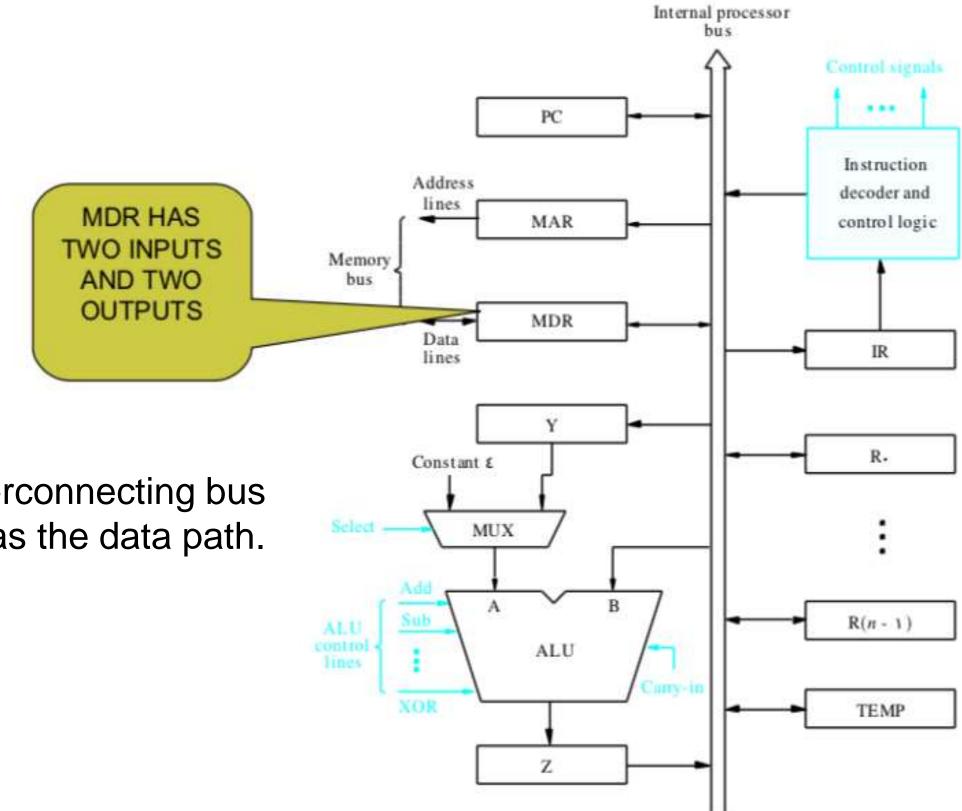

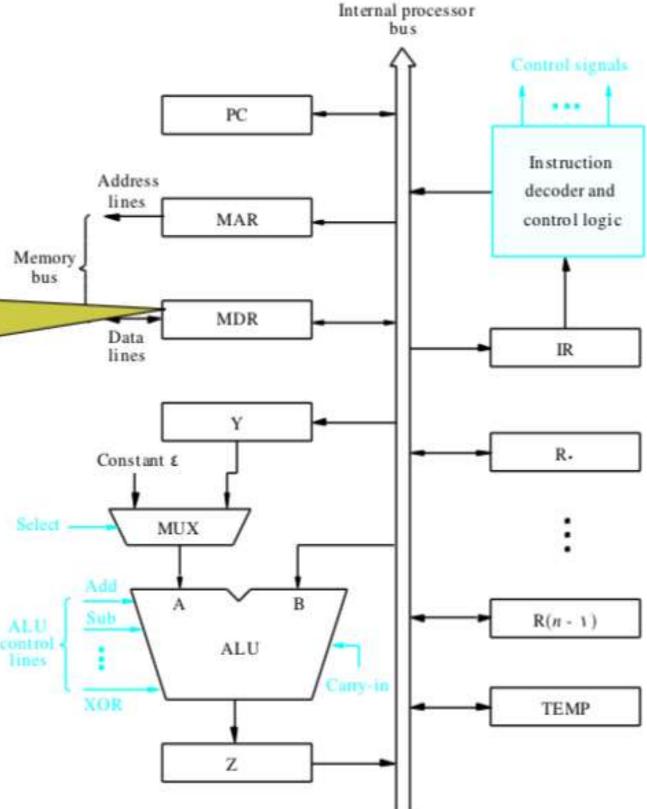

# Single-bus Processor organization

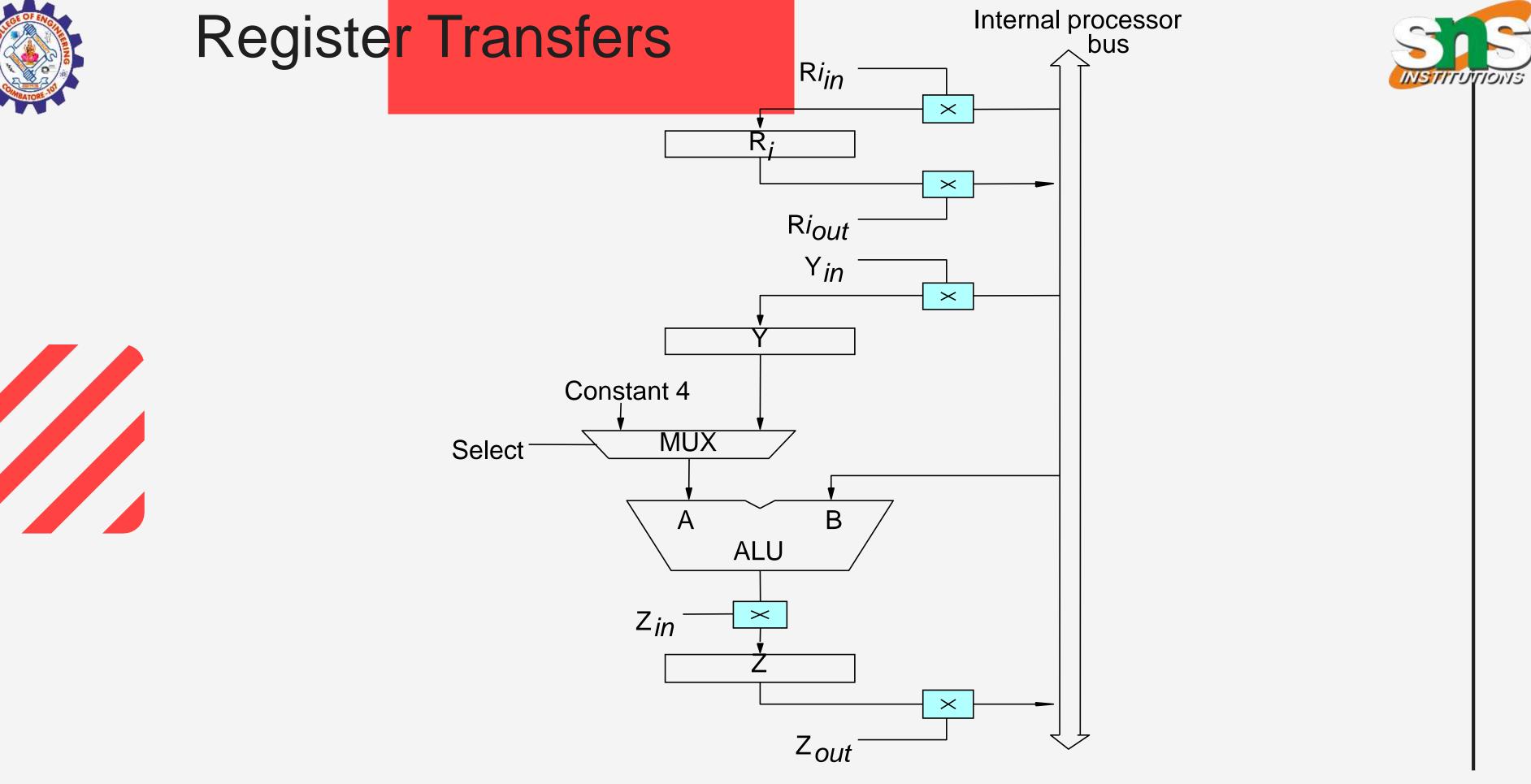

### **Data Path:**

The registers, ALU and interconnecting bus are collectively referred to as the data path.

1/18/2023

SNSCE / IT / V Sem / V. Vaishnavee AP-IT

4/12

# Few operations to execute an instruction

- Fetch the contents of a given memory location and load them into a processor register.

- Transfer a word of data from one processor register to another or to the ALU.

- Perform an arithmetic or a logic operation and store the result in a processor register.

- Store a word of data from a processor register into a given memory location.

Input and output gating for the registers

SNSCE / IT / V Sem / V. Vaishnavee AP-IT

# Register control signals

- The input and output of register R*i* are controlled by signals is Ri<sub>in</sub> and Ri<sub>out</sub>

- $R_{i_{in}}$  is set to 1 data on the bus are loaded into  $R_{i}$ •

- $R_{i_{out}}$  is set to 1 the contents of register are placed on the bus. •

- $R_{out}$  is set to 0 the bus can be used for transferring data from lacksquareother registers

### **Example:**

Transfer the contents of R1 to R4.

- Enable output of register R1 by setting R1<sub>out</sub>=1. This places the contents of R1 on the processor bus.

- Enable input of register R4 by setting R4<sub>in</sub>=1. This loads the data ulletfrom the processor bus into register R4

11/18/2023

SNSCE / IT / V Sem / V. Vaishnavee AP-IT

# Performing an Arithmetic or Logic Operation

- The ALU is a combinational circuit that has no internal storage.

- ALU gets the two operands from MUX and bus. The result is • temporarily stored in register Z.

- What is the sequence of operations to add the contents of register R1 to those of R2 and store the result in R3?R3  $\leftarrow$  R1 + R2

the clock cycle

SNSCE / IT / V Sem / V.Vaishnavee AP-IT

11/18/2023

\* Signals given in any step are activated others are inactive for

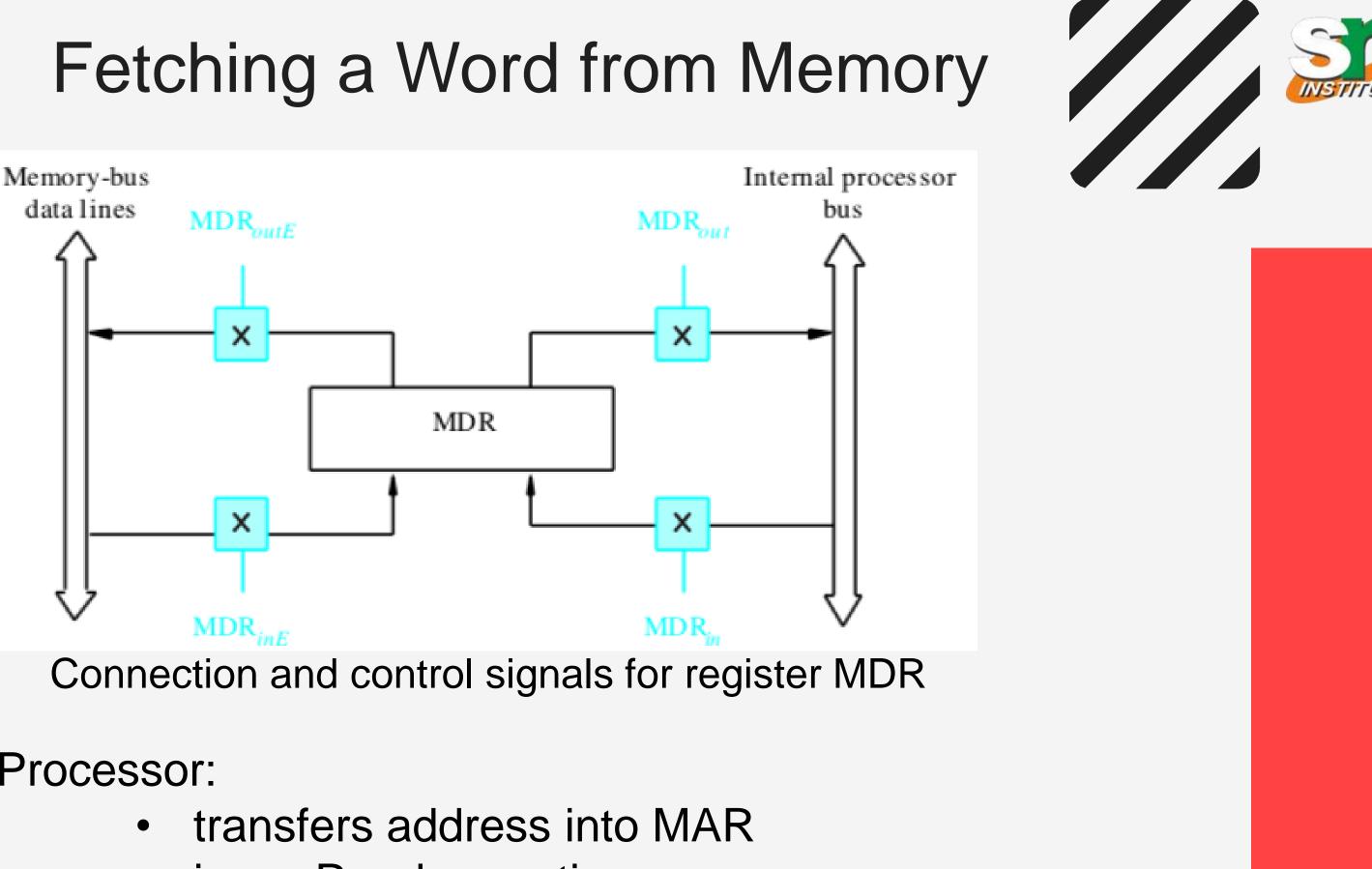

### Processor:

- issue Read operation ullet

- data into MDR  $\bullet$

**SNSCE / IT / V Sem / V. Vaishnavee AP-IT**

# Fetching a Word from Memory

- The response time of each memory access varies (cache miss, memory-mapped I/O,...).

- To accommodate this, the processor waits until it receives an indication that the requested operation has been completed (Memory-Function-Completed, MFC).

Example:

Move (R1), R2

- $\circ$  MAR  $\leftarrow$  [R1]

- Start a Read operation on the memory bus

- Wait for the MFC response from the memory

- Load MDR from the memory bus

- $\circ$  R2  $\leftarrow$  [MDR]

11/18/2023

SNSCE / IT / V Sem / V. Vaishnavee AP-IT

Signals activated for Move (R1), R2:

- R1<sub>out</sub>, MAR<sub>in</sub>, Read

- MDR<sub>inF</sub>, WMFC

- $MDR_{out}$ ,  $R2_{in}$

# Storing a word in memory

- Address is loaded into MAR

- Data to be written loaded into MDR

- Write command is issued Example: Move R2,(R1)

- R1<sub>out</sub>, MAR<sub>in</sub> Ο

- R2<sub>out</sub>, MDR<sub>in</sub>, Write 0

- MDR<sub>outE</sub>, WMFC Ο

**SNSCE / IT / V Sem / V. Vaishnavee AP-IT**

## Thank You

**11/18/2**023

SNSCE / IT/ V Sem/V.VaishnaveeAP-IT