## **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (PO), Coimbatore - 641 107 Accredited by NAAC-UGC with 'A' Grade Approved by AICTE, Recognized by UGC & Affiliated to Anna University, Chennai

# **DEPARTMENT OF INFORMATION TECHNOLOGY COURSE NAME: 19IT301 COMPUTER ORGANIZATION**

**AND ARCHITECTURE**

**II YEAR/ III SEM**

**Unit 2 : ARITHMETIC OPERATIONS**

**Topic 5: Fast Multiplication**

**SNSCE / IT / III Sem / Vaishnavee AP-IT**

# **Fast Multiplication**

Two techniques for speeding up the multiplication operation

- 1. Bit-pair Recoding of Multipliers

- 2. Carry-Save addition of summands

### **Bit-pair Recoding of Multipliers:**

Guarantees the maximum number of summands (versions of multiplicand) added is n/2 for n-bit operands

### **Carry-Save Addition of summands**

Reduces the time needed to add the summands

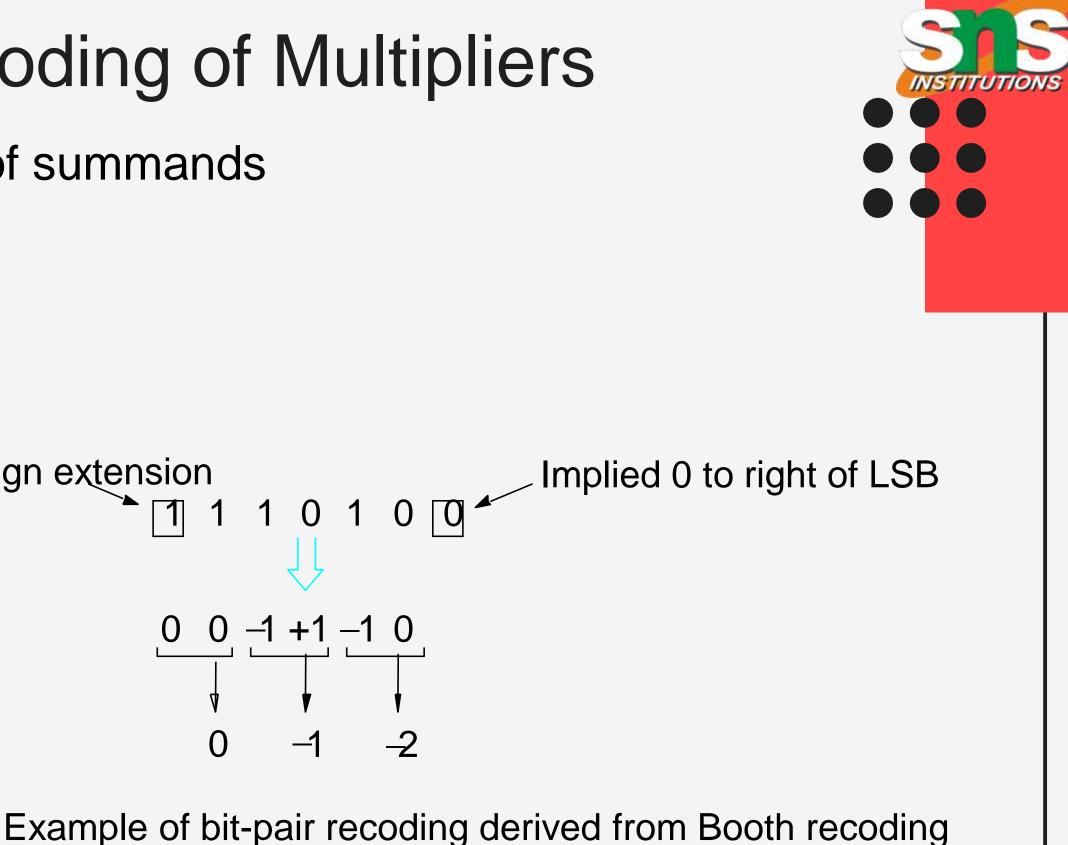

# **Bit-pair Recoding of Multipliers**

- It halves the maximum number of summands

- Derived from Booth algorithm  ${\color{black}\bullet}$

| Bit iBit i-1selected by bit i00 $0 \times M$ Sign extension01 $+1 \times M$ 110 $-1 \times M$ $0 = 1 + 1 - 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 +$ | Multiplier                   | Version of multiplica | and                                |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|------------------------------------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                       | Bit <i>i</i> Bit <i>i</i> -1 | -                     |                                    |

| 1 0 $-1 \times M$ $0 -1 + 1 - 1$                                                                                                            | 0 0                          | 0 X M                 | Sign extension $\boxed{1}$ 1 1 0 1 |

|                                                                                                                                             | 0 1                          | +1 X M                |                                    |

| 1 1 0 X M 0 1                                                                                                                               | 1 0                          | -1 X M                |                                    |

|                                                                                                                                             | 1 1                          | 0 X M                 |                                    |

**SNSCE / IT / V Sem / V Vaishnavee AP-IT**

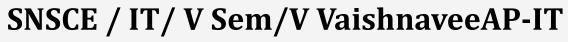

# Multiplier Bit pair recoding

| Multiplier bit-pair |   | Multiplier bit on the right | Multiplicand         |  |  |

|---------------------|---|-----------------------------|----------------------|--|--|

| <i>i</i> + 1        | i | i–1                         | selected at position |  |  |

| 0                   | 0 | 0                           | 0 X M                |  |  |

| 0                   | 0 | 1                           | +1 X M               |  |  |

| 0                   | 1 | 0                           | +1 X M               |  |  |

| 0                   | 1 | 1                           | +2 X M               |  |  |

| 1                   | 0 | 0                           | -2 X M               |  |  |

| 1                   | 0 | 1                           | -1 X M               |  |  |

| 1                   | 1 | 0                           | -1 X M               |  |  |

| 1                   | 1 | 1                           | 0 X M                |  |  |

### Table of multiplicand selection decisions

**SNSCE / IT / V Sem / V Vaishnavee AP-IT**

### **Example: Booth Multiplication** 1 1 0 1 (+13) 0 -13 = 10011(-6) 1 1 0 1 0 0 1 0 1 0 - 1 + 1 - 1 0 0 0 0 0 0 0 0 1 1 1 0 $\mathbf{O}$ 1 0 0 1 1 1 0 0 0 0 0 $\mathbf{0}$ 1 1 1 0 1 1 0 0 1 0 (-78)

Example

SNSCE / IT / V Sem / V Vaishnavee AP-IT

|        |        |     |       |       |     |     | NSTITU |  |

|--------|--------|-----|-------|-------|-----|-----|--------|--|

| iplica | and:   | 0   | 1     | 1     | 0   | 1   |        |  |

|        |        | 0   |       | - 1   |     | - 2 |        |  |

| 1      | 1      | 0   | 0     | 1     | 1   | 0   | _      |  |

| 1      | 0      | 0   | 1     | 1     | X   | Х   |        |  |

| 0      | 0      | 0   | X     | X     | X   | X   |        |  |

| 0      | 1      | 1   | 0     | 0     | 1   | 0   | _      |  |

| requ   | uiring | onl | y n/2 | 2 sun | nma | nds |        |  |

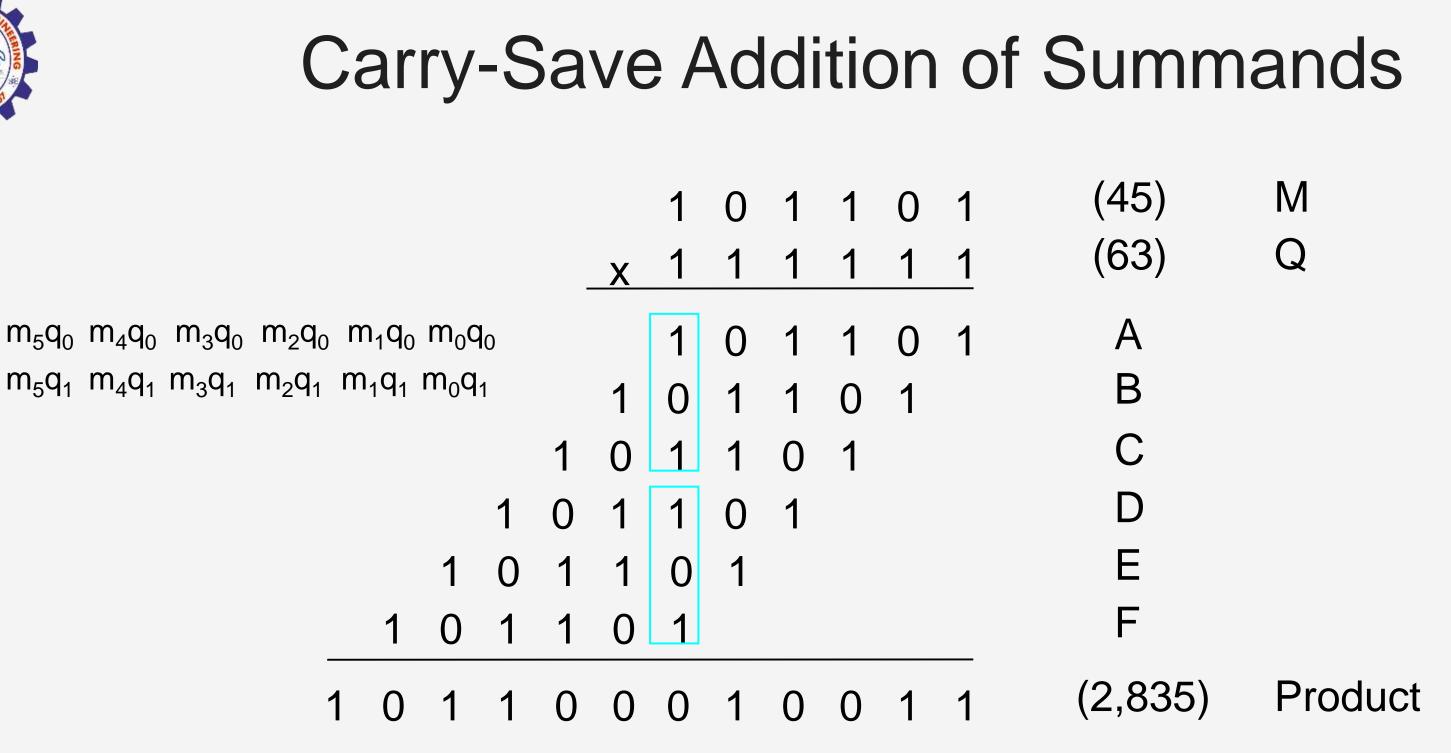

# **Carry-Save Addition of Summands**

- Multiplication requires addition of several summands.

- Carry- Save Addition(CSA) technique speeds up the addition process

**SNSCE / IT / V Sem / V Vaishnavee AP-IT**

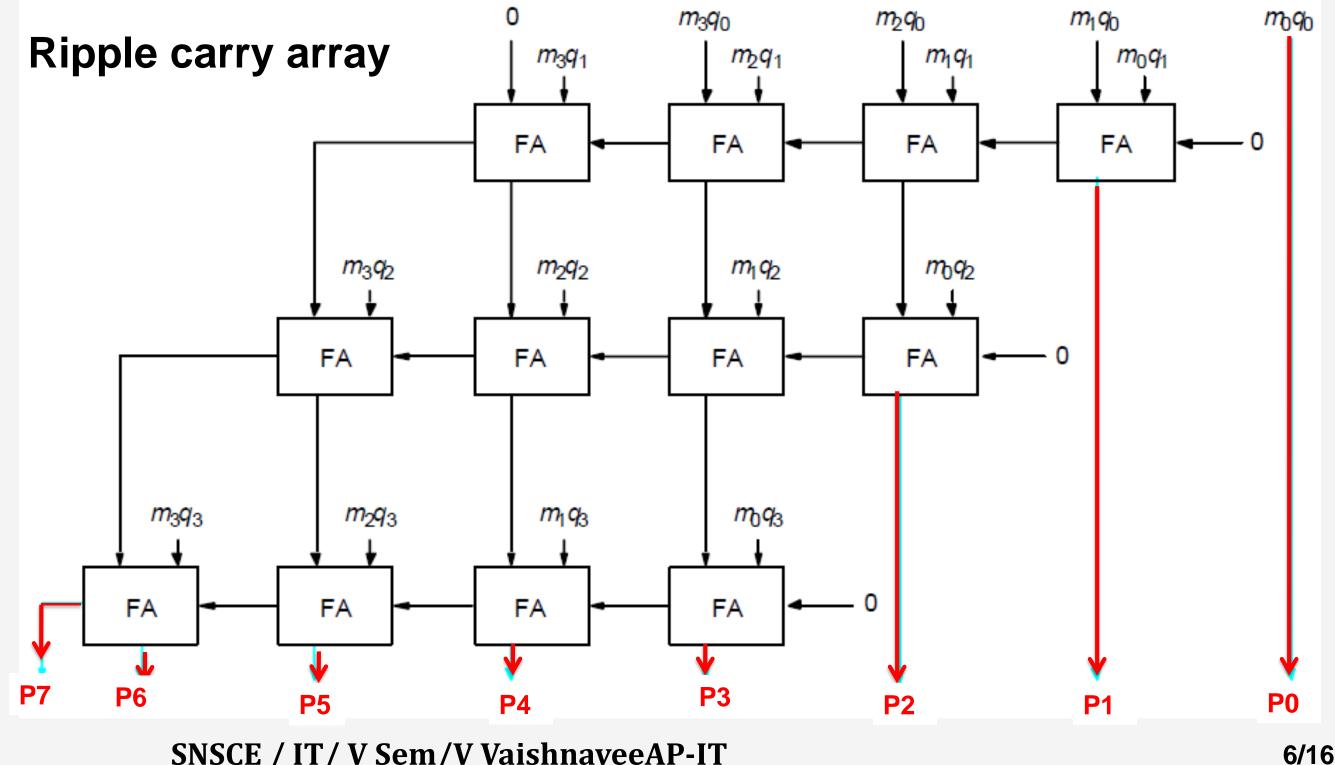

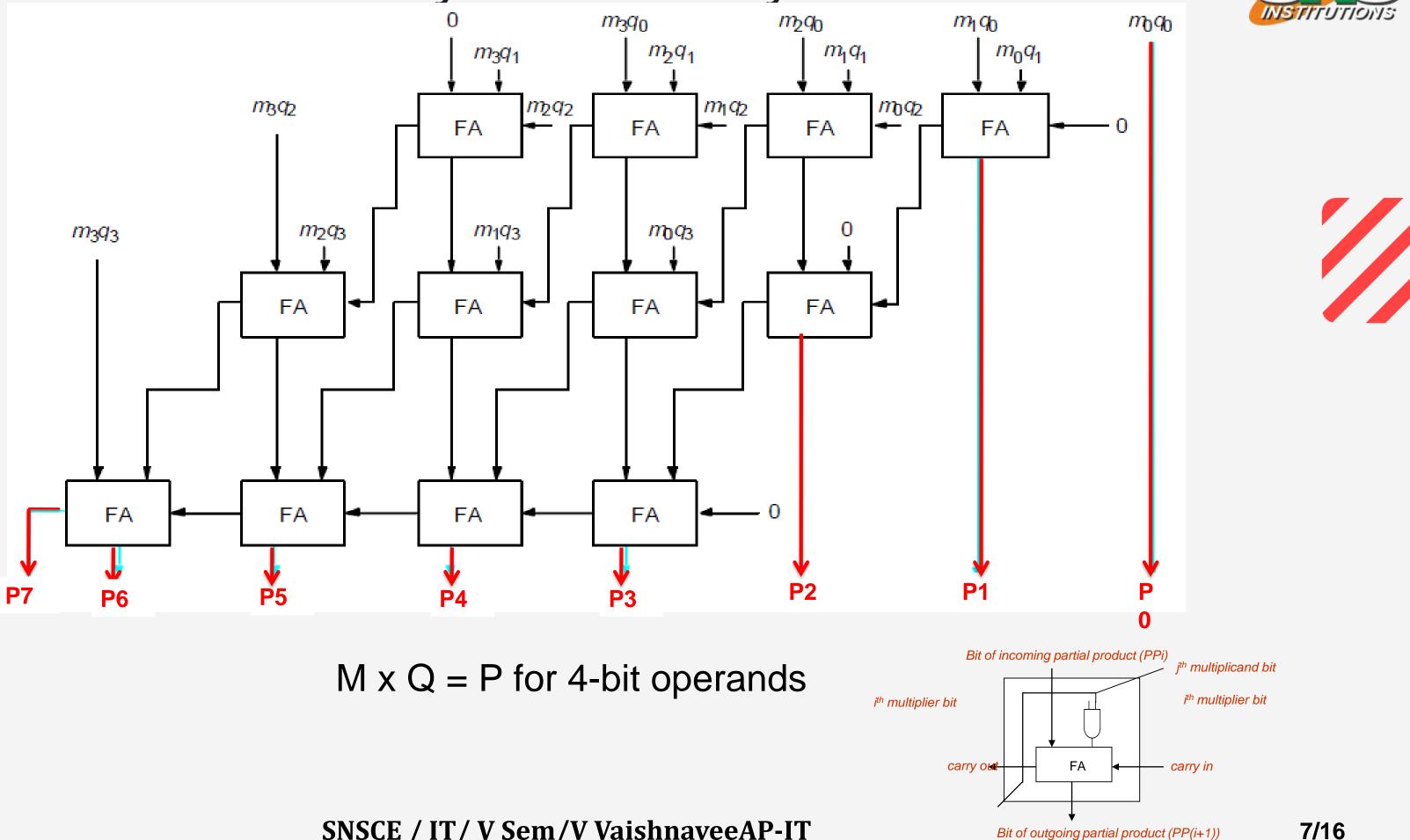

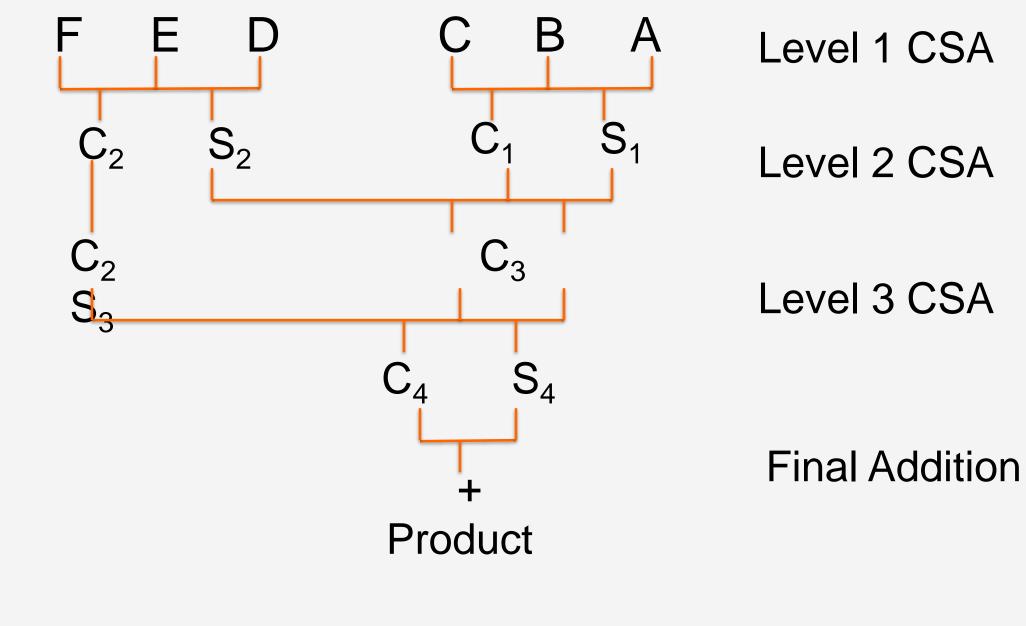

# **Carry-Save Array**

**SNSCE / IT / V Sem / V Vaishnavee AP-IT**

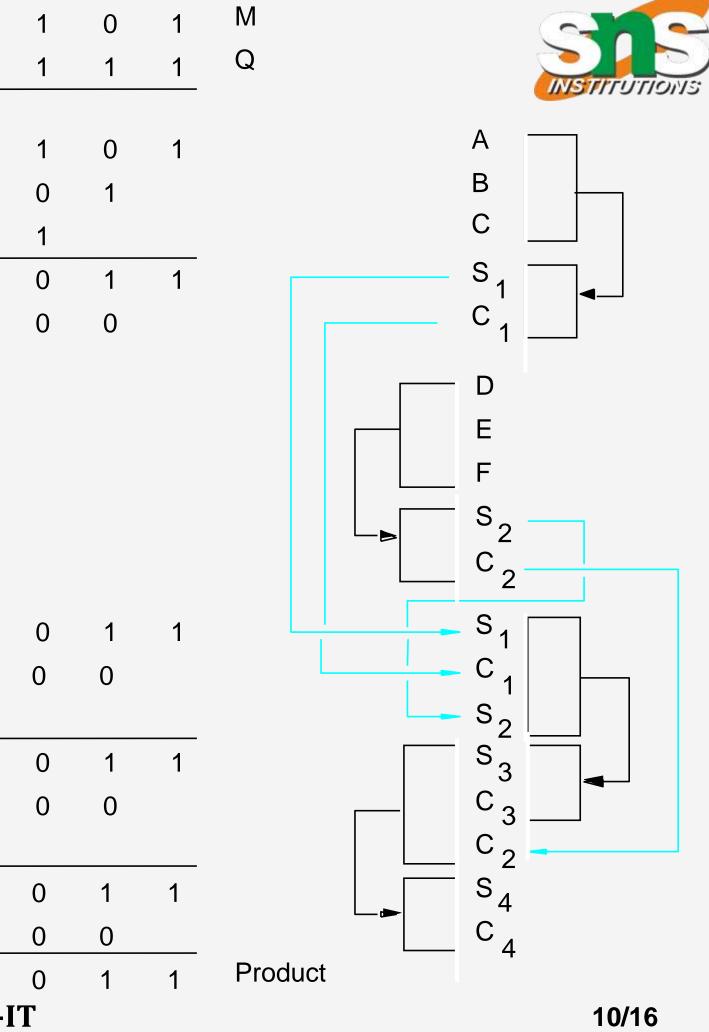

# Carry-Save Addition of Summands

- Consider the addition of many summands, we can:  $\succ$  Group the summands in threes and perform carry-save addition on each of these groups in parallel to generate a set of S and C vectors in one full-adder delay

- $\succ$  Group all of the S and C vectors into threes, and perform carrysave addition on them, generating a further set of S and C vectors in one more full-adder delay

- > Continue with this process until there are only two vectors remaining

- $\succ$  They can be added in a RCA or CLA to produce the desired product

SNSCE / IT / V Sem / Vaishnavee AP-IT

A multiplication example used to illustrate carry-save addition

**SNSCE / IT / V Sem / V Vaishnavee AP-IT**

11/18/2023

9/16

### **Carry- Save Addition**

|                                    |   |   |   |   |   | 1 | 0 | 1 |  |

|------------------------------------|---|---|---|---|---|---|---|---|--|

| •                                  |   |   |   |   | х | 1 | 1 | 1 |  |

|                                    |   |   |   |   |   |   |   |   |  |

|                                    |   |   |   |   |   | 1 | 0 | 1 |  |

|                                    |   |   |   |   | 1 | 0 | 1 | 1 |  |

|                                    |   |   |   | 1 | 0 | 1 | 1 | 0 |  |

|                                    |   |   |   | 1 | 1 | 0 | 0 | 0 |  |

|                                    |   |   | 0 | 0 | 1 | 1 | 1 | 1 |  |

|                                    |   |   |   | - |   |   |   |   |  |

|                                    |   |   | 1 | 0 | 1 | 1 | 0 | 1 |  |

|                                    |   | 1 | 0 | 1 | 1 | 0 | 1 |   |  |

|                                    | 1 | 0 | 1 | 1 | 0 | 1 |   |   |  |

|                                    | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |  |

| 0                                  | 0 | 1 | 1 | 1 | 1 | 0 | 0 |   |  |

|                                    |   |   |   |   | _ | 0 | 0 | • |  |

|                                    |   |   |   | 1 | 1 | 0 | 0 | 0 |  |

|                                    |   |   | 0 | 0 | 1 | 1 | 1 | 1 |  |

|                                    | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |  |

|                                    | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |  |

| 0                                  | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 |  |

| 0                                  | 0 | 1 | 1 | 1 | 1 | 0 | 0 |   |  |

| 0                                  | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |  |

| 0                                  | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |  |

| 1                                  | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 |  |

| SNSCE / IT/ V Sem/V VaishnaveeAP-I |   |   |   |   |   |   |   |   |  |

# Schematic Representaion of CSA

**SNSCE / IT / V Sem / V Vaishnavee AP-IT**

# Gate Delays

Logic gate delay to perform 6 x 6 multiplication

- 1 AND gate delay

- 2 gate delays per CSA level

- CLA has 8 gate delays

Total gate delays =  $1 + 2 \times 3 \text{ CSA}$  levels + 8 = 15

In general, for n summands of n x n multiplication,  $= 1.7 \log_2 n - 1.7$  levels of CSA steps needed

Using bit-pair recoding,

$= 1.7 \log_2 n - 3.4$  levels of CSA steps needed

SNSCE / IT / V Sem / Vaishnavee AP-IT

- 1. We make use of \_\_\_\_\_\_ circuits to implement multiplication.

- a) Flip flops

- b) Combinatorial

- c) Fast adders

- d) None of the mentioned

2. The method used to reduce the maximum number of summands by half is

- a) Fast multiplication

- b) Bit-pair recoding

- c) Quick multiplication

- d) None of the mentioned

# Assessment

- 3. The multiplier -6(11010) is recorded as \_\_\_\_\_\_ a) 0-1-2

- b) 0-1+1-10

- c) -2-10

- d) None

- a) 1100110011 b) 1101110001 c) 1010101010 d) 1111111000

- 4. CSA stands for?

- a) Computer Speed Addition

- b) Carry Save Addition

- c) Computer Service Architecture d) None of the mentioned

**SNSCE / IT / V Sem / V Vaishnavee AP-IT**

11/18/2023

### 5. The product of -13 & 11 is

## Answers

1. C 2. B 3. A 4. B 5. B

SNSCE / IT/ V Sem/V VaishnaveeAP-IT

11/18/2023

15/16

# Thank You

**11/18/2**023

SNSCE / IT/ V Sem/V VaishnaveeAP-IT

16/16