Kurumbapalayam (PO), Coimbatore – 641 107

Accredited by NAAC-UGC with 'A' Grade

Approved by AICTE, Recognized by UGC & Affiliated to Anna University, Chennai

#### **DEPARTMENT OF ECE**

COURSE NAME: 19IT301 COMPUTER ORGANIZATION

AND ARCHITECTURE

II YEAR/ III SEM

**Unit 2: ARITHMETIC OPERATIONS**

Topic 1: Addition and subtraction of signed

numbers

## Binary, signed interger representation

| b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> |   |   |   | Sign and<br>Magnitude | 2's Complement |

|-------------------------------------------------------------|---|---|---|-----------------------|----------------|

| 0                                                           | 1 | 1 | 1 | +7                    | +7             |

| 0                                                           | 1 | 1 | 0 | +6                    | +6             |

| 0                                                           | 1 | 0 | 1 | +5                    | +5             |

| 0                                                           | 1 | 0 | 0 | +4                    | +4             |

| 0                                                           | 0 | 1 | 1 | +3                    | +3             |

| 0                                                           | 0 | 1 | 0 | +2                    | +2             |

| 0                                                           | 0 | 0 | 1 | +1                    | +1             |

| 0                                                           | 0 | 0 | 0 | +0                    | +0             |

| 1                                                           | 0 | 0 | 0 | -0                    | -8             |

| 1                                                           | 0 | 0 | 1 | -1                    | -7             |

| 1                                                           | 0 | 1 | 0 | -2                    | -6             |

| 1                                                           | 0 | 1 | 1 | -3                    | -5             |

| 1                                                           | 1 | 0 | 0 | -4                    | -4             |

| 1                                                           | 1 | 0 | 1 | -5                    | -3             |

| 1                                                           | 1 | 1 | 0 | -6                    | -2             |

| 1                                                           | 1 | 1 | 1 | -7                    | _1             |

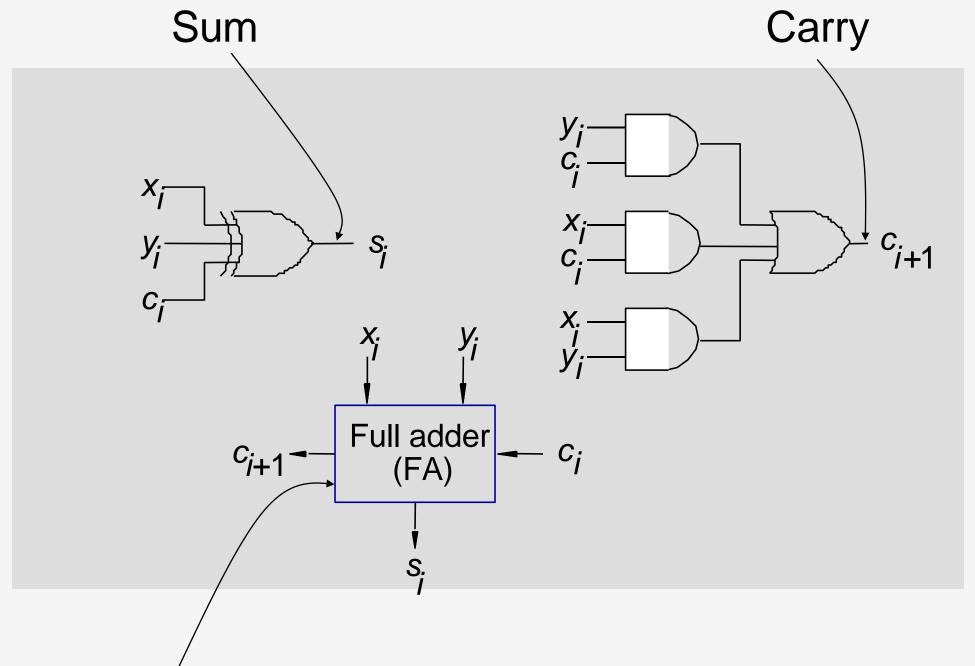

# Logic specification for a stage of binary addition

At the *i*<sup>th</sup> stage:

**Input:**

$c_i$  is the carry-in

Output:

$s_i$  is the sum  $c_{i+1}$  carry-out to  $(i+1)^{st}$  state

| <b>X</b> i | <b>y</b> i | Carry-in c | Sums: Carry-out ci+1 |

|------------|------------|------------|----------------------|

| 0          | 0          | 0          | 0 0                  |

| 0          | 0          | 1          | 1 0                  |

| 0          | 1          | 0          | 1 0                  |

| 0          | 1          | 1          | 0 1                  |

| 1          | 0          | 0          | 1 0                  |

| 1          | 0          | 1          | 0 1                  |

| 1          | 1          | 0          | 0 1                  |

| 1          | 1          | 1          | 1 1                  |

$$S_{i} = X_{i}Y_{i}G + X_{i}Y_{i}G + X_{i}Y_{i}G + X_{i}Y_{i}G = X_{i} \oplus Y_{i} \oplus C_{i}$$

$$C_{i+1} = Y_{i}C_{i} + X_{i}C_{i} + X_{i}Y_{i}$$

Example:

$$\frac{X}{Z} = \frac{7}{13} = \frac{7}{100} = \frac{7}{10$$

## Addition logic for a single stage

Full Adder (FA): Symbol for the complete circuit for a single stage of addition

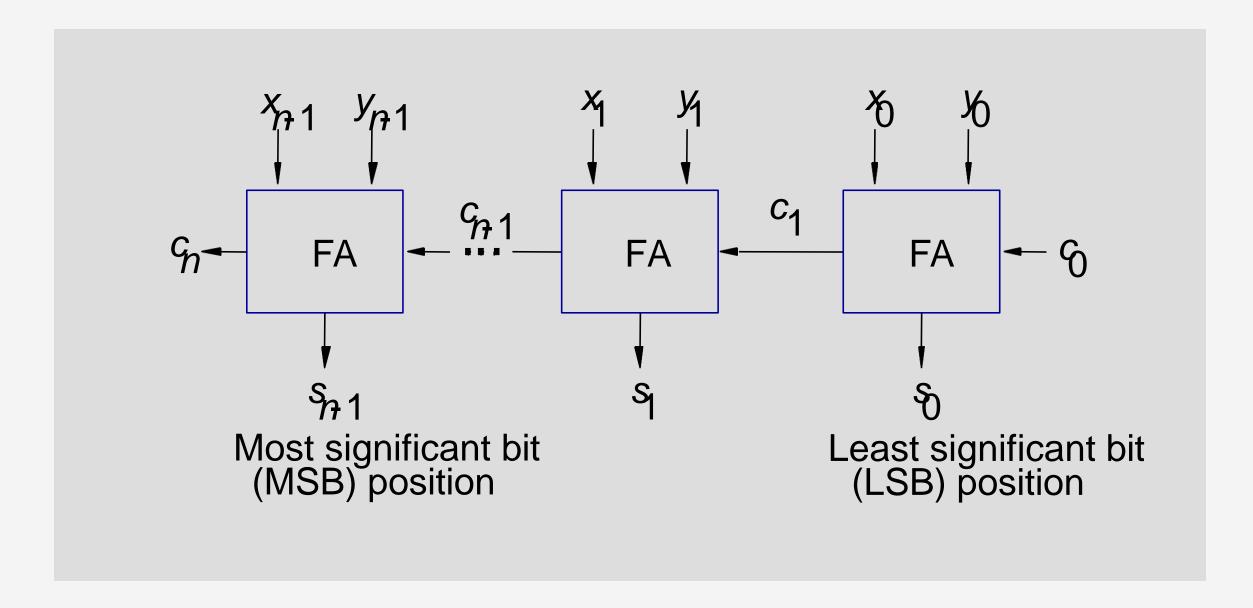

## n-bit ripple carry adder

- Cascade n-full adder (FA) blocks to form a n-bit adder.

- Carries propagate or ripple through this cascade, n-bit ripple carry adder.

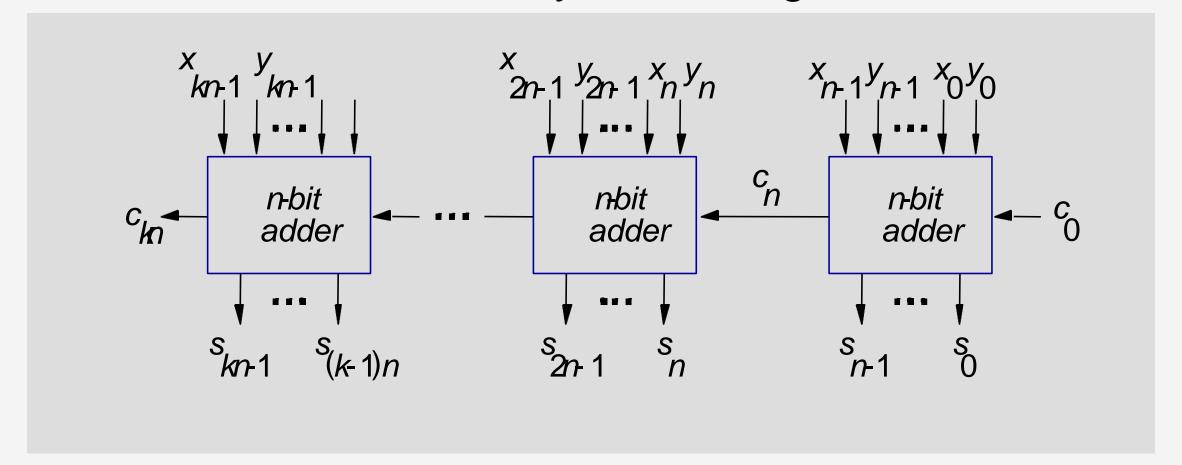

#### K n-bit adder

K n-bit numbers can be added by cascading k n-bit adders

- Carry-in  $c_0$  into the LSB position provides a convenient way to perform subtraction

- Each n-bit adder forms a block, so this is cascading of blocks.

- Carries ripple or propagate through blocks, Blocked Ripple Carry Adder

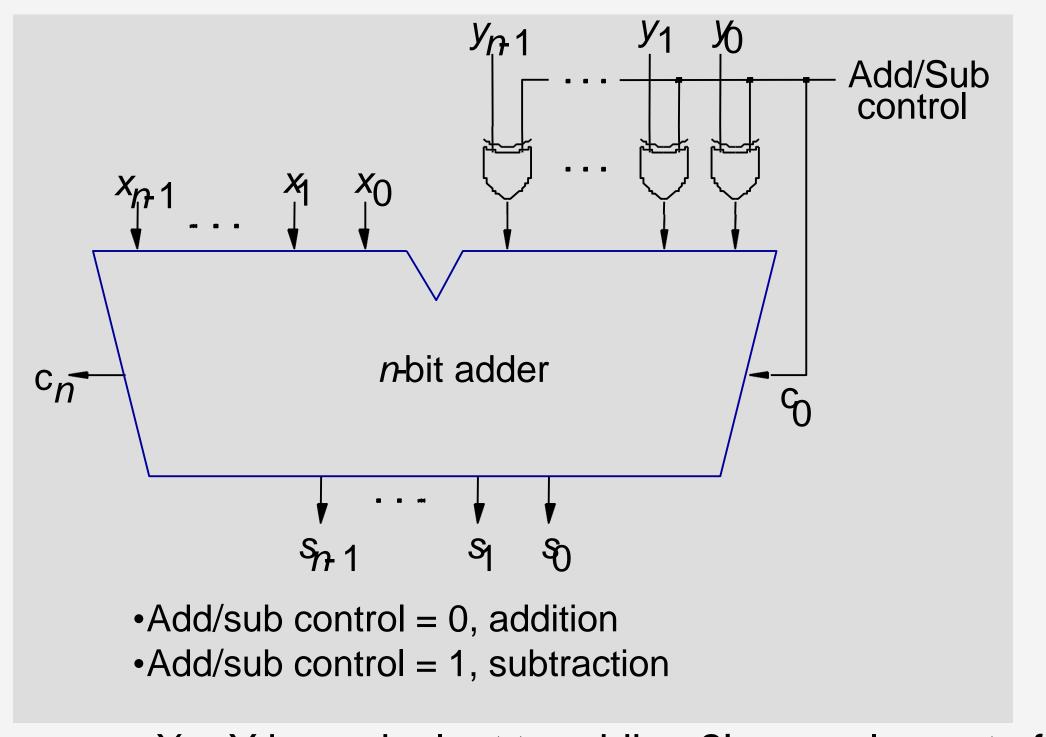

### Binary addition- subtraction logic network

- X Y is equivalent to adding 2's complement of Y to X

- 2's complement is equivalent to 1's complement + 1

- X Y = X + Y + 1

#### Detecting overflows

- Overflows can only occur when the sign of the two operands is the same.

- Overflow occurs if the sign of the result is different from the sign of the operands.

- Circuit to detect overflow can be implemented by the following logic expressions:

$$Overflow = x_{n-1}y_{n-1}\bar{s}_{n-1} + \bar{x}_{n-1}\bar{y}_{n-1}s_{n-1}$$

$$Overflow = c_n \oplus c_{n-1}$$

#### Thank You