## **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (PO), Coimbatore – 641 107 Accredited by NAAC-UGC with 'A' Grade Approved by AICTE, Recognized by UGC & Affiliated to Anna University, Chennai

## **DEPARTMENT OF ECE**

**COURSE NAME: 19IT301 COMPUTER ORGANIZATION**

**AND ARCHITECTURE**

**II YEAR/ III SEM**

**Unit 1 : BASIC STRUCTURE OF COMPUTERS Topic 2:**

**Basic operational concepts – Bus Structures**

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT -1

9/30/2023

0/11

9/30/

## Recap

- Activity in a computer is governed by instructions.

- To perform a task, an appropriate program consisting of a list of instructions is stored in the memory.

- Individual instructions are brought from the memory into the ulletprocessor, which executes the specified operations.

- Data to be used as operands are also stored in the memory. ullet

# **Basic Operational Concepts**

Instruction:

Add LOCA, R0

- Add the operand at memory location LOCA to the operand in a register R0 in the processor.

- Place the sum into register R0.

- The original contents of LOCA are preserved.

- The original contents of R0 is overwritten.

- Steps involved:

- Instruction is fetched from the memory into the processor

- ✓ the operand at LOCA is fetched and added to the contents of **R**0

- $\checkmark$  the resulting sum is stored in register R0.

- Load LOCA, R1 ->Memory Access ullet

- Add R1, R0 -> ALU Operation ullet

- Whose contents will be overwritten?

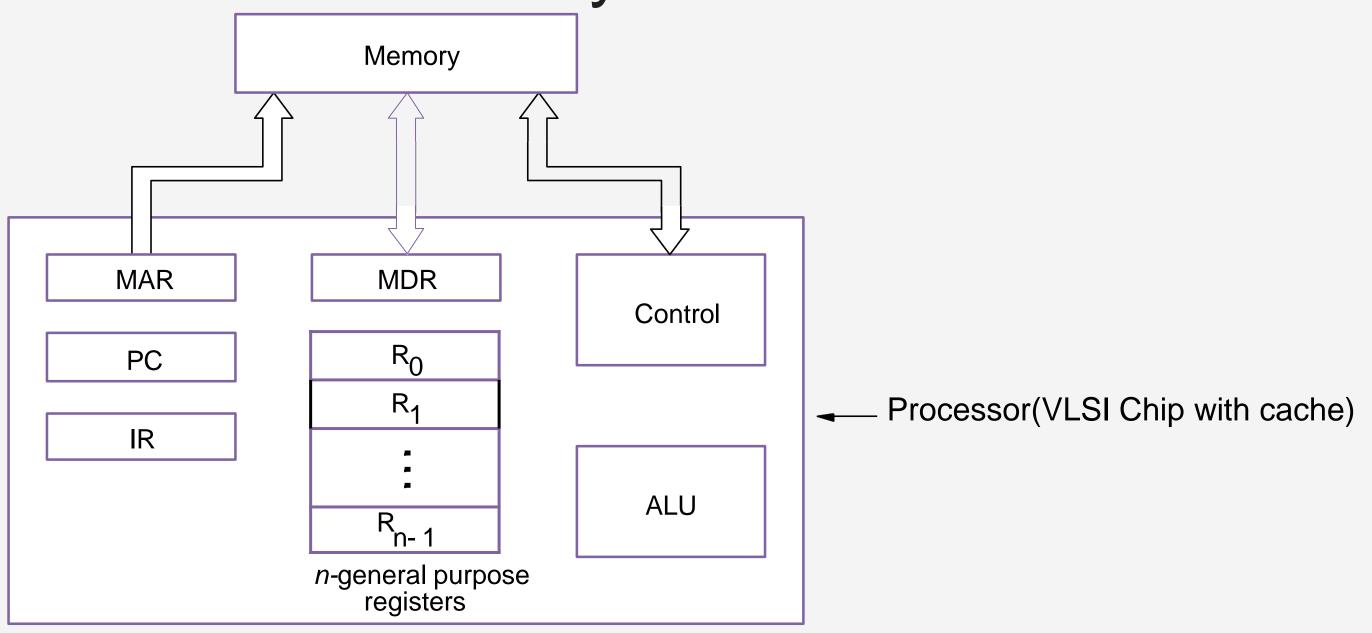

## **Connection Between the Processor and the** Memory

Connections between the processor and the memory.

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT -1

4/11

## Registers

- Instruction register (IR) •

- Program counter (PC) •

- General-purpose register (R0 Rn-1) •

- Memory address register (MAR) •

- Memory data register (MDR) •

5/11

# **Typical Operating Steps**

- Programs reside in the memory through input devices The contents of PC are transferred to MAR

- PC is set to point to the first instruction

- A Read signal is sent to the memory

- The first instruction is read out and loaded into MDR

- The contents of MDR are transferred to IR

- Decode and execute the instruction

- Get operands for ALU

- Either from general-purpose register or ✓ Memory (address to MAR – Read – MDR to ALU)

- Perform operation in ALU

- Store the result back

- ✓ To general-purpose register  $\checkmark$  To memory (address to MAR, result to MDR – Write) 6/11 K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT -1

- During the execution, PC is incremented to the next instruction

## Interrupt

- Normal execution of programs may be preempted if some device requires urgent servicing.

- The normal execution of the current program must be interrupted the device raises an interrupt signal.

- Interrupt-service routine

- Current system information backup and restore (PC, general-purpose) registers, control information, specific information)

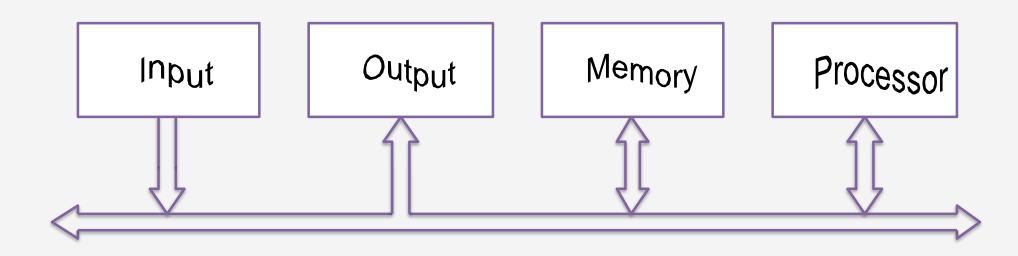

## **Bus Structures**

- There are many ways to connect different parts inside a computer together.

- A group of lines(wires) that serves as a connecting path for several ulletdevices is called a *bus*.

- Address/data/control

## Single-bus

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT -1

## Speed Issue

- Different devices have different transfer/operate speed.

- If the speed of bus is bounded by the slowest device connected to it, the efficiency will be very low.

- How to solve this?

- A common approach use buffer registers. e.g.- Printing the characters

Adv. of Buffers: Processor switches rapidly from one device to another.

## Identify the Images

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT -1

9/30/2023

## Thank You

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT -1