## **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (PO), Coimbatore – 641 107 Accredited by NAAC-UGC with 'A' Grade Approved by AICTE, Recognized by UGC & Affiliated to Anna University, Chennai

### **DEPARTMENT OF ECE**

**COURSE NAME: 19IT301 COMPUTER ORGANIZATION**

## **AND ARCHITECTURE**

**II YEAR/ III SEM**

## **Unit 1 : BASIC STRUCTURE OF COMPUTERS Topic 8:**

**Case study- RISC and CISC Architecture**

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT - 1

9/30/2023

- Instruction set or instruction set architecture(ISA) is the structure of the lacksquarecomputer that provides commands to guide the computer for processing data manipulation.

- Instruction set consists of

- ✓ instructions

- ✓ addressing modes

- $\checkmark$  registers

- ✓ interrupt

- $\checkmark$  exception handling

- ✓ memory architecture

### Instruction set of Processor

## RISC

**RISC or Reduced Instruction Set Computer** is a type of microprocessor architecture that utilizes a small, highly-optimized set of instructions for processing computations.

- It is also called as LOAD/STORE architecture lacksquare Divides instruction into memory access and **ALU** operations

- The IBM was the first company to define the ulletRISC architecture in the 1970s.

- This research was further developed by the universities • of Berkeley and Stanford to give basic architectural models.

A Sun UltraSPARC, a RISC microprocessor

# Characteristic/features of RISC processors

- Low number of clock cycles per instruction (CPI)

- Large number of registers(32 or more)

- Instruction pipeline

- Simple addressing modes

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT - 1

instruction (CPI) more)

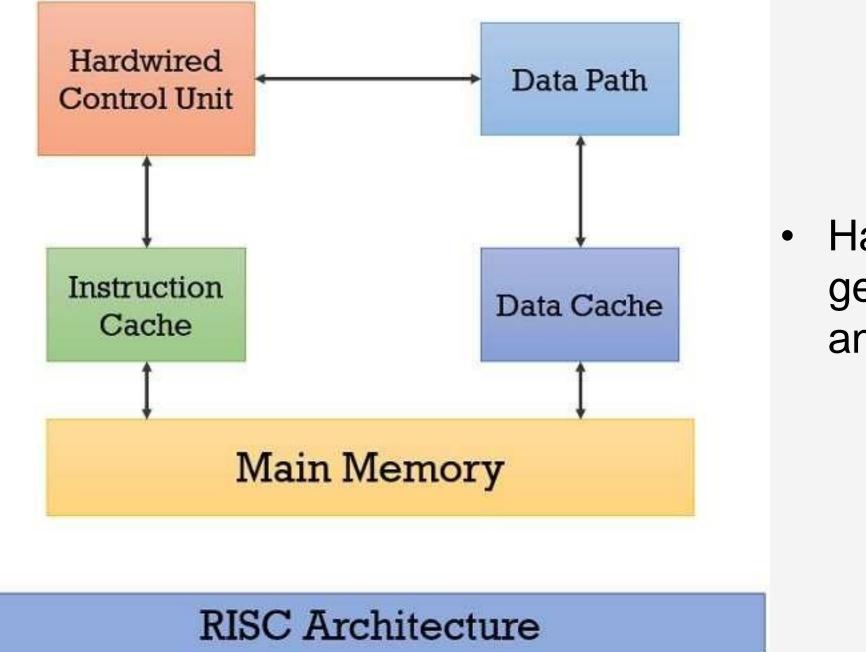

# **RISC** Processor Architecture

### Examples: MIPS, PowerPC, SUN SPARC, Alpha, RISC-V, ARM(Advanced RISC Machine)

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT - 1

9/30/2023

### Hardwired is a circuitry approach generates the control signals to fetch and execute instructions.

# Advantages of RISC Processor

- **RISC** instructions are simpler machine instruction

- RISC instructions are hardwired to fasten the execution

- Very less number of instruction formats (less than four), a few number of instructions (around 150) and a few addressing modes (less than four) are needed

- **Register based instructions**

- Less design complexity

# Disadvantages of RISC Processor

- The machine instructions are hardwired in RISC so, it would cost if any instruction needs modification

- RISC instructions do not allow direct memory to memory transfer, it requires Load and Store instructions to do so.

RISC instruction size is reduced but more instructions are required to

- RISC instruction size is reduced but more instructions are required to perform an operation

- CISC(Complex Instruction Set Computer) processor architecture completes the task by reducing the number of instructions in a program

- Since program/software is simplified, hardware is complex to perform complex tasks

CISC

## **Features of CISC Architecture**

- More number of predefined instructions which makes high lacksquarelevel languages easy to design and implement. Less number of registers and more number of addressing

- ulletmodes, generally 5 to 20.

- Takes varying cycle time for execution of instructions multi-clock cycles.

- Complex instruction set makes the pipelining technique lacksquaredifficult.

- CISC consists generally from 100 to 250 instructions lacksquare

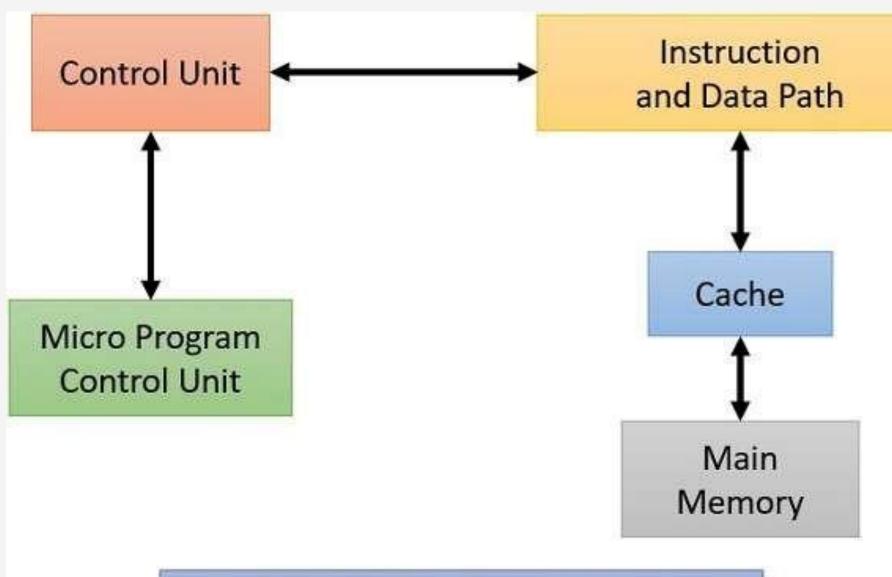

### **CISC** Architecture

Microprogram control unit uses a series of microinstructions of the microprogram(instructions are like small programs) and generate the control signals.

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT - 1

9/30/2023

## Example

### Examples of CISC Processors are:

### IBM 370/168, VAX 11/780, Intel 80486.

9/30/2023

## Advantages

- The code size is comparatively shorter which minimizes the memory requirement.

- Execution of a single instruction accomplishes several low-level tasks. lacksquare

- Complex addressing mode makes the memory access flexible.  ${\color{black}\bullet}$

- CISC instruction can directly access memory locations.

# Disadvantages of CISC

- Though the code size is minimized but it requires several clock cycles to execute a single instruction

- The hardware structure needs to be more complex to simplify software implementation.

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT - 1

# **RISC vs CISC**

- To perform a complex task, multiple small instruction are used together in RISC, whereas only few instructions are required to do the same task using CISC – as it is capable of performing complex task

- CISC is typically used for computers while RISC is used for smart • phones, tablets and other electronic devices.

1. The computer architecture aimed at reducing the time of execution of instructions is \_\_\_\_\_ a) CISC b) RISC c) ISA

d) IANA

2. The RISC processor has a more complicated design than CISC. a) True b) False

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT - 1

## Assessment

- 3. Pipe-lining is a unique feature of \_\_\_\_\_ a) RISC b) CISC c) ISA d) IANA

- 4. Out of the following which is not a CISC machine. a) IBM 370/168 b) VAX 11/780 c) Intel 80486 d) Motorola A567

## Answers

1. b 2. b 3. a 4. d

9/30/2023

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT - 1

## Thank You

<mark>9/30/20</mark>23

K.Sangeetha/AP/ECE / SNSCE / III Sem / COA / UNIT - 1