# UNIT III PROCESSOR AND CONTRO UNIT

**Basic MIPS implementation**

# Recall the Prior Knowledge

2/12

K.SANGEETHA/ECE/SNSCE19IT301 / Basic MIPS implementation

11/4/2023

## Introduction

3/12

#### **CPU** performance factors

- Instruction count: Determined by ISA and compiler

- **CPI and Cycle time**: Determined by CPU hardware

#### **MIPS** implementations

- A simplified version

- A more realistic pipelined version

#### Simple Subset

Memory reference: lw, sw

Arithmetic/logical: add, sub, and, or, slt

Control transfer: beq, j

## Instruction Execution

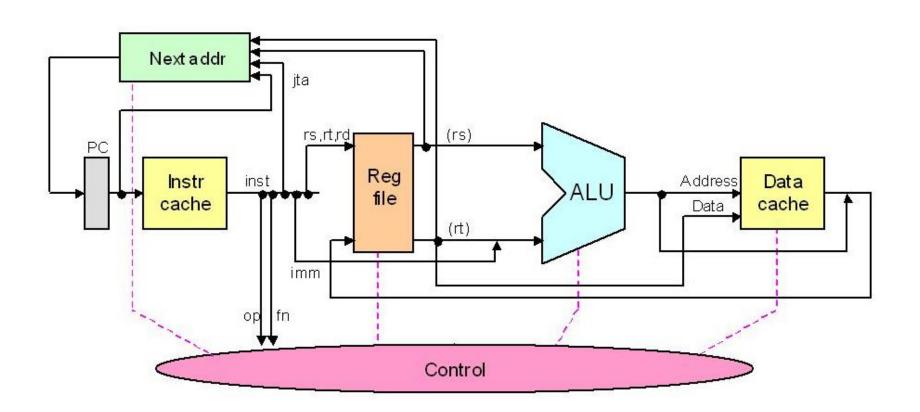

## **CPU Overview**

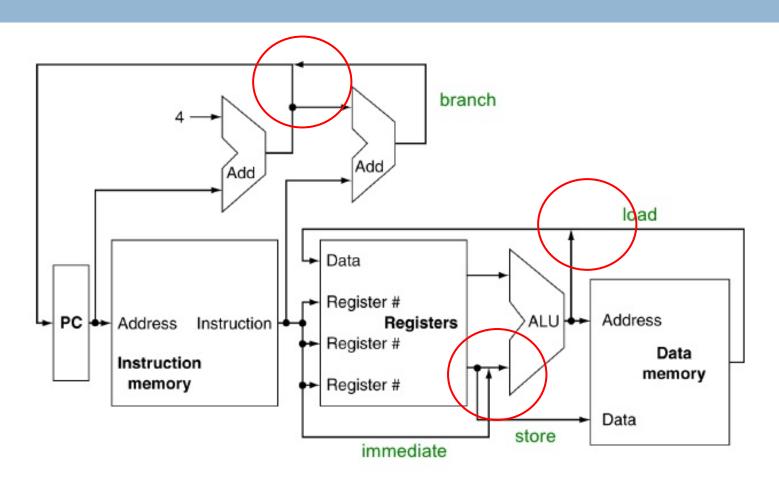

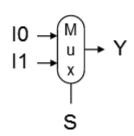

## **Multiplexers**

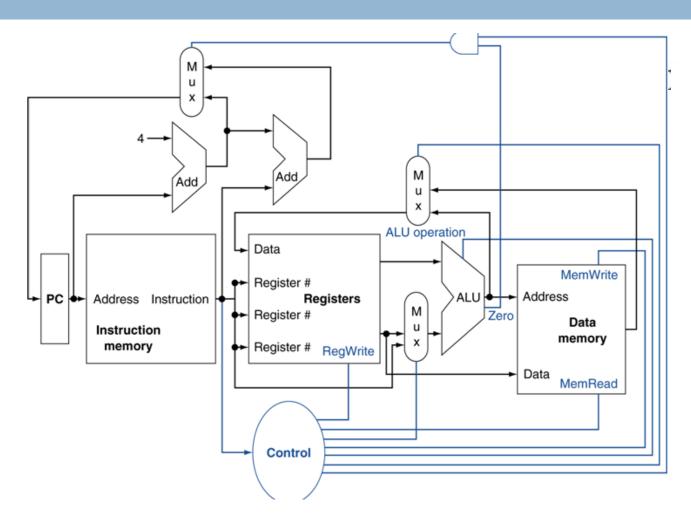

# **Control Signal**

## Logic Design Basics

- □ Information encoded in binary

- $\blacksquare$  Low voltage = 0, High voltage = 1

- One wire per bit

- Multi-bit data encoded on multi-wire buses

- Combinational element

- Operate on data

- Output is a function of input

- □ State (sequential) elements

- Store information

8/12

## **Combinational Elements**

AND-gate

- Multiplexer

- Y = S ? I1 : I0

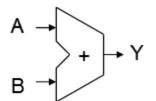

Adder

Addel

$$A = A + B$$

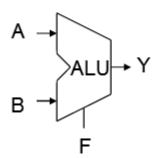

Arithmetic/Logic Unit

$$Y = F(A, B)$$

# Sequential Elements

- □ Register: stores data in a circuit

- Uses a clock signal to determine when to update the stored value

- Edge-triggered: update when Clk changes from 0 to 1

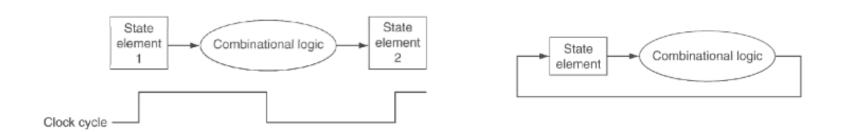

# Clocking Methodology

10/12

### Combinational logic transforms data during clock cycles

- Between clock edges

- Input from state elements, output to state element

- Longest delay determines clock period

11/12

# **Upcoming**

Instruction-1 Instruction-2 Instruction-3 Execution in Non-Pipelined Architecture

# **Upcoming**

12/12

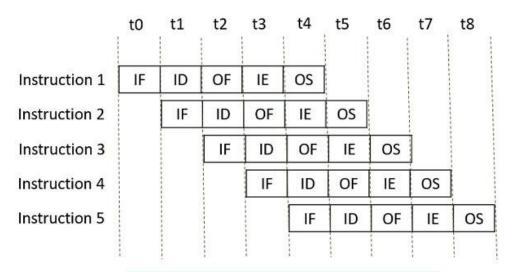

Pipelining of 5 Instructions