### **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

19EC306- DIGITAL ELECTRONICS

II YEAR/ III SEMESTER

1

UNIT 2 – COMBINATIONAL CIRCUITS

TOPIC - DECODER AND ENCODER

#### WHAT IS A DECODER?

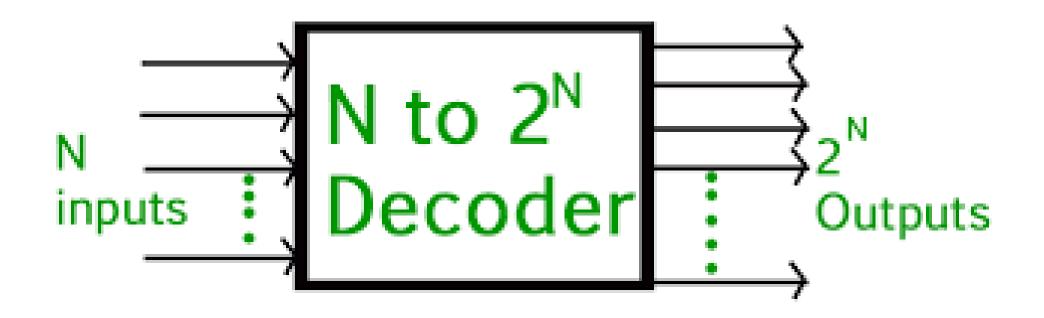

**▶Decoder** is a combinational logic circuit that converts binary information from the n coded inputs to a maximum of 2<sup>n</sup> unique outputs.

#### **DECODER**

#### A decoder has

- *n* inputs

- 2<sup>n</sup> outputs

- A decoder selects one of 2<sup>n</sup> outputs by decoding the binary value on the *n* inputs.

- The decoder generates all of the minterms of the *n* input variables.

- Exactly one output will be active for each combination of the inputs.

What does "active" mean?

#### **DECODER**

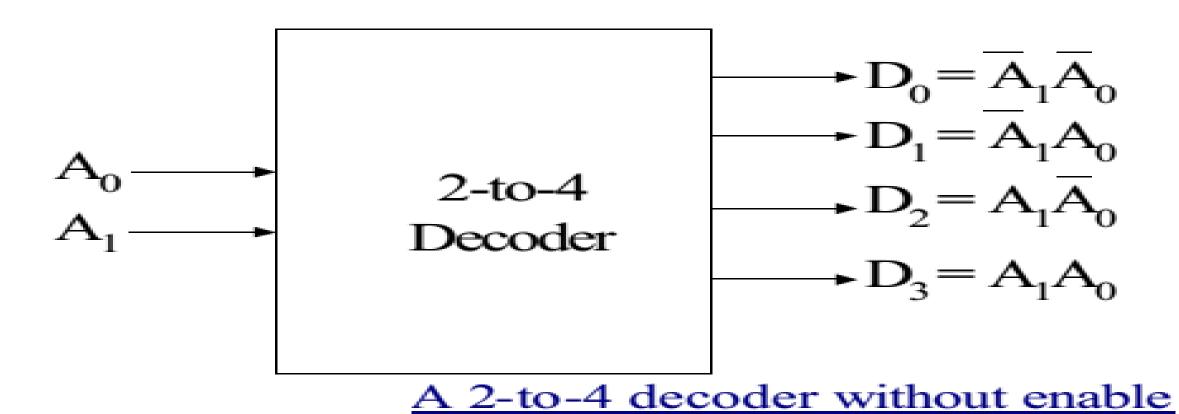

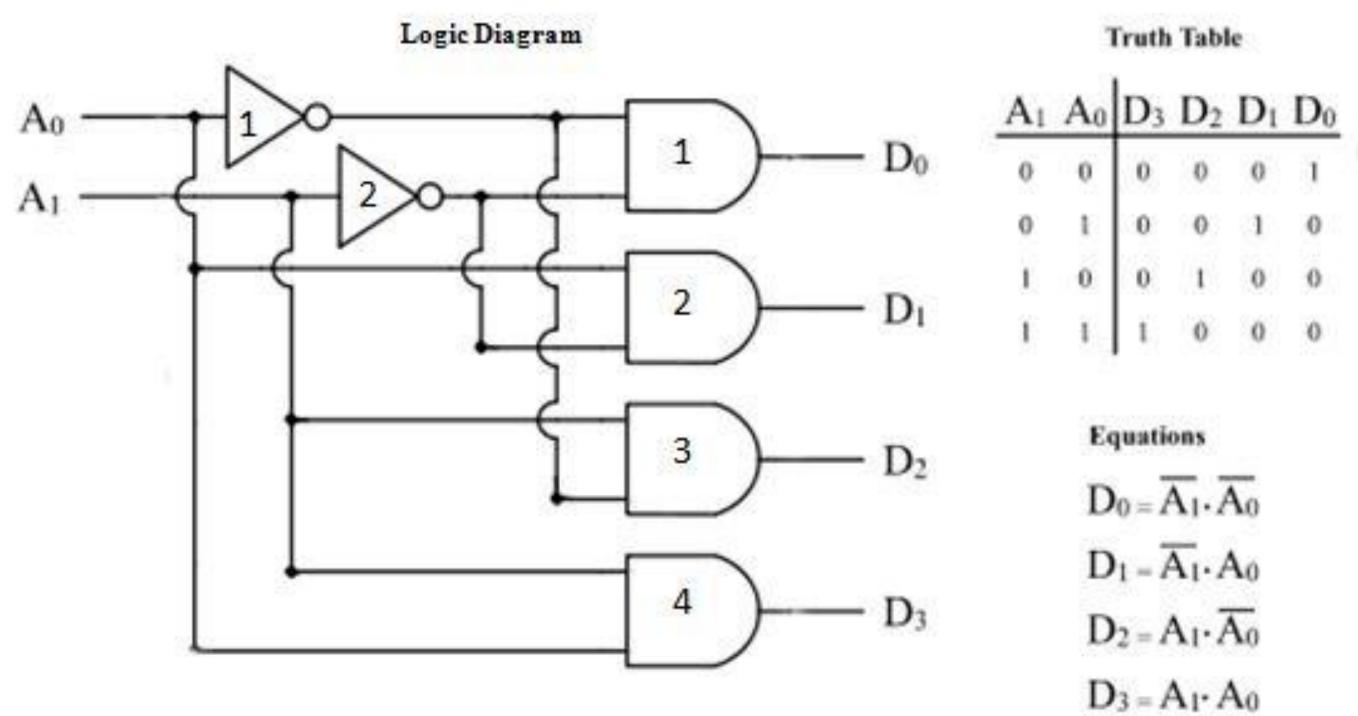

| Decimal # | Input |       | Output         |                |                |                |  |

|-----------|-------|-------|----------------|----------------|----------------|----------------|--|

|           | $A_1$ | $A_0$ | $\mathbf{D_0}$ | $\mathbf{D_1}$ | $\mathbf{D_2}$ | $\mathbf{D_3}$ |  |

| 0         | 0     | 0     | 1              | 0              | 0              | 0              |  |

| 1         | 0     | 1     | 0              | 1              | 0              | 0              |  |

| 2         | 1     | 0     | 0              | 0              | 1              | 0              |  |

| 3         | 1     | 1     | 0              | 0              | 0              | 1              |  |

Truth table for 2-to-4 decoder

#### **DECODER**

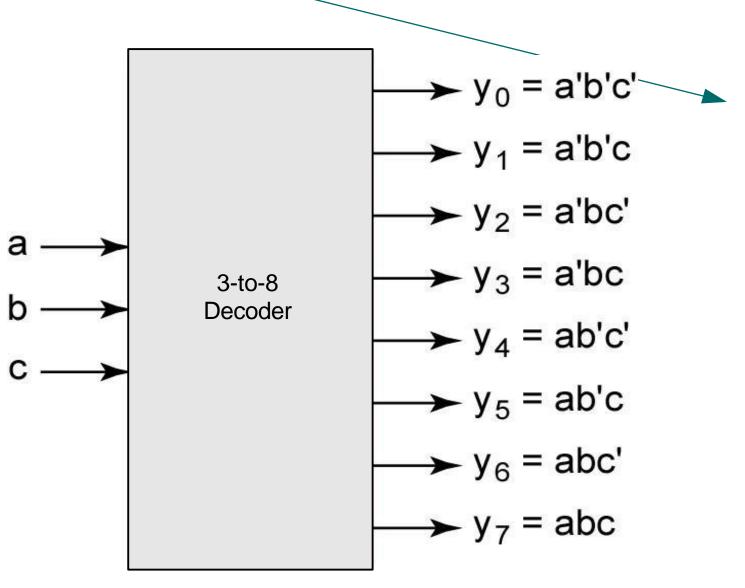

#### **DECODERS**

| a | b | С | <i>y</i> <sub>0</sub> | <i>y</i> <sub>1</sub> | <i>y</i> <sub>2</sub> | <i>y</i> <sub>3</sub> | <i>y</i> <sub>4</sub> | <i>y</i> <sub>5</sub> | <i>y</i> <sub>6</sub> | <i>y</i> <sub>7</sub> |

|---|---|---|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0 | 0 | 0 | 1                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |

| 0 | 0 | 1 | 0                     | 1                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |

| 0 | 1 | 0 | 0                     | 0                     | 1                     | 0                     | 0                     | 0                     | 0                     | 0                     |

| 0 | 1 | 1 | 0                     | 0                     | 0                     | 1                     | 0                     | 0                     | 0                     | 0                     |

| 1 | 0 | 0 | 0                     | 0                     | 0                     | 0                     | 1                     | 0                     | 0                     | 0                     |

| 1 | 0 | 1 | 0                     | 0                     | 0                     | 0                     | 0                     | 1                     | 0                     | 0                     |

| 1 | 1 | 0 | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 1                     | 0                     |

| 1 | 1 | 1 | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 1                     |

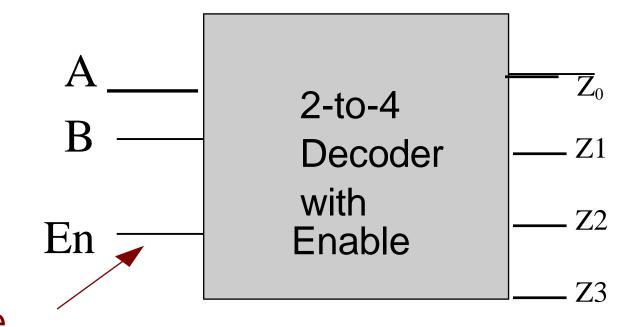

### Decoder with Enable

### active-high enable

En

0

A

X

B

X

| 1 | 0 | 0 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

0

$\mathbf{Z}_0$

$\mathbf{Z}_1$

0

$\mathbb{Z}_2$

0

$\mathbb{Z}_3$

0

enabled

disabled

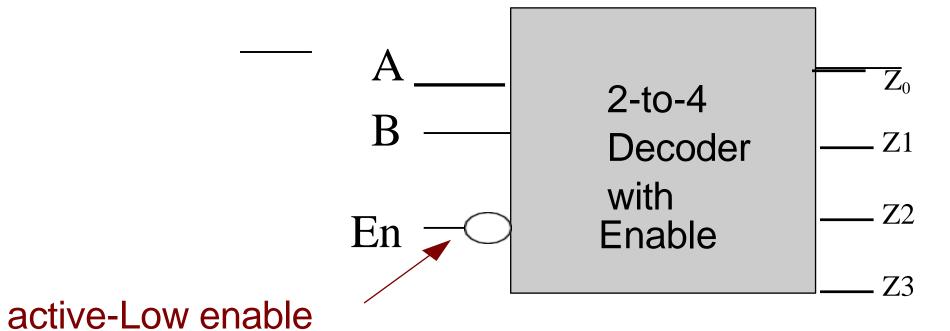

### Decoder with Enable

enabled

disabled

| En | A | В | $\mathbf{Z}_0$ | $\mathbf{Z}_1$ | ${f Z}_2$ | $\mathbb{Z}_3$ |

|----|---|---|----------------|----------------|-----------|----------------|

| 0  | 0 | 0 | <sub>8</sub> 1 | 0              | 0         | 0              |

| 0  | 0 | 1 | 0              | 1              | 0         | 0              |

| 0  | 1 | 0 | 0              | 0              | 1         | 0              |

| 0  | 1 | 1 | 0              | 0              | 0         | 1              |

| 1  | X | X | 0              | 0              | 0         | 0              |

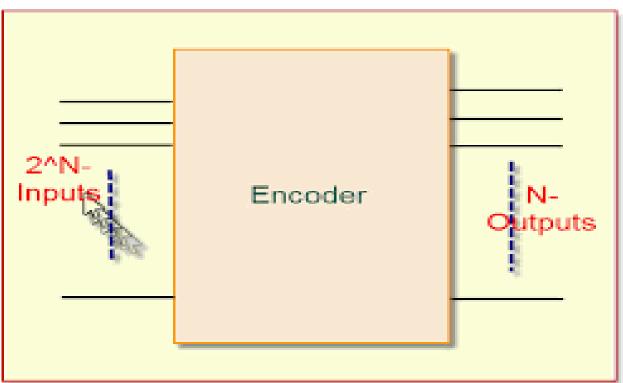

#### WHY ENCODERS?

#### An encoder has

- 2<sup>n</sup> inputs

- *n* outputs

Outputs the binary value of the selected (or active) input.

Performs the inverse operation of a decoder. Issues

- What if more than one input is active?

- What if no inputs are active?

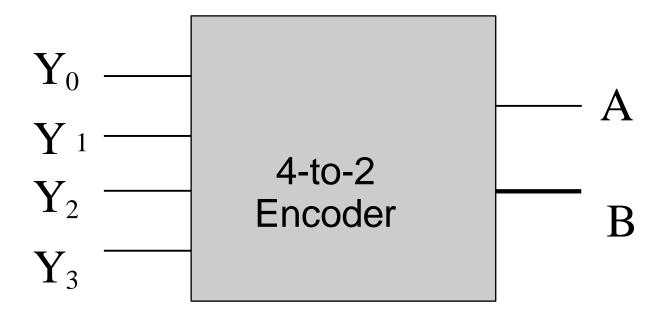

# **Encoders**

| $\mathbf{Y}_{0}$ | $\mathbf{Y}_1$ | $\mathbf{Y}_2$ | $\mathbf{Y}_3$ | A | В |

|------------------|----------------|----------------|----------------|---|---|

| 1                | 0              | 0 10           | 0              | 0 | 0 |

| 0                | 1              | 0              | 0              | 0 | 1 |

| 0                | 0              | 1              | 0              | 1 | 0 |

| 0                | 0              | 0              | 1              | 1 | 1 |

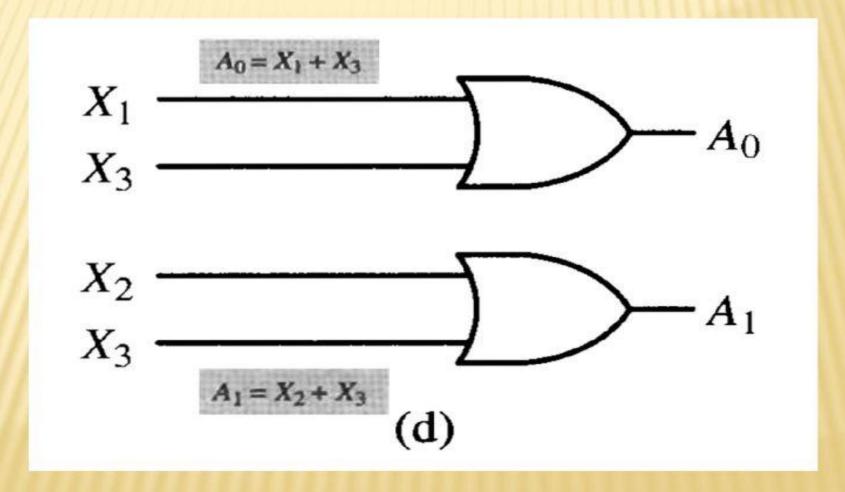

# **Encoders**

# 4 TO 2 LINE ENCODER

#### Logic diagram

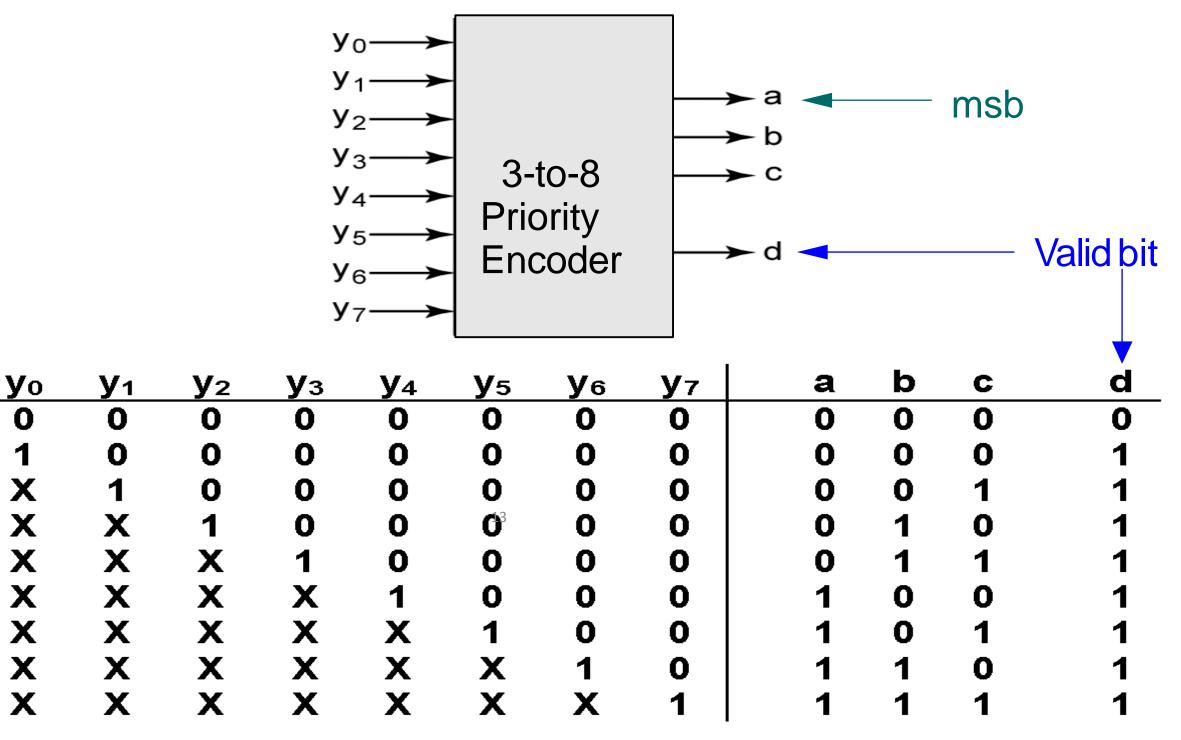

# **Priority Encoders**

- If more than one input is active, the higher-order input has priority over the lower-order input.

- The higher value is encoded on the output

A valid indicator, d, is included to indicate whether or not the output is valid.

- Output is invalid when no inputs are active

•

$$d = 0$$

- Output is valid when at least one input is active

•

$$d = 1$$

# **Priority Encoders**

EE203 - Linear and Digital Circuits

Dr.B.Sivasankari, ASP/ECE

### Using an *n*-output Decoder

n-output decoder to realize a logic circuit for a function with n''

- minterms.

- Each minterm of the function can be mapped to an output of the decoder.

- For each row in the truth table, for the function, where the output is 1, sum (or "OR") the corresponding outputs of the decoder.

L4

That is, for each minterm in the minterm expansion of the function, OR the corresponding outputs of the decoder.

Leave remaining outputs of the decoder unconnected.

# Using an *n*-output Decoder

#### Example

- Using a 3-to-8 decoder, design a logic circuit to realize the following Boolean function

- F(A,B,C) = 2m(2,3,5,6,7)

# Using an *n*-output Decoder

#### **Example**

Using a 2-to-2 decoder, design a logic circuit to realize the following Boolean function

16

$$F(A,B,C) = \Sigma m(0, 1, 4, 6, 7)$$

### **ASSESSMENT**

- 1. What is a Encoder?

- 2. Device which converts an input device state into a binary representation of ones or zeros is termed as

17

- 1. Encoder

- 2. Decoder

- 3. Multiplexer

- 4. Data selector

- 3. A decoder converts n inputs to \_\_\_\_\_ outputs.(2<sup>n</sup>)

- 4. ----- are building blocks of encoders.(Ans OR gate)

- 5. Draw the block diagram of 2x4 decoder.

### **THANK YOU**